# Concept de grille quasi-flottante pour la protection d'un MOSFET SiC et la surveillance de l'intégrité de son oxyde basé sur une architecture de driver à résistances de grilles commutées.

M. Picot-Digoix <sup>(1,2)</sup>, F. Richardeau <sup>(1)</sup>, W. Jouha <sup>(1)</sup>, J-M. Blaquier <sup>(1)</sup>, S. Vinnac <sup>(1)</sup>, S. Azzopardi <sup>(2)</sup>, T-L. Le <sup>(2)</sup>

<sup>(1)</sup> LAPLACE, Université de Toulouse, CNRS, INPT, UPS, Toulouse – <sup>(2)</sup> SAFRAN TECH, Paris Saclay

**RESUME** – La protection efficace sur courts-circuits du MOSFET SiC tout comme la surveillance de l'intégrité de son oxyde reste un enjeu de premier plan dans l'usage de ces composants. Dans cet article, une architecture parallèle originale de gate driver à résistances de grille commutées permettant de concilier dynamique en commutation et détection de divers défauts est présentée. Cette méthode met à profit les variations de charge de grille apparaissant en régimes de défaut, en isolant partiellement la grille entre l'amorçage et le blocage afin de la rendre plus sensible aux signatures électriques de défauts. L'architecture de commande est caractérisée et validée sur banc de test avec des MOSFETs SiC de calibre 1200V-36A.

**Mots-clés** – MOSFET SiC, court-circuit, gate driver, fiabilité.

## 1. INTRODUCTION

Le MOSFET SiC s'est imposé comme composant de choix dans les convertisseurs de moyenne et de forte puissance. Cependant, son déploiement dans les applicatifs à haute exigence de fiabilité, comme l'aéronautique, reste limité par un manque de robustesse, notamment sur la durée de tenue aux courts-circuits (CC), et la fragilité de la région d'oxyde de grille. Les méthodes de protection contre les courts-circuits actuelles reposent essentiellement sur une surveillance de la tension drain-source ou bien du courant de drain. Ces méthodes sont relativement invasives et coûteuses dans le sens où elles requièrent l'utilisation d'une large diode haute tension de désaturation [1], non-intégrable sur circuit intégré, ou encore d'un capteur de courant sur puce spéciale encore aujourd'hui non standardisée sur SiC à la différence de la technologie Si, notamment dans l'industrie automobile.

Il existe aujourd'hui plusieurs propositions d'architectures de gate driver à voies parallélisées. Leur fonction reste cependant majoritairement circonscrite à de l'optimisation de vitesse de commutation en  $dV/dt$  et/ou en  $dI/dt$  par adaptation dynamique de la résistance de grille selon le régime de fonctionnement [2] ou par compensation des dérives des performances du transistor dues à son vieillissement [3].

L'architecture de gate driver proposée [4] et présentée en [5] permet une protection à la fois multifonctionnelle et exhaustive contre tous types de CC (type 1 [6], type 2 interne et type 2 externe [7]), contre des surintensités modérées (fonction *Over Current Protection*), ainsi qu'une détection de dégradation irréversible de l'oxyde de grille (fonction *Gate Oxide Damage*), le tout sans entraver le fonctionnement nominal du bras d'onduleur. De plus, elle repose sur la surveillance d'un observable du côté de la grille, donc basse tension, ce qui la rend réalisable en circuit intégré. La parallélisation peut être implémentée d'autant plus facilement avec des buffers standards du commerce puisqu'aucun isolement galvanique supplémentaire n'est requis : deux alimentations positive ( $V_{DD}$ ) et négative ( $V_{SS}$ ) partagées entre les différents buffers suffisent.

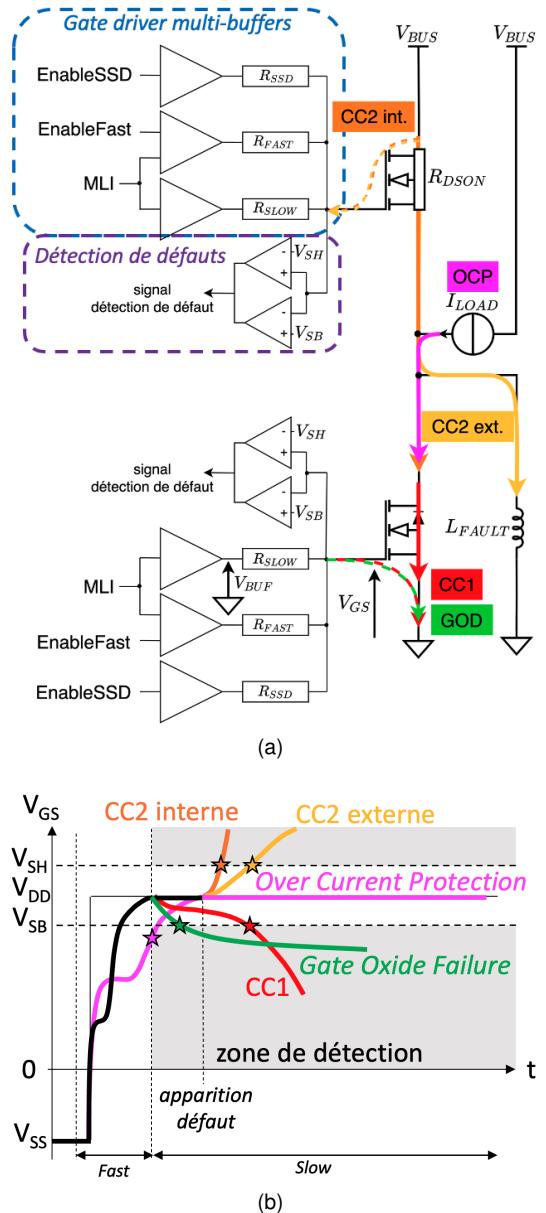

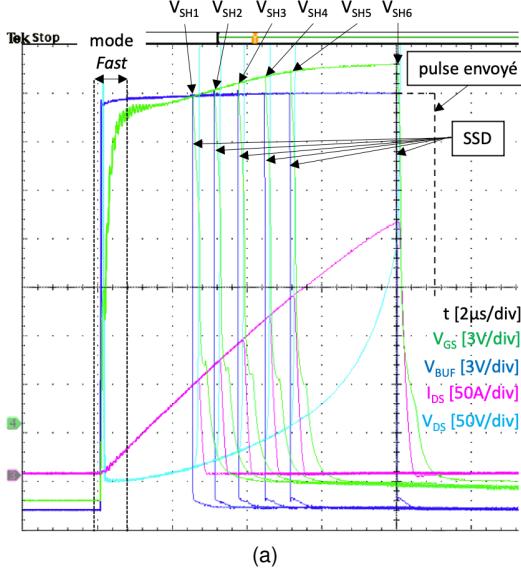

FIG. 1. Illustration de plusieurs types de défauts dans un bras d'onduleur disposant d'une architecture de gate driver parallèle à résistances de grille commutées (a), signatures respectives des défauts sur  $V_{GS}$  considérés dans cette étude (b)

## 2. MISE EN ŒUVRE DU CONCEPT

### 2.1. Présentation du driver à résistances de grille commutées

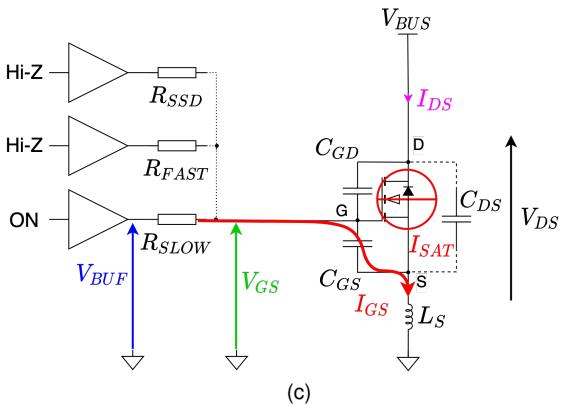

La méthode de protection proposée repose sur une redéfinition du rôle du circuit de grille : habituellement uniquement considéré comme un élément de contrôle permettant de gérer les dynamiques en commutation, il est ici amené à également assurer une fonction de surveillance de possibles défauts. Le concept consiste à isoler partiellement la grille via une forte résistance de grille entre l'amorçage et le blocage afin de la rendre plus sensible à de possibles variations modérées de charge de grille identifiées comme des signatures électriques en CC. Une telle valeur de résistance de grille n'étant pas viable lors des phases de commutation, une architecture de gate driver multi-voies parallèles à résistances de grille commutées conciliant dynamique en commutation et surveillance de défauts sous grille quasi-flottante (Fig. 1a) est caractérisée ci-après. Le besoin de forte dynamique étant confiné autour des instants de commutation, le buffer *Fast* à faible résistance de grille est uniquement activé autour des fronts d'amorçage et de blocage (Fig. 1b). Les durées d'activation *EnableFast* doivent permettre des charges et décharges complètes de grille, et en configuration bras d'onduleur, protéger le MOSFET complémentaire contre les remontées de charge par effet Miller lors des phases de dv/dt. Le reste du temps, le buffer *Fast* est placé en haute impédance (Hi-Z) pour laisser place au buffer *Slow* en parallèle à forte résistance de grille afin d'exacerber les possibles signatures de défaut sur la tension grille-source  $V_{GS}$  et de faciliter leur détection.

### 2.2. Méthode de détection de défauts

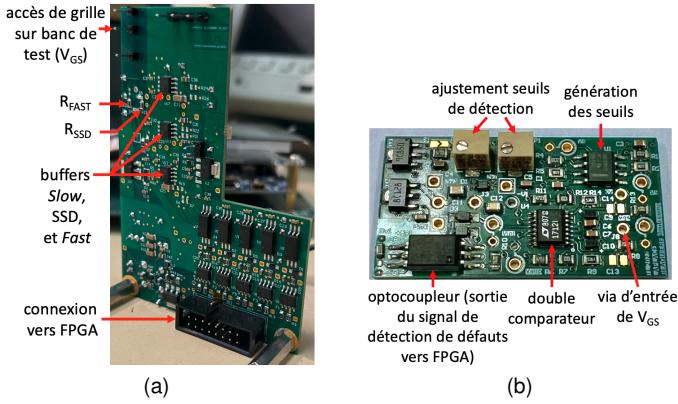

La méthode de détection de défauts proposée consiste en un double seuillage de  $V_{GS}$  autour de sa valeur nominale entre l'amorçage et le blocage.  $V_{GS}$  est comparée à des références haute ( $V_{SH}$ ) et basse ( $V_{SB}$ ) (Fig. 1b), et le résultat de la comparaison est envoyé via une liaison isolée à un organe de contrôle numérique (cf. Fig. 2b) gérant le blocage du MOSFET à l'aide du buffer *Soft Shut-Down* (SSD) comme illustré en Fig. 1a.

FIG. 2. Carte gate-driver multi-buffers (a), carte de détection de défauts à doubles seuils (b)

## 3. RÉSULTATS EXPÉRIMENTAUX

Afin de valider l'architecture de driver proposée et la méthode de détection à double seuils, des essais de protection sous différents défauts ont été conduits sur un bras d'onduleur à base de MOSFETs SiC 1200V-36A-80mΩ du commerce en boîtier TO-247 à 3 broches (sans source Kelvin) sous une tension de bus  $V_{BUS}$  de 600V. Il est à noter que l'utilisation d'une résistance  $R_{FAST}$  de relativement forte valeur (47Ω) dans les essais expérimentaux qui suivent permet de limiter les perturbations dues aux éléments parasites du banc de tests. En pratique, de plus faibles valeurs sont recommandées par les fournisseurs.

### 3.1. Robustesse et non-détection en fonctionnement nominal

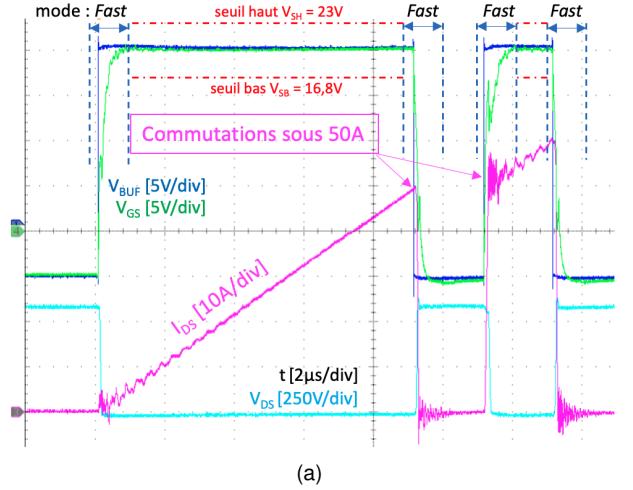

Avant de détailler les diverses fonctions de protection contre des défauts pouvant survenir dans un bras d'onduleur, il convient d'assurer l'absence d'influence du système de protection proposé sur le fonctionnement nominal du bras. Pour ce faire, des essais en double pulse ont été réalisés pour se rapprocher d'un fonctionnement nominal. Un courant de charge de 50A, soit 140% du calibre en courant du MOSFET SiC étudié a été choisi afin de se positionner dans le pire cas. Dans cette optique, une résistance  $R_{SLOW} = 10k\Omega$  est également choisie pour placer la grille dans un état de haute sensibilité lors des phases de conduction.

(a)

(b)

FIG. 3. Formes d'ondes en essai double pulse sous un courant de charge de 50A ( $V_{BUS} = 600V$ ,  $V_{DD} = 20V$ ,  $V_{SS} = -5V$ ,  $R_{FAST} = 47\Omega$ ,  $R_{SLOW} = 10k\Omega$ ,  $L = 108\mu H$ ) (a), schéma équivalent de l'essai en double pulse avec une diode Schottky SiC de roue libre (b)

Comme illustré en Fig. 3a, la tension de grille n'est pas impactée en fonctionnement nominal et suit correctement les ordres de commande. Cela valide la robustesse de l'architecture proposée face à de fausses détections en régime nominal.

### 3.2. Court-circuit de type 1 (CC1)

Le CC1 se caractérisant par une montée en courant de drain à forte dynamique jusqu'à saturation sous la pleine tension de bus, il se traduit par une intense dissipation de puissance localisée dans la puce. L'échauffement résultant donne naissance à un courant  $I_{SE}$  défini en (1) à travers l'oxyde de grille vers la source par émission Schottky d'électrons chauds.

$$I_{SE} = A_0 \frac{4\pi q k^2 m_{ox}}{h^3} T^2 \cdot \exp \left( \frac{-\Phi_B + \sqrt{\frac{q^3 E}{4\pi\epsilon_r\epsilon_0}}}{kT} \right) \quad (1)$$

Avec  $T$  la température, et  $A_0$  la surface active de la puce. Les autres paramètres sont définis dans [8].

(a)

(b)

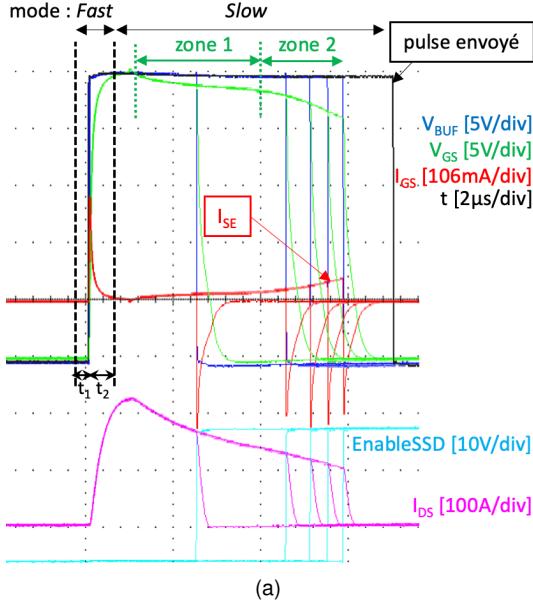

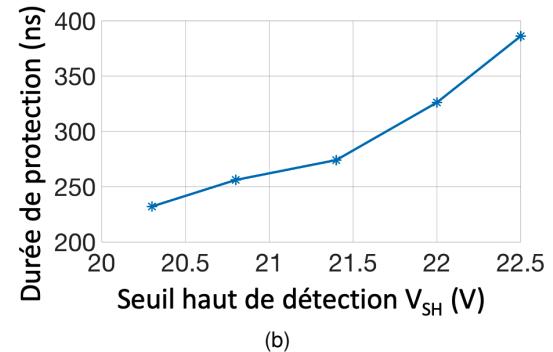

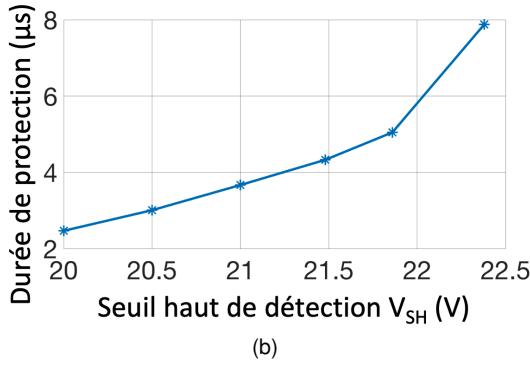

FIG. 4. Formes d'ondes de grille en CC1 pour différentes valeurs de seuils bas de détection  $V_{SB}$  ( $V_{BUS} = 600V$ ,  $R_{FAST} = 47\Omega$ ,  $R_{SLOW} = 1k\Omega$ ,  $R_{SSD} = 82\Omega$ ,  $V_{DD} = 20V$ ,  $V_{SS} = -5V$ ,  $t_1 = 50ns$ ,  $t_2 = 830ns$ ) (a), résultats paramétriques en durée de protection (b), schéma équivalent (c)

Ce courant engendre une chute de tension aux bornes de la résistance de grille ( $R_{SLOW}$  ici), provoquant ainsi une baisse naturelle de  $V_{GS}$  (Fig. 1a en rouge) comme décrit par éq. (2). Cette baisse est rendue détectable par comparaison à un seuil bas ( $V_{SB}$ ) de référence.  $R_{SLOW}$  joue ici un rôle d'amplification de la signature du CC1.

$$V_{GS_{CC1}} = V_{DD} - R_{SLOW}I_{SE} - L_S \frac{dI_{DS}}{dt} \Big|_{CC1} \quad (2)$$

Comme illustré en Fig. 4a, la fuite de courant par effet

Schottky étant un phénomène d'origine thermique, donc intrinsèquement lent, se manifeste de manière tardive (Fig. 4a zone 2) par rapport au front d'amorçage signifiant l'apparition du défaut, le tout malgré l'effet quadratique de la température sur cette fuite (cf. éq. (1)). Cependant,  $V_{GS}$  commence à chuter avant même l'échauffement de la puce, dès la fin de l'amorçage en mode *Fast*. Cela est dû à un effet inductif lié à la présence de l'inductance de la connectique de source  $L_S$  de la puce dans le boîtier TO-247. En effet, à haute température la mobilité des électrons dans le canal diminue, ce qui réduit le gain du MOSFET SiC. Il s'ensuit alors une diminution du courant de saturation et donc un  $dI_{DS}/dt$  négatif. Ce  $di/dt$  apparaissant juste après le sommet de la forme en cloche de  $I_{DS}$  (Fig. 4a) excite  $L_S$  et provoque un appel de charges de la grille vers la source à travers  $C_{GS}$ . Ce phénomène inductif, traditionnellement considéré comme effet parasite, est ici avantageux car il permet d'abaisser  $V_{GS}$  au plus tôt (Fig. 4a zone 1) et d'accélérer son intersection avec le seuil de détection bas  $V_{SB}$ . Cela autorise *in fine* une détection plus rapide du défaut.

Il apparaît que rapprocher le seuil  $V_{SB}$  de la tension nominale  $V_{DD}$  (20V ici) rend l'intersection avec  $V_{GS}$  plus proche dans le temps, ce qui permet une détection effectivement plus rapide. Néanmoins, cela rend le système plus susceptible de générer de fausses détections. Un compromis entre vitesse de protection et robustesse du système de détection selon la valeur du seuil bas de détection est ainsi mis en évidence. D'après les relevés paramétriques en Fig. 4b, augmenter  $R_{SLOW}$  permet de rompre ce compromis en abaissant davantage  $V_{GS}$ , et d'obtenir une détection rapide et robuste. Une protection effective contre CC1 est obtenue en 1,2μs (Fig. 4b) soit seulement 15% du temps de tenue en court-circuit de 8μs [9] du MOSFET SiC testé. Rappelons qu'une détection rapide et un gage d'une durée de vie sur courts-circuits répétés [10].

### 3.3. Court-circuit de type 2 (CC2)

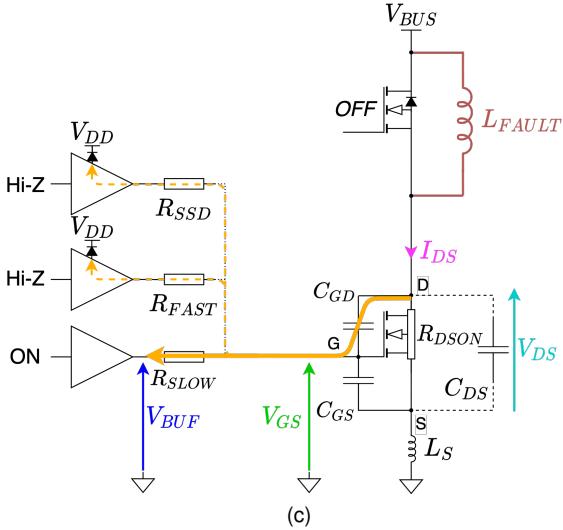

Lors d'un fonctionnement en bras d'onduleur, un défaut peut surgir sur la charge connectée au point milieu. Ce type de défaut est appelé CC2 externe. Il peut résulter d'un défaut d'isolement d'enroulements moteurs par exemple. Ce dysfonctionnement crée un chemin inductif de défaut ( $L_{FAULT}$ ) entraînant une montée en courant à travers un MOSFET initialement à l'état passant (Fig. 1a en jaune) jusqu'à atteindre la saturation. De nature inductive, ce courant est de faible dynamique et rend la détection de CC2 d'autant plus délicate. Tant que le transistor est en zone ohmique, le  $di/dt$  modéré se traduit à travers  $R_{DS(on)}$  par un  $dV_{DS}/dt$  aux bornes du MOSFET. Ce phénomène engendre, par couplage capacitif via  $C_{GD}$ , une remontée de charges du drain vers la grille. Ce couplage est d'autant plus fort car  $C_{GD}$  présente une valeur maximale à faible  $V_{DS}$  ce qui favorise l'injection de charges vers la grille. Ce courant capacitif traverse  $R_{SLOW}$  et participe à augmenter  $V_{GS}$  (Fig. 5a) comme décrit par éq. (3).

$$V_{GS_{CC2ext}} = V_{DD} + R_{SLOW}C_{GD}(V_{DS}) \frac{dV_{DS}}{dt} \quad (3)$$

La détection de ce type de défaut est réalisée grâce à l'intersection de  $V_{GS}$  avec un seuil haut ( $V_{SH}$ ). La contribution du couplage inductif via  $L_S$  est ici négligeable du fait du faible  $di/dt$  d'excitation.

Quand le MOSFET atteint la saturation, apparaît alors un fort  $dV_{DS}/dt$  jusqu'à la tension de bus. Ce fort terme excitatoire sollicite  $C_{GD}$  et renvoie des charges vers la grille par le même processus que celui décrit précédemment. Ce fort  $dv/dt$  compense le fait que  $C_{GD}$  présente maintenant une faible valeur ( $V_{DS} \approx V_{BUS}$ ). Une fois la saturation atteinte, un courant de saturation traverse le canal du transistor sous la pleine tension de bus. Le composant subit alors une forte dissipation de puissance et donc un échauffement. Ce phénomène n'est pas sans rappeler les caractéristiques du CC1. En effet, un CC2 externe non

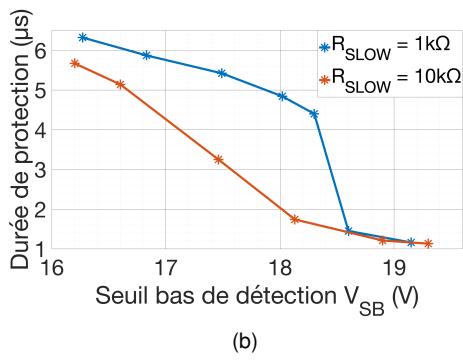

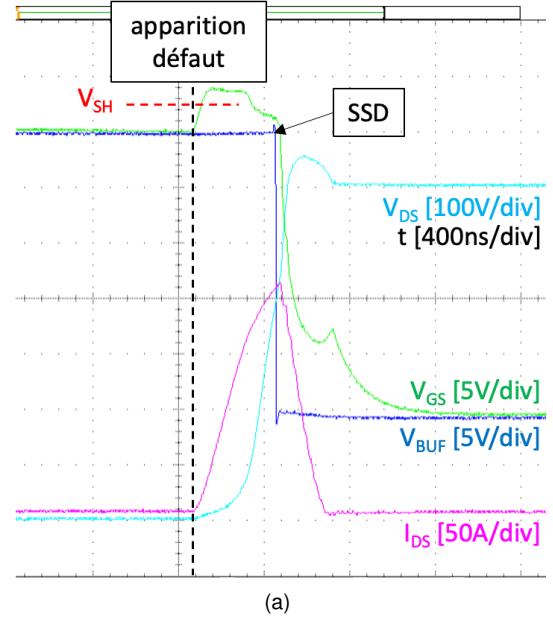

FIG. 6. Formes d'ondes de grille en CC2 interne ( $V_{BUS} = 600V$ ,  $R_{FAST} = 47\Omega$ ,  $R_{SLOW} = 1k\Omega$ ,  $R_{SSD} = 82\Omega$ ,  $V_{DD} = 20V$ ,  $V_{SS} = -5V$ ,  $20V < V_{SH} < 22.4V$ ,  $L_{FAULT} = 11.6\mu H$ ) (a), résultats en durée de protection (b), schéma équivalent (c)

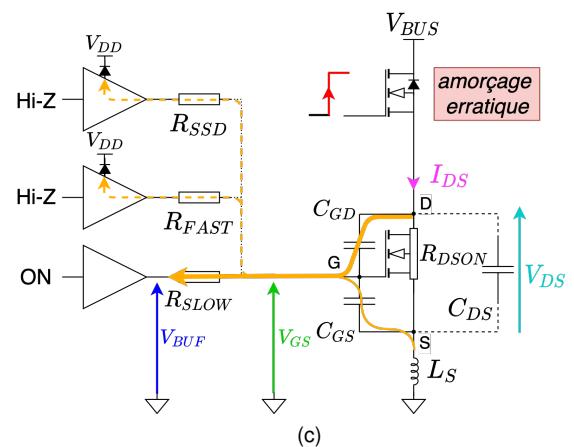

à « ET » logique afin d'éviter de fausses détections suite à un possible déclenchement erratique.

Une protection effective contre CC2 externe est obtenue en  $2.5\mu s$  (Fig. 5b). La durée de protection dépend toutefois fortement du  $dI/dt$  de défaut.

Dans le cas où la montée en courant de défaut est causée non plus par un élément inductif externe mais par un défaut interne au bras d'onduleur (remise en conduction erratique du transistor complémentaire [7] par exemple), on parle alors de CC2 interne (Fig. 1a en orange). Ce type de défaut se caractérise par

détecté lors de la phase montante du courant laissera place à un comportement de type CC1.

Cette propriété permet alors une double détection : une par seuil haut sur  $V_{GS}$  lors de la phase de  $dI/dt$  positif, et une par seuil bas une fois la saturation atteinte comme décrit pour le CC1 (cf. paragraphe 3.1). Sur ce principe, la méthode de détection proposée permet une redondance dans le cas d'un dysfonctionnement de la détection à seuil haut, ou bien une validation

une montée en courant très dynamique, à présent seulement limitée par l'inductance parasite de la maille de commutation et la dynamique d'amorçage du transistor provoquant la montée en courant. Les phénomènes apparaissant en CC2 interne sont identiques à ceux décrits en CC2 externe, la seule différence résidant dans la dynamique de montée en courant. Cela a pour effet de rendre le couplage inductif avec  $L_S$  considérable (cf. éq. (4)).

$$\delta V_{GS_{CC2int}} = (R_{SLOW}C_{GD_{MAX}}R_{DS_{ON}} + L_S) \frac{dI_{DS}}{dt} \quad (4)$$

La surtension observée sur  $V_{GS}$  est écrêtée par les buffers étant en haute impédance pendant la phase de conduction (buffers *Fast* et *SSD*). En effet, les buffers utilisés étant en configuration *push-pull*, les diodes *body* de leur transistor PMOS (*P-type Metal-Oxide-Semiconductor*) *high-side* permettent d'évacuer les remontées de courant vers les condensateurs de découplage sur  $V_{DD}$  (Fig. 6c). Cela a pour effet d'écrêter  $V_{GS}$  à  $V_{DD}$  à la tension de seuil des diodes près (environ 4V). Cette limitation permet de protéger naturellement la grille du MOSFET contre des excursions trop élevées de  $V_{GS}$ .

Une protection effective en CC de type 2 interne est obtenue en seulement 250ns (Fig. 6b).

#### 3.4. Complémentarité des protections *high-side* et *low-side*

Par ailleurs, dans le cas d'un CC de type 1 déclenché par un défaut de commande dans un bras d'onduleur, le courant résultant de l'amorçage erratique d'un MOSFET est subi par le transistor homologue initialement en phase de conduction (cf. Fig. 4a). Ce transistor complémentaire subit alors un CC2 interne provoqué par l'apparition du défaut CC1. La complémentarité des protections *high-side* et *low-side* rendent alors possible soit la détection d'un CC1 avec la même dynamique qu'un CC2 interne, en quelques centaines de nanosecondes, soit une redondance des protections pour éviter de fausses détections de CC1. Cette propriété à l'échelle du bras d'onduleur sera développée et illustrée dans une prochaine publication.

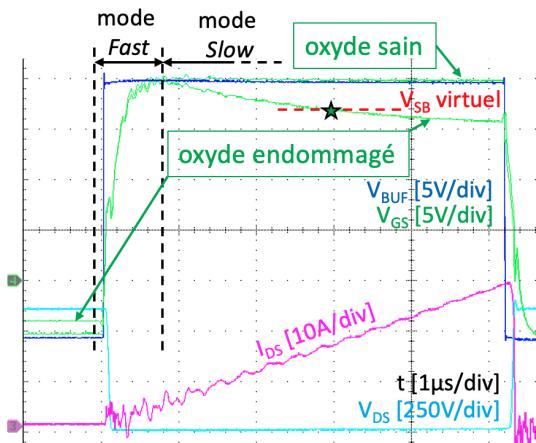

#### 3.5. Fonction Gate Oxide Damage (GOD)

Afin de pallier la baisse de mobilité du canal des MOSFETs SiC par rapport à leurs homologues en Si, leur couche d'oxyde de grille en  $\text{SiO}_2$  est réalisée beaucoup plus finement (typiquement 50nm) [11]. Cela a pour conséquence de rendre la région d'oxyde mécaniquement plus fragile et sensible.

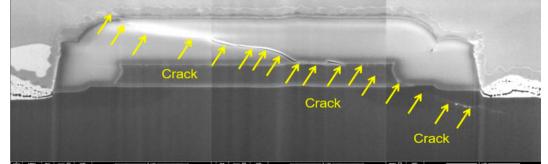

Sous stress thermomécaniques répétés, notamment en cas de CC, la région d'oxyde *Inter-Layer Dielectric* (ILD) du MOS-

FIG. 7. Visualisation de la fuite de grille d'un MOSFET à oxyde endommagé, comparaison avec un oxyde sain en essai double pulse ( $V_{BUS} = 600V$ ,  $R_{FAST} = 47\Omega$ ,  $R_{SLOW} = 1k\Omega$ ,  $V_{DD} = 20V$ ,  $V_{SS} = -5V$ )

FET SiC peut se fracturer (Fig. 8) et laisser place à des fuites de courant irréversibles entre grille et source [12]. Ces chemins de fuites conduisent alors à une baisse détectable de  $V_{GS}$  (Fig. 1 en vert et Fig. 7) à travers  $R_{SLOW}$ .

L'impact de ces fissures est d'ailleurs également visible lors de la phase OFF de la trame MLI : la tension de grille ne parvient plus à suivre la tension négative  $V_{SS}$  imposée par le buffer.

FIG. 8. Fissure diélectrique dans la zone ILD entre grille en polysilicium et contact de source en aluminium et dans la zone d'oxyde de grille observée au MEB sur le DUT dans [13]

#### 3.6. Fonction Over Current Protection (OCP)

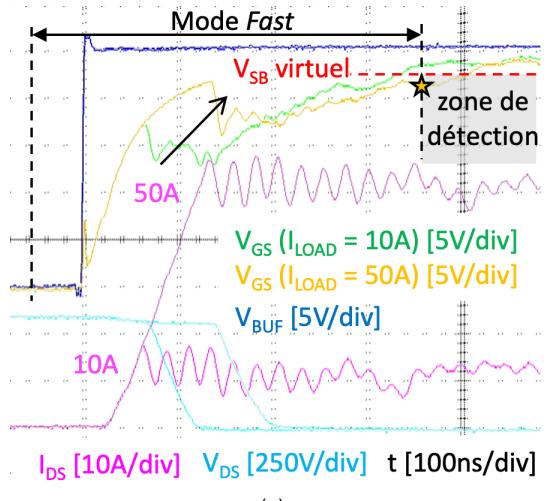

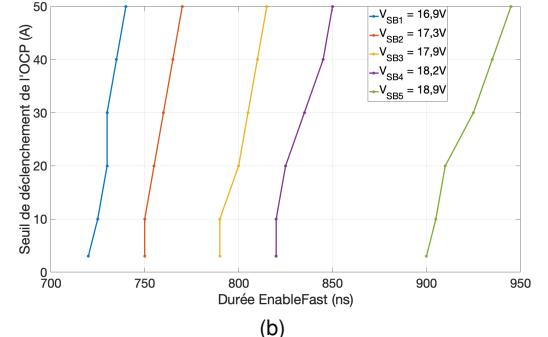

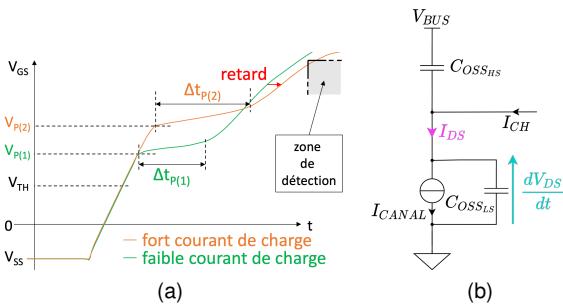

Le principe de la fonction OCP repose sur le lien entre la vitesse de charge de grille et le courant de charge. Ce dernier modifie la dynamique de  $V_{GS}$ , notamment au niveau de la hauteur et de la durée du plateau Miller lors de l'amorçage.

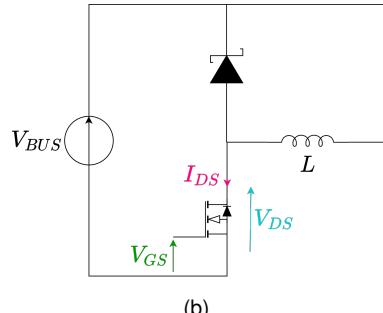

En effet, en comparaison avec une commutation à vide, la formation du canal requiert une polarisation de grille plus importante à courant de charge élevé. Cela se traduit par un  $dV_{DS}/dt$  retardé dans le temps car la commutation effective débute à  $V_{GS}$  plus élevé qu'à courant de charge nul comme illustré en

(a)

(b)

FIG. 9. Dynamiques de charge de grille (détection inhibée) sous différents courants de charge (10A, 50A) (a), résultats paramétriques de l'influence de la durée d'activation *EnableFast* du buffer *Fast* sur le seuil de surcharge détectable (b) ( $V_{BUS} = 600V$ ,  $R_{FAST} = 47\Omega$ ,  $R_{SSD} = 82\Omega$ ,  $V_{DD} = 20V$ ,  $V_{SS} = -5V$ )

FIG. 10. Principe de dépendance du plateau Miller en amplitude et en durée au courant de charge (a), schéma équivalent (b)

Fig. 10a.

Le courant de charge  $I_{CH}$  impacte donc la dynamique de charge de grille au niveau de la durée et la hauteur du plateau Miller (Fig. 9a et éq. (5)). La fonction OCP repose sur la détection de ce ralentissement de charge de grille à courants élevés (Fig. 1b en magenta).

$$V_P(t) \approx V_{TH} + \frac{I_{CH}}{G_{FS}} + \frac{2C_{OSS}}{G_{FS}} * \frac{dV_{DS}}{dt} + f(\lambda * V_{DS}(t)) \quad (5)$$

Avec  $\lambda$  le paramètre traduisant l'évolution temporelle oblique du plateau (analogue à l'effet Early en technologie bipolaire) et  $G_{FS}$  le gain du transistor. Une relation approchée liant la vitesse de commutation au courant de charge est décrite par éq. (6) d'après la Fig. 10b. Une modélisation plus précise a été conduite dans la thèse [14].

$$\frac{dV_{DS}}{dt} \approx \frac{I_{CANAL} - I_{CH}}{2C_{OSS}} \quad (6)$$

D'où une relation approchée entre durée du plateau Miller et courant de charge en (7).

$$\Delta t_P \approx \frac{2C_{OSS}V_{BUS}}{I_{CANAL} - I_{CH}} \quad (7)$$

Il apparaît alors que la durée du plateau Miller augmente avec le courant de charge, comme illustré en Fig. 10a. Tandis que les fonctions de protection précédentes reposent toutes sur une intersection horizontale avec la zone de détection décrite en Fig. 1a, celle-ci repose sur une intersection verticale, lors du passage en mode *Slow* à la fin de l'amorçage. Cela permet un réglage du seuil de protection indépendamment des autres fonctions de protection.

#### 4. CONCLUSION

L'architecture proposée de gate driver parallèle à résistances de grille commutées et à grille quasi-flottante a été validée à travers les différentes fonctions de protections qu'elle offre (CC1, CC2 interne et externe, surcharges et détérioration de l'oxyde de grille). Son principe repose sur l'utilisation de deux voies de commande à résistances de grilles distinctes : une résistance nominale de faible valeur est utilisée lors des commutations pour assurer leur dynamique, et une résistance de surveillance à forte valeur est utilisée lors des phases de conduction pour placer la grille dans un état quasi-isolé et ainsi augmenter la sensibilité de la tension de grille à de possibles signatures électriques de défauts. Un intérêt particulier a été porté sur la robustesse des différentes fonctions de protection. Une protection contre CC de type 1 et 2 interne est atteinte en 250ns. Cette méthode de protection multifonctionnelle présente également l'avantage d'être intégrable sur circuit intégré. Les travaux futurs porteront sur le développement de nouvelles fonctions et sur des variantes de cette architecture.

#### 5. RÉFÉRENCES

- [1] S. Mocevic, J. Wang, R. Burgos, D. Boroyevich, M. Jaksic, C. Stancu, and B. Peaslee, "Comparison and Discussion on Short-Circuit Protections for Silicon-Carbide MOSFET Modules : Desaturation Versus Rogowski Switch-Current Sensor," *IEEE Transactions on Industry Applications*, vol. 56, no. 3, pp. 2880–2893, 2020.

- [2] W. T. Cui, W. J. Zhang, J. Y. Liang, H. Nishio, H. Sumida, H. Nakajima, Y.-T. Hsieh, H.-H. Tsai, Y.-Z. Juang, W.-K. Yeh, and W. T. Ng, "A Dynamic Gate Driver IC with Automated Pattern Optimization for SiC Power MOSFETs," in *IEEE 34th International Symposium on Power Semiconductor Devices and ICs (ISPSD)*, 2022, pp. 33–36.

- [3] M. Wang, W. J. Zhang, J. Liang, W. T. Cui, W. Tung Ng, H. Nishio, H. Sumida, and H. Nakajima, "A Smart Gate Driver for SiC Power MOSFETs with Aging Compensation and Ringing Suppression," in *33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD)*, 2021, pp. 67–70.

- [4] S. Azzopardi, T.-L. Le, F. Richardeau, W. Jouha, Y. Barazi, N. Rouger, J.-M. Blaqui  re, S. Vinnac, and M. Picot-Digoix, "Dispositif de Commande, de Protection et de Surveillance de l'  tat de Sant   d'un Transistor de Puissance," 27 Juillet 2022, brevet FR2207714, Safran, CNRS, Toulouse INP.

- [5] M. Picot-Digoix, F. Richardeau, J.-M. Blaqui  re, S. Vinnac, S. Azzopardi, and T.-L. Le, "Quasi-Flying Gate Concept Used for Short-Circuit Detection on SiC Power MOSFETs Based on a Dual-Port Gate Driver," *IEEE Transactions on Power Electronics*, vol. 38, no. 6, pp. 6934–6938, 2023.

- [6] J. Sun, H. Xu, X. Wu, and K. Sheng, "Comparison and analysis of short circuit capability of 1200V single-chip SiC MOSFET and Si IGBT," in *13th China International Forum on Solid State Lighting : International Forum on Wide Bandgap Semiconductors China (SSLChina : IFWS)*, 2016, pp. 42–45.

- [7] M. Cui, J. Li, Y. Du, and Z. Zhao, "Behavior of SiC MOSFET under Short-Circuit during the On-State," *IOP Conference Series : Materials Science and Engineering*, vol. 439, no. 2, p. 022026, nov 2018.

- [8] F. Boige, D. Tr  mouilles, and F. Richardeau, "Physical Origin of the Gate Current Surge During Short-Circuit Operation of SiC MOSFET," *IEEE Electron Device Letters*, vol. 40, no. 5, pp. 666–669, 2019.

- [9] A. E. Awwad and S. Dieckerhoff, "Short-circuit evaluation and overcurrent protection for SiC power MOSFETs," in *2015 17th European Conference on Power Electronics and Applications (EPE'15 ECCE-Europe)*, 2015, pp. 1–9.

- [10] F. Richardeau and Y. Barazi, "Predictive gate ageing-laws of SiC MOSFET under repetitive short-circuit stress," *Microelectronics Reliability*, vol. 138, p. 114706, 2022, 33rd European Symposium on Reliability of Electron Devices, Failure Physics and Analysis.

- [11] G. Romano, A. Fayyaz, M. Riccio, L. Maresca, G. Breglio, A. Castellazzi, and A. Irace, "A Comprehensive Study of Short-Circuit Ruggedness of Silicon Carbide Power MOSFETs," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 4, no. 3, pp. 978–987, 2016.

- [12] F. Boige, F. Richardeau, D. Tr  mouilles, S. Lefebvre, and G. Guibaud, "Investigation on damaged planar-oxide of 1200 V SiC power MOSFETs in non-destructive short-circuit operation," *Microelectronics Reliability*, vol. 76-77, pp. 500 – 506, Sep. 2017.

- [13] P. D. Reigosa, F. Iannuzzo, and L. Ceccarelli, "Effect of short-circuit stress on the degradation of the SiO<sub>2</sub> dielectric in SiC power MOSFETs," *Microelectronics Reliability*, vol. 88-90, pp. 577–583, 29th European Symposium on Reliability of Electron Devices, Failure Physics and Analysis (ESREF 2018).

- [14] T. Rossignol, "Contribution    la caract  risation et    la commande r  approch  e de composants    grand gap moyen tension pour onduleur de tension," Ph.D. dissertation, LAPLACE, Universit   de Toulouse, CNRS, INPT, UPS, 2015.