# Développement de fonctionnalités rapides, précises et intégrées CMOS, pour la commutation optimale et la protection interne des onduleurs à module SiC MOSFET

Anas ELBOUBKARI<sup>1,2,3</sup>, Matthieu MASSON<sup>1,2,3</sup>, Nicolas ROUGER<sup>1,3</sup>, Marc COUSINEAU<sup>1,3</sup>, Frédéric RICHARDEAU<sup>1,3</sup>, Matthew BACCHI<sup>2,3</sup>, Jean-Marc BLAQUIERE<sup>1,3</sup>, Alexandre LABORDE<sup>2,3</sup>, Sébastien VINNAC<sup>1</sup>, Didier FLUMIAN<sup>1,3</sup>, Pierre CALMES<sup>2,3</sup>

<sup>1</sup>LAPLACE, Université de Toulouse, CNRS, INPT, UPS, Toulouse, France,

<sup>2</sup>NXP Semiconductors, <sup>3</sup>LabCom SEMA NXP/LAPLACE

**RESUME** – Les modules à base de MOSFET SiC sont désormais disponibles sur une large gamme de tension et courants. Ils sont intrinsèquement performants. Cet article présente un focus sur deux verrous majeurs associés à la commutation optimale et la protection interne de ces modules : la détection intégrée rapide de court-circuit par la mesure de la charge de grille, et la gestion optimale et adaptative du temps mort par l'observation du circuit de commande rapprochée.

**Mots-clés**—Commande rapprochée, modules SiC, intégration CMOS, protection court-circuit, optimisation temps-mort.

## 1. INTRODUCTION

Les onduleurs utilisant des modules MOSFET SiC ont démontré des gains significatifs en traction, notamment dans le véhicule électrique et le ferroviaire [1]. Par rapport aux IGBT Silicium, ils présentent néanmoins une tenue réduite aux régimes extrêmes tels que le court-circuit (CC) de par leur conduction unipolaire et leur fort gain [2, 3]. Ainsi le temps de détection et protection effectif en court-circuit doit être réduit, autour de 1µs, et si possible encore plus rapidement. D'autre part, les modules SiC n'intègrent pas systématiquement de diodes de roue libre à barrière Schottky (SBD) en parallèle, afin de limiter leur coût. La diode body bipolaire (intrinsèque) est alors utilisée pendant le temps mort, pouvant avoir un impact par la suite les pertes énergétiques ainsi que sur les caractéristiques du MOSFET SiC [4]. La gestion optimale du temps mort devient alors cruciale, en prenant en compte les variations de température et de point de fonctionnement, mais aussi de dispersions (e.g. isolateurs, caractéristiques des MOSFET SiC, tensions de commande, résistances de grilles). Des solutions innovantes sur ces deux sujets sont développées au sein du LabCom SEMA regroupant NXP Semiconductors et le laboratoire LAPLACE. Celles-ci s'appuient sur une intégration CMOS de fonctions d'observation rapide et précise de signaux clés accessibles, en particulier le courant de grille permettant une forte immunité et une plus grande flexibilité d'intégration sur ASIC, en technologie SMARTMOS 10 130nm de NXP.

## 2. AVANTAGES ET DEFIS DE L'APPROCHE DE LA CHARGE DE GRILLE POUR LA DETECTION DE COURT-CIRCUIT

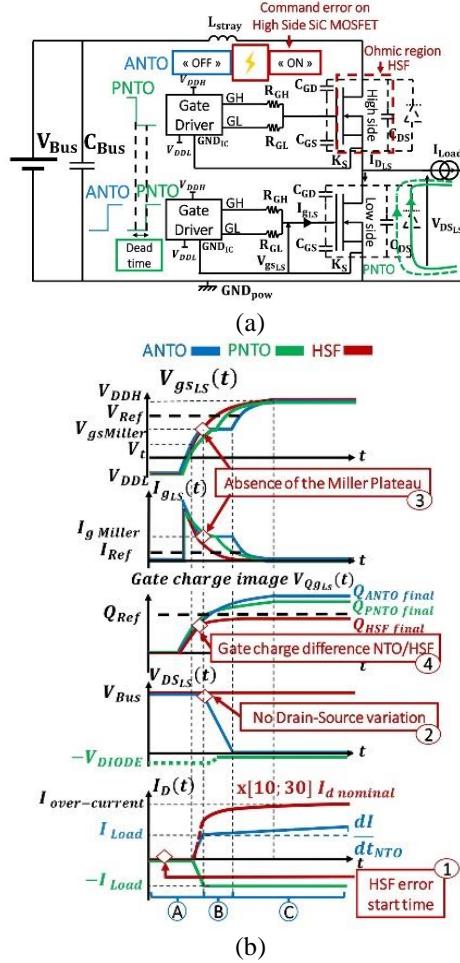

La détection de court-circuit en 2D présentée (Fig. 1) consiste à surveiller les signaux de basse tension. Le signal

primaire est l'image de la charge de grille ( $V_{Qg}$ ) qui permet au système de distinguer les événements de court-circuit des modes de fonctionnement normaux [5]. Le court-circuit (HSF) est initié avant la mise en marche du MOSFET SiC côté Low-Side. Contrairement aux cas de mise en marche normale active et passive (ANTO, PNTO), le cas HSF montre une absence de

Fig. 1. (a) Circuit de bras d'onduleur, (b) Signaux qualitatifs du MOSFET SiC côté bas dans les cas ANTO, PNTO et HSF

|                 | $V_{gs}$ & $I_g$ time constant ( $\tau$ ) |                |                           |

|-----------------|-------------------------------------------|----------------|---------------------------|

| Switching cases | A                                         | B              | C                         |

| ANTO            | $R_G \cdot C_{iss_{min}}$                 | Miller Plateau | $R_G \cdot C_{iss_{max}}$ |

| PNTO            |                                           |                | $R_G \cdot C_{iss_{max}}$ |

| HSF             |                                           |                | $R_G \cdot C_{iss_{min}}$ |

(a)

| When $V_{gs}(t)$ or $I_g(t)$ reaches $V_{Ref}$ (on the rising edge) or $I_{Ref}$ (on the falling edge) |  | State |

|--------------------------------------------------------------------------------------------------------|--|-------|

| if $V_{Qg}(t) > V_{Qref}$                                                                              |  | NTO   |

| if $V_{Qg}(t) < V_{Qref}$                                                                              |  | HSF   |

(b)

Fig. 2. (a) Tableau de constantes de temps relatives aux cas de commutation, (b) Tableau de diagnostic HSF.

plateau de Miller causé par la non-variation de la tension drain-source ( $V_{DS}$ ) du MOSFET SiC, comme le montre la figure 1(b). De plus, la constante de temps de la tension grille-source du SiC MOSFET ( $V_{gs}$ ) et le courant de grille ( $I_g$ ) dépendent du cas de commutation, comme illustré dans la figure 2(a). Ces différentes conditions de cas ont un impact considérable sur la valeur finale de la charge de grille. En termes de comparaison quantitative, le HSF a la valeur de charge de grille finale la plus faible et le ANTO a la plus élevée ( $Q_{HSF} < Q_{PNTO} < Q_{ANTO}$ ). Pour évaluer les valeurs de charge de grille dans des conditions fixes, un signal de déclenchement secondaire peut être dérivé soit de  $I_g$ , soit de  $V_{gs}$ . Ces signaux seront respectivement comparés à une référence de courant ( $I_{Ref}$ ) ou de tension ( $V_{Ref}$ ) pour initier l'examen de la valeur de charge de grille et ceci indépendamment du temps en utilisant une approche 2D ( $Q_g$ ,  $V_{gs}$  ou  $I_g$ ). Pour augmenter la distinction de la charge de grille entre  $Q_{HSF}$  et  $Q_{ANTO}$  &  $Q_{PNTO}$ ,  $I_{Ref}$  doit être inférieur au courant du plateau de Miller ( $I_g_{Miller}$ ) et  $V_{Ref}$  doit être supérieur à la tension du plateau de Miller ( $V_{gsMiller}$ ). Ces conditions aident à éviter les fausses détections de court-circuit. Lorsque  $I_g(t)$  atteint  $I_{Ref}$  (respectivement lorsque  $V_{gs}(t)$  atteint  $V_{Ref}$ ), le système examine la mesure de  $Q_g(t)$  et la compare à  $Q_{Ref}$ . Le signal de détection de court-circuit passe à l'état actif si la référence de l'image de

charge de grille ( $Q_g$ ) est inférieure à la référence ( $Q_{Ref}$ ), sinon l'événement est considéré comme une commutation normale, comme mentionné dans la figure 2(b). Malgré la simplicité de cette méthode de détection de court-circuit en 2D, il est nécessaire d'avoir une estimation rapide et précise de la charge de grille pour établir une réaction rapide et robuste du système.

### 2.1. Robustesse de la charge de grille

Une méthode de détection de court-circuit doit prendre en compte la dispersion de tous les paramètres dans un circuit de bras d'onduleur pour assurer des détections de court-circuit sûres et robustes. Malheureusement, ces paramètres sont souvent négligés dans la littérature lorsqu'il s'agit de proposer des méthodes de détection de court-circuit, alors qu'ils peuvent potentiellement causer des fausses détections. Ces paramètres peuvent être classés en deux catégories :

- Les paramètres de point de fonctionnement : résistance de grille externe ( $R_{GH}$ ), résistance de grille interne ( $R_{Gint}$ ), tension de bus ( $V_{Bus}$ ), charge de courant ( $I_{Load}$ ).

- Les inductances parasites : inductance parasite de grille ( $L_g$ ), inductances parasites de source commune ( $L_{Ks}$ ).

(a)

(b)

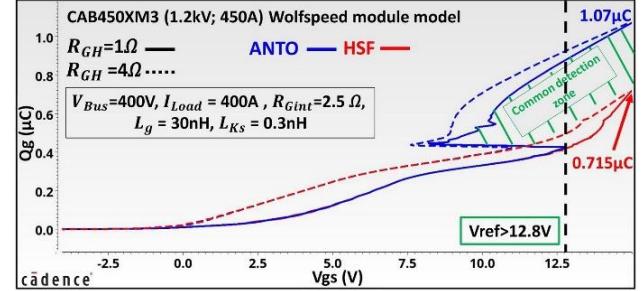

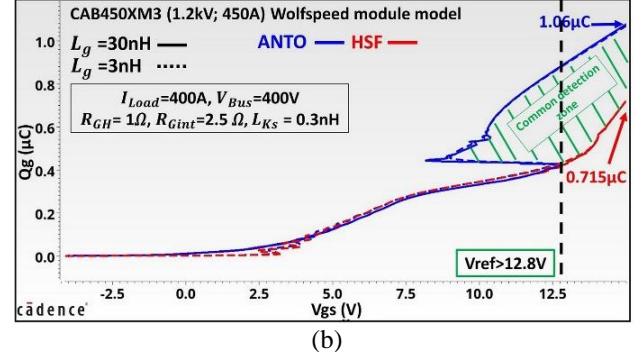

Fig. 3. Charge de grille ( $Q_g$ ) vs tension de grille-source, simulation de variations paramétrique du point de fonctionnement, (a) variation de  $R_{GH}$ , (b) variation de  $I_{Load}$

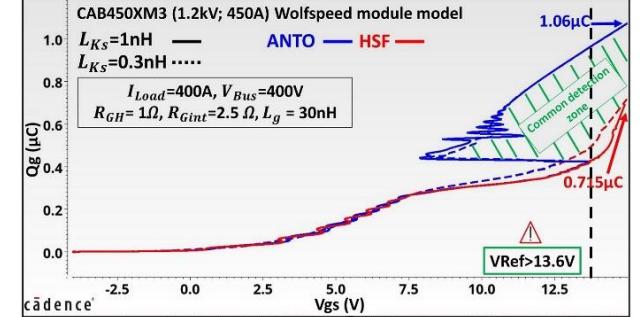

Fig. 4. Charge de grille ( $Q_g$ ) vs tension de grille-source, simulation de variations paramétrique de l'inductance parasite  $L_{Ks}$ .

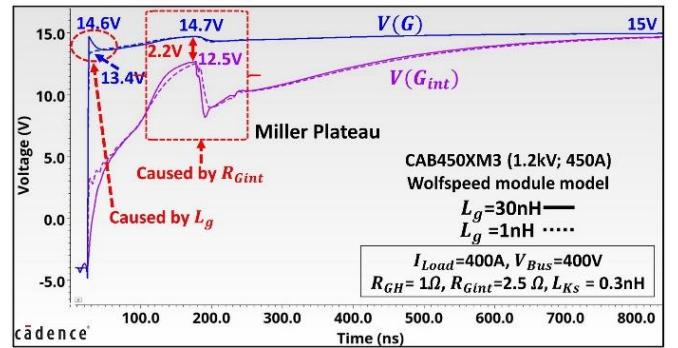

Fig. 5. Simulation de variation paramétrique des tensions de grille-source interne et externe du MOSFET SiC.

Les paramètres de point de fonctionnement sont principalement déterminés par les spécifications de l'application. En revanche, les inductances parasites peuvent, mais pas toujours, être optimisées en conséquence. Les figures 3 et 4 montrent les signaux de charge de grille simulés avec Cadence™ en fonction de la tension interne grille-source en utilisant un modèle de module MOSFET SiC Wolfspeed™ CAB450XM3 (1.2 kV, 450 A) tout en faisant varier les paramètres de point de fonctionnement et les inductances parasites. Les simulations

démontrent la haute sélectivité de la zone de détection commune (en pointillé vert). Ces résultats confirment la robustesse de l'approche de la charge de grille et la nécessité d'une tension  $V_{Ref}$  ajustable pour éviter les fausses détections de court-circuit. Les éléments internes du MOSFET (comme  $R_{Gint}$  et  $L_g$ ) compliqueront le seuillage sur  $V_{GS}$  (comme le montre la figure 5). Il y a donc un intérêt à utiliser le courant de grille comme signal de déclenchement qui nous donnera une information plus fiable sur l'état de la capacité d'entrée du MOSFET SiC.

### 3. NOUVELLE ARCHITECTURE DE GATE DRIVER AVEC UN ESTIMATEUR DE CHARGE DE GRILLE PRECIS, RAPIDE ET INTEGRE

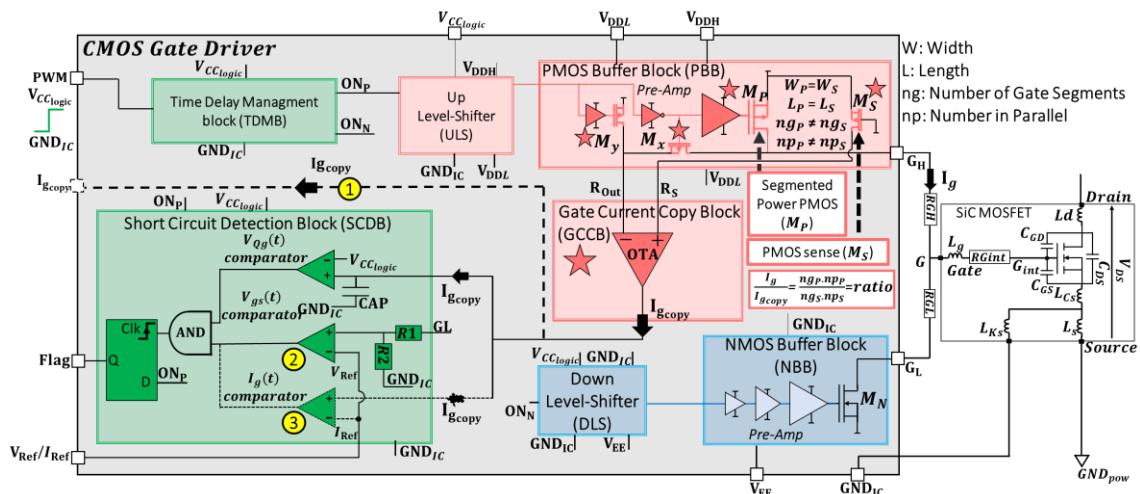

#### 3.1. Architecture du Gate Driver

La conception proposée vise à présenter une copie rapide, stable et précise du courant de grille avant le début du plateau de Miller (avec un courant de pic possible de 15 A en 40 ns). Cette copie doit conserver sa précision jusqu'à la fin de la charge de grille. En raison du niveau de tension élevé de la sortie du gate-driver (p. ex. -4V/15V), la conception utilise à la fois des transistors CMOS haute tension (p. ex. >30V) et basse tension (p. ex. 1.8V, 5V). Pour expliquer clairement le concept derrière cette copie précise et rapide de  $I_g$ , nous décrirons le diagramme de blocs de l'architecture du gate-driver proposée présentée à la figure 6.

Garantir une détection fiable, précise et ultra-rapide du courant  $I_g$  nécessite un capteur de courant sur puce composé d'un amplificateur opérationnel de transconductance (OTA) et d'un senseFET PMOS (Ms) qui est assorti à un PMOS de puissance segmenté (Mp). Le transistor de puissance SiC MOSFET est piloté par les transistors de sortie du gate-driver Mp et Mn qui sont contrôlés par le signal d'entrée (PWM). Lorsque le signal PWM est haut, Mp est allumé et Mn est éteint, et inversement. Pendant la phase de charge de grille SiC (PWM est haut), le capteur de courant détecte et génère en interne une copie proportionnelle au courant  $I_g$  ( $I_{copy}$ ). Un transistor haute tension (Mx, p. ex. >30V) est utilisé pour isoler le système de copie de courant de grille de la sortie haute tension du PMOS. Pour assurer une copie précise du courant, Mp et Ms présentent la même tension source-grille ( $V_{SG}$ ), avec Ms toujours allumé. L'OTA et l'état des transistors de commutation Mx et My garantiront la même tension de drain pour Mp et Ms. Les transistors Mp et Mx sont contrôlés par le même signal

contrairement à My qui est contrôlé par le signal complémentaire. Lorsque Mp est allumé, Mx est également allumé, assurant la connexion du potentiel  $V(G_H)$  au potentiel  $V(R_{out})$  et par conséquent l'OTA veillera à ce que le potentiel  $V(R_s)$  suive  $V(R_{out})$ . Les transistors Mp, Ms, Mx et My sont assortis en largeur et en longueur. Le rapport de copie de courant  $I_{copy}/I_g$  est déterminé par le rapport  $(n_{gp} \cdot n_{pP})/(n_{gS} \cdot n_{pS})$ , avec  $n_{gS}$  le nombre de segments de grille d'un transistor élémentaire et  $n_{pX}$  le nombre de transistors connectés en parallèle. My est utilisé pour régler  $V(R_{out})$  et  $V(R_s)$  au même potentiel et pour éliminer les décalages lorsque le signal PWM est bas.  $I_{copy}$  sera intégré en interne dans le bloc de détection de court-circuit (SCDB) pour générer une estimation précise de la charge de grille du SiC MOSFET. Cette information précise sera interprétée avec une tension de grille à source SiC MOSFET réduite ou  $I_{copy}$  pour détecter le type de court-circuit I (HSF).

Le capteur de courant conçu est une version modifiée et améliorée de l'approche utilisée pour les détecteurs de courant de crête des régulateurs Buck [6], avec ici la contrainte particulière que cette mesure de courant est implémentée sur les transistors PMOS (>30V) et avec un besoin de précision et rapidité supplémentaire.

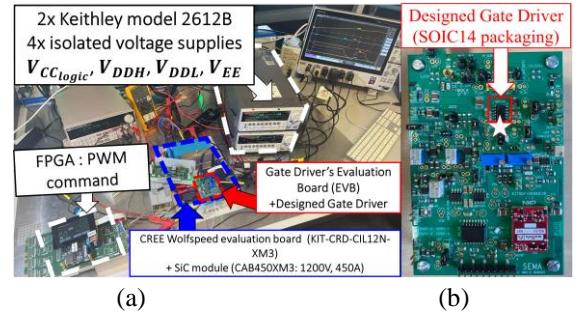

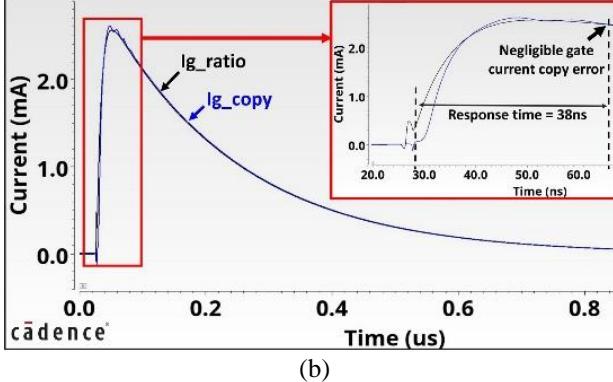

#### 3.2. Validation de la fonctionnalité de copie de courant

La broche IC dédiée (numéro 1, entourée de jaune sur la figure 6) du gate-driver conçu (monté en boîtier SOIC-14 et soudé sur une carte d'évaluation conçue, figure 8b) est utilisée pour valider la précision et la rapidité du capteur de courant.

Fig. 7. (a) Banc d'essai de test en double impulsion et HSF, (b) Carte d'évaluation des Gate Driver

Fig. 6. Architecture du Gate-Driver conçu, (1) Variante évaluant  $I_{copy}$ , (2) Variante utilisant  $V_{Qg}$  et  $V_{gs}$  pour la détection de court-circuit, (3) Variante utilisant  $V_{Qg}$  et  $I_g$  pour la détection de court-circuit .

(a)

(b)

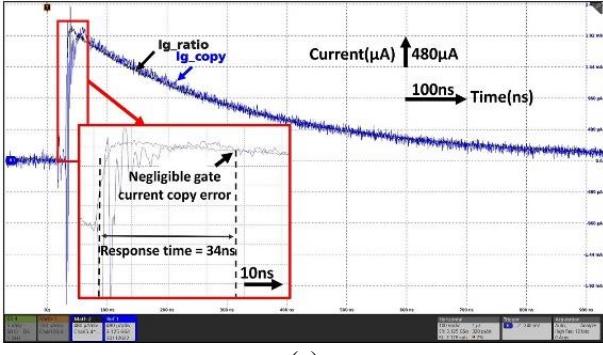

Fig. 8. Superpositions des résultats d'  $I_{g\_copy}$  &  $Ig/ratio$  ( $V_{DDH} = 15$  V,  $V_{DDL} = 10$  V,  $V_{CClogic} = 1.5$  V,  $V_{EE} = -4$  V,  $R_{GH} = 5.4$   $\Omega$ ,  $R_{GL} = 1$   $\Omega$ ,  $C_L = 50$  nF).

(a) Manipulation, (b) Simulation

Pour cette première phase de validation, une charge capacitive fixe de 50 nF ( $C_L$ ) est utilisée à la place de la capacité d'entrée du MOSFET SiC ( $C_{iss}$ ). La figure 7(a) montre le résultat expérimental de la superposition du courant  $I_{gcopy}$  générée en interne par le gate-driver et de  $I_g$  mesurée en externe par une sonde optique de 1 GHz (chute de tension à travers la résistance de grille externe  $R_{GH}$ ). Le temps de réponse d' $I_{gcopy}$  est de 34 ns et l'erreur est négligeable (<1%) après ce retard initial qui est en corrélation avec les résultats de simulation présentés dans la figure 7(b). Ceci valide la fiabilité de l'estimation de la charge de grille. En simulation, nous avons assuré la robustesse de la fonctionnalité de copie de courant ( $I_{gcopy}$ ) face aux variations PVT (Processus, Tension et Température) grâce aux outils exhaustifs disponibles chez NXP Semiconductors.

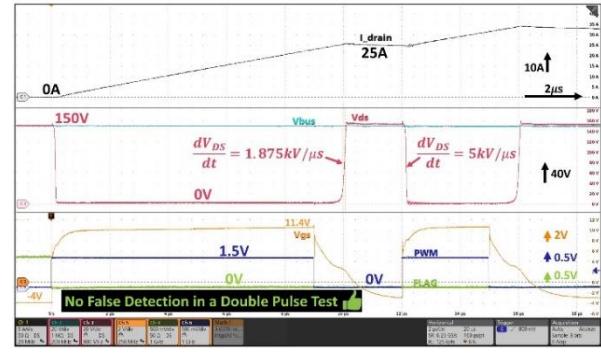

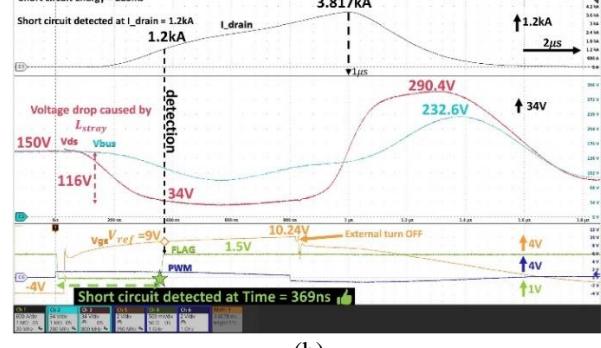

#### 4. FONCTIONNALITE DE DETECTION DES COURTS-CIRCUITS ET VALIDATION A L'AIDE D'UN MODULE DEMI-PONT SiC

Pour valider le concept et la robustesse du bloc de détection de court-circuit, la deuxième broche de l'IC (numéro 2, entourée en jaune sur la figure 6) est mesurée sur la carte d'évaluation conçue pour être connectée à un module de puissance SiC CAB450M12XM3 dans un dispositif de test à double impulsion (KIT-CRD-CIL12N-XM3), comme le montre la figure 8(a). La figure 9(a) montre un événement de commutation normal (avec la méthode de double impulsion), sans détection de court-circuit (le signal de détection reste bas). Le MOSFET côté High-Side est piloté à  $V_{GS} = -4$  V, ce qui représente une commutation classique avec conduction dans sa diode de corps. En cas d'événement de court-circuit, le MOSFET côté High-Side est piloté à une tension constante  $V_{GS} = 18$  V avec une alimentation externe isolée. Dans les deux expériences, le MOSFET SiC côté basse tension est également piloté par le gate-driver CMOS conçu. Dans le cas de court-circuit, la figure 9(b) montre un temps de détection de 369 ns (le signal de détection passe à '1'),

(a)

(b)

Fig. 9. Manipulations utilisant le module SiC CAB450XM3. (a) ANTO, (b) HSF.  $V_{Bus} = 150$  V,  $R_{GH} = 1\Omega$ ,  $R_{GL} = 12\Omega$ ,  $V_{Ref} = 9$  V,  $V_{DDH} = 12$  V,  $V_{DDL} = 10$  V,  $V_{CClogic} = 1.5$  V.

correspondant à un courant de drain 1,2 kA au moment de la détection, ce qui est bien inférieur au courant de saturation du canal (>7 kA). Cela garantit une protection rapide contre les courts-circuits par rapport au courant nominal de 450 A du module de puissance MOSFET SiC. Pour des raisons de sécurité, la tension du bus continu est réduite lors des expériences à 150 V et  $V_{DDH}$  à 12 V sans limiter la validation du circuit. Pour le moment, le signal de détection n'est pas bouclé ni vers la commande éloignée (FPGA) ni sur le driver. Le signal PWM est censé être désactivé après la détection afin de permettre l'arrêt progressif réalisé par le NMOS intégré (Mn) au niveau de la sortie du gate-driver CMOS, piloté par le FPGA qui génère le signal PWM. Ces résultats démontrent la rapidité de la méthode de détection de court-circuit sans nécessiter de diode haute tension externe DSAT, en utilisant une méthode de détection de charge de grille et d' $I_{gcopy}$  intégrée et précise, qui est intrinsèquement robuste.

#### 5. OPTIMISATION DE LA DUREE DU TEMPS-MORT

##### 5.1. Intérêt de l'optimisation du temps-mort

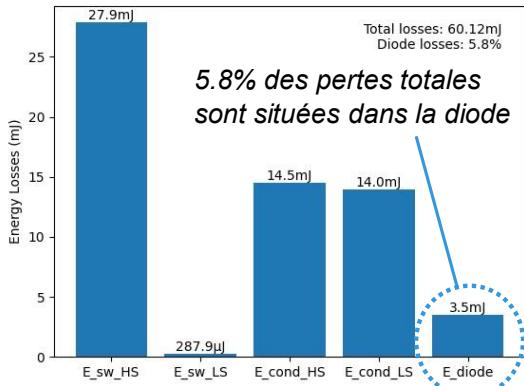

Le temps-mort utilisé entre le blocage d'un transistor au sein d'un bras d'onduleur et l'amorçage du transistor opposé permet d'éviter tout risque de commutation dure quelles que soient les conditions d'opération du convertisseur. Durant cette période, le courant circule au travers de la diode de corps intrinsèque du MOSFET SiC qui présente une tension directe plus élevée que leur équivalents en silicium (4.7 V à 25°C et à 400 A pour le module CAB450M12XM3 d'après la documentation du fabricant). La figure 10 montre le détail des pertes au sein d'une cellule de commutation sans diode externe en simulation LTSpice dans des conditions représentatives d'une utilisation onduleur.

Les pertes de recouvrement inverse de la diode interne (comptabilisées dans les pertes à l'amorçage du transistor

Fig. 10. Détail des pertes dans un module CAB450M12XM3 sur une période de commutation en simulation LTSpice ( $V_{BUS}=800V$ ,  $I_{load}=400A$ ,  $f_{SW}=10kHz$ ,  $\alpha=50\%$ ,  $R_{G,EXT}=1\Omega$ , temps mort :  $t_D=1\mu s$ ,  $V_{Driver}=-4V/+15V$ ,  $T_j=50^\circ C$ ) Les pertes entourées ne représentent que les pertes par conduction dans la diode interne. Les pertes de recouvrement sont incluses dans les pertes en commutation du transistor actif.

High-Side) sont aussi affectées par une durée excessive du temps mort [7]. Pour finir, [3] met en évidence une dégradation des caractéristiques du transistor MOSFET SiC (notamment une diminution de la tension de seuil) due à une utilisation prolongée de la diode interne.

Pour ces raisons à la fois énergétiques mais aussi de fiabilité, l'utilisation d'un réglage de temps-morts fixes, tels que ceux utilisés pour un convertisseur à IGBT, est peu approprié au cas d'une cellule de commutation à MOSFET SiC. La détection du temps de blocage de chaque transistor au sein de la cellule permet alors de définir le temps-mort optimal à appliquer pour un point de fonctionnement donné [8].

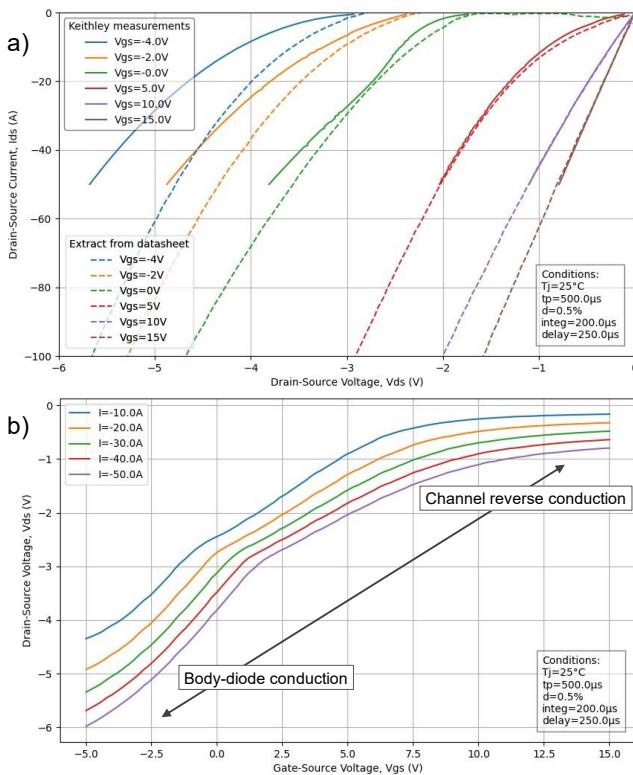

Fig. 11. Mesure expérimentale du comportement statique dans le 3<sup>ème</sup> quadrant. a) Caractéristique courant/tension comparée à la datasheet. b) Passage de la conduction diode de corps au canal avec l'évolution de la tension de grille.

## 5.2. Caractérisation du comportement du composant dans le 3<sup>ème</sup> quadrant

La figure 11 présente une mesure des caractéristiques statiques dans le 3<sup>ème</sup> quadrant d'un transistor MOSFET SiC C3M0016120K (1200 V, 115 A) correspondant à une puce élémentaire que l'on retrouve dans le module présenté à la partie précédente. Nous avons mis en évidence l'évolution progressive de la tension drain-source en fonction de la tension de grille. Il en résulte une difficulté à imposer une dynamique de transition rapide entre le mode de conduction dans la diode intrinsèque et le mode ohmique, et ainsi minimiser le temps d'activation de la diode PIN au sein du MOSFET.

On remarque l'importance du choix de la tension de grille appliquée au blocage du transistor pour diminuer les pertes par conduction dans la diode interne. Par exemple, d'après la figure 11 b) pour un courant nominal de 50 A l'utilisation d'une tension de blocage de 0 V au lieu de -5 V pendant le temps-mort permet de réduire la tension inverse d'environ 30% et de diminuer d'autant les pertes engendrées. Une caractérisation plus fine du comportement dans les 1<sup>er</sup> et 3<sup>ème</sup> quadrants est en cours d'étude. Ce travail nous permettra, par la suite, d'optimiser les temps-morts.

## 6. GESTION OPTIMALE ET ADAPTATIVE DU TEMPS-MORT

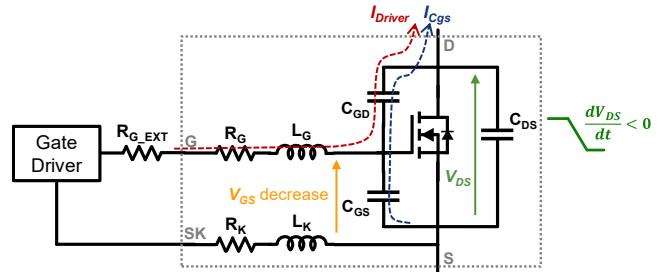

Un système de gestion automatique du temps-mort au niveau du circuit driver est en cours d'étude. Dans le principe, nous utilisons certains blocs comparables à la méthode de protection contre le court-circuit, en réalisant une mesure de l'état du transistor de puissance sans composant externe haute tension. Contrôler le temps-mort au plus proche du transistor de puissance permet de ne pas dépendre des temps de propagation et de la gigue introduits par l'isolateur haute tension et de s'adapter toujours au mieux au point de fonctionnement de la cellule. La figure 12 présente le phénomène de couplage

Fig. 12. Schéma présentant l'appel de courant de grille lorsque le transistor complémentaire à l'état bloqué subi un  $dV_{DS}/dt$  négatif

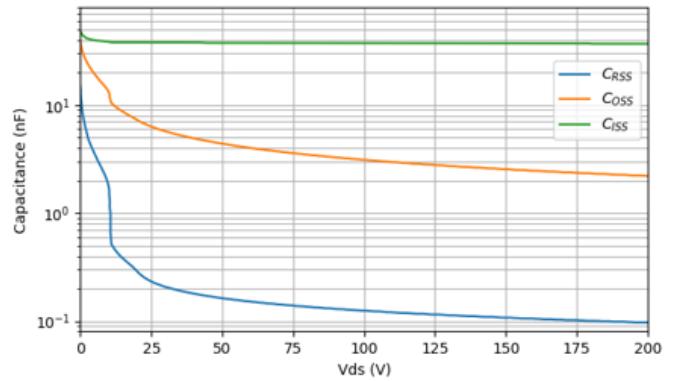

Fig. 13. Evolution des capacités parasites du MOSFET SiC en fonction de la tension drain-source ( $C_{RSS}=C_{GD}$ ,  $C_{OSS}=C_{GD}+C_{DS}$ ,  $C_{ISS}=C_{GS}+C_{GD}$ ) Extrait de la documentation fournie par le fabricant.

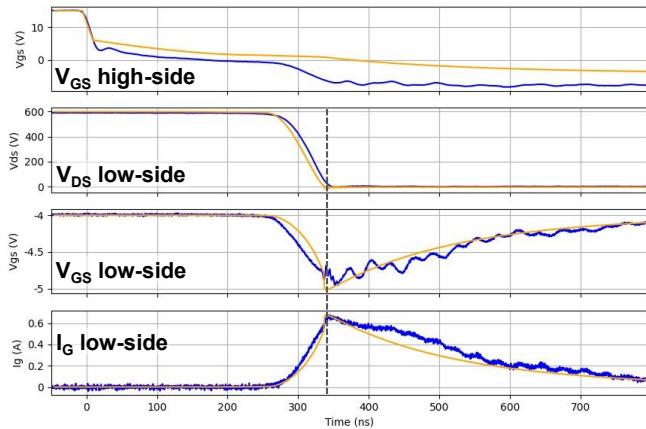

Fig. 14. Oscillogramme présentant le pic de courant de grille et la chute de la tension grille-source au moment du passage par zéro de la tension drain-source. Simulation LTSpice en jaune et résultat expérimental en bleu. ( $V_{BUS} = 600$  V,  $I_{Load} = 150$  A,  $R_{G\_EXT} = 1$   $\Omega$ ,  $V_{Driver} = +15$  V / -3 V)

capacitif naturellement présent entre le drain et la grille d'un MOSFET et qui peut être utilisé pour la détection du temps-mort optimal. La capacité  $C_{GD}$  varie de manière fortement non-linéaire avec la tension  $V_{DS}$  comme le montre la figure 13. Cette augmentation brusque de la valeur de capacité lorsque  $V_{DS}$  s'approche de zéro provoque un pic de courant de grille se situant à la fin du blocage du transistor actif, et donc au début de la mise en conduction de la diode de corps du transistor complémentaire. La figure 14 illustre ce phénomène en simulation et expérimentalement.

Un système de copie de courant (similaire à celui développé pour la détection de courts-circuits) suivi d'un détecteur de pic rapide peut donc permettre une détection fiable et intégrée du temps de blocage sans l'utilisation de composants haute tension externes.

## 7. CONCLUSION

Les degrés de liberté offerts par la réalisation d'un circuit intégré dédié à la commande rapprochée des transistors de puissance permettent d'envisager de nouvelles stratégies précises et rapides dans le contexte du pilotage des modules SiC MOSFET. Dans un contexte industriel, la sécurisation de la commutation est primordiale, afin de détecter de façon rapide et robuste les possibles courts-circuits. De nouvelles stratégies de commutation sont aussi nécessaires, afin de réduire la durée des temps morts, tout en garantissant des commutations sûres. L'observation de signaux directement accessibles depuis le

circuit intégré gate-driver (comme le courant de grille) permet la gestion rapide et fiable du pilotage des modules de puissance tout en réduisant les surcoûts et l'inertie liés à l'utilisation de composants externes. L'intégration monolithique du circuit gate-driver avec les outils de conception, de vérification, et la technologie BiCMOS de NXP Semiconductors permet de répondre à ces enjeux. Des résultats expérimentaux des solutions innovantes pour ces deux fonctionnalités ont été présentés.

## 8. REFERENCES

- [1] W. Chou, A. Kempitiya, et O. Vodyakho, « Reduction of Power Losses of SiC MOSFET Based Power Modules in Automotive Traction Inverter Applications », in 2018 IEEE Transportation Electrification Conference and Expo (ITEC), juin 2018, p. 1035-1038. doi: 10.1109/ITEC.2018.8450130.

- [2] J. Sun, H. Xu, X. Wu, and K. Sheng, « Comparison and analysis of short circuit capability of 1200V single-chip SiC MOSFET and Si IGBT, » in 2016 13th China International Forum on Solid State Lighting: International Forum on Wide Bandgap Semiconductors China (SSLChina: IFWS), 2016, pp. 42-45.

- [3] G. Romano et al., "Short-circuit failure mechanism of SiC power MOSFETs," 2015 IEEE ISPSD, Hong Kong

- [4] O. Aviñó Salvadó, H. Morel, C. Buttay, D. Labrousse, et S. Lefebvre, « Threshold voltage instability in SiC MOSFETs as a consequence of current conduction in their body diode », Microelectronics Reliability, vol. 88-90, p. 636-640, sept. 2018, doi: 10.1016/j.microrel.2018.06.033.

- [5] Y. Barazi et al., "CMOS Gate Driver with fast short circuit protection for SiC MOSFETs," 2020 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Vienna, Austria, 2020, pp. 94-97, doi: 10.1109/ISPSD46842.2020.9170164.

- [6] Jung-Woo Ha et al., "A Fast Response Integrated Current-Sensing Circuit for Peak-Current-Mode Buck Regulator", IEEE ESSCIRC 2014

- [7] A. Kumar, S. Bhattacharya, and J. Baliga, "Influence of the Inverter Dead-time on the Reverse Recovery Characteristics of 3.3-kV SiC MOSFETs and JBSFETs," in 2022 IEEE Energy Conversion Congress and Exposition (ECCE), Oct. 2022, pp. 1-7. doi: 10.1109/ECCE50734.2022.9947390.

- [8] J. Dyer, Z. Zhang, F. Wang, D. Costinett, L. M. Tolbert, et B. J. Blalock, « Dead-time optimization for SiC based voltage source converters using online condition monitoring », in 2017 IEEE 5th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), oct. 2017, p. 15-19. doi: 10.1109/WiPDA.2017.8170495.

- [9] Jiawei Li et al., "An Improved Desaturation Protection Method with Self-Adaptive Blanking-Time for Silicon Carbide (SiC) Power MOSFETs," 2021 IEEE (WiPDA) Asia.

- [10] Anas El Boubkari et al., "CMOS Gate Driver with Integrated Ultra-Accurate and Fast Gate Charge Sensor for Robust and Ultra-Fast Short Circuit Detection of SiC Power modules", 2023 IEEE ISPSD, Hong Kong

- [11] Eric Velander et al., "Analysis of Short Circuit type II and III of High Voltage SiC MOSFETs with Fast Current Source Gate Drive Principle", 2016 IEEE IPEMCECCE, Asia