# Système de mesure de la tension Drain-Source à l'état passant: application aux modules SiC forte tension

Antoine Laspeyres, Anne-Sophie Descamps, Christophe Batard et Nicolas Ginot

Nantes Université, CNRS, IETR, UMR 6164, F-44000 Nantes, France

**RESUME** – Cet article traite de la mesure en fonctionnement des paramètres électriques sensibles à la dégradation des semi-conducteurs de puissance menant à une approche de surveillance de l'état de santé du module de puissance. La résistance à l'état passant  $R_{DS_{ON}}$  est un indicateur de vieillissement clé des MOSFETs en carbure de silicium. Elle peut fournir des informations sur la dégradation de la puce et du boîtier afin de rendre un convertisseur de puissance plus fiable. Cette résistance à l'état passant peut être déterminée en utilisant à la fois le courant à l'état passant et la tension du semi-conducteur de puissance. Cet article propose un circuit de mesure de tension à l'état passant pour les modules haute puissance (jusqu'à 3.3 kV, 500 A). Le circuit proposé est validé lors d'un test double pulse pour différentes températures de semelle du module et comparé aux données obtenues avec un traceur de courbe Keysight B1505.

**Mots-clés** – Silicon carbide (SiC), Source Driver Topology, On-state voltage measurement circuit, Semiconductor device reliability

## 1. INTRODUCTION

Les MOSFET haute tension en carbure de silicium (SiC) offrent une vitesse de commutation ou une température de fonctionnement plus élevée que les composants de puissance à base de silicium (Si) [1]. Ces composants permettent alors d'augmenter l'efficacité des convertisseurs dans une large gamme d'applications telles que l'aérospatiale [2] ou les véhicules électriques [3]. Au cours des dernières années, de nouveaux smart gate drivers explorent les fonctionnalités de surveillance et de diagnostic de ces composants SiC, car elles jouent un rôle important pour les problèmes de fiabilité et peuvent être utilisés pour augmenter la durée de vie des semi-conducteurs de puissance [4].

Parmi les indicateurs de vieillissement, la résistance à l'état passant  $R_{DS_{ON}}$  est souvent utilisée car elle donne des informations à la fois sur l'état de santé de la puce semi-conductrice et de son environnement (délaminage des brasures au niveau des puces semi-conductrices, soulèvement des fils de liaison, etc.) [5]. L'acquisition du courant est souvent réalisée à l'aide d'un circuit externe au gate driver comme des sondes de rogowski [6]. La valeur de  $R_{DS_{ON}}$  est alors déduite de la chute de tension  $V_{DS_{ON}}$  aux bornes du composant de puissance.

### 1.1. Drain Voltage Clamping Circuits (DVCCs) conventionnels

En raison de l'écart entre la tension à l'état passant 0-3 V et la tension à l'état bloqué 1.2 kV-3.3 kV, les DVCCs sont utilisés pour bloquer la tension drain-source élevée du Device Under Test (DUT) [7].

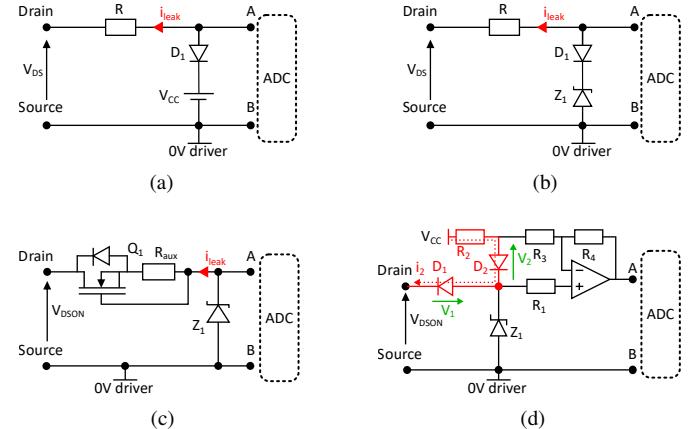

Les DVCCs peuvent être divisés en deux catégories : ceux utilisant une résistance comme le DVR ou le DZD et ceux utilisant un semi-conducteur comme le DTr ou le D2D. La figure 1 illustre ces 4 exemples. La solution proposée est basée sur la solution D2D.

De nombreuses études sur les DVCC ont été menées afin d'améliorer la bande passante et la précision des circuits de mesures [8] ou d'offrir une plage de température de fonctionnement plus large [9]. Néanmoins, tous les DVCC conventionnels bloquent uniquement le potentiel de drain du composant de

FIG. 1. Illustrations des DVCCs conventionnels. (a) DVR. (b) DZD. (c) DTr. (d) D2D.

puissance et supposent le potentiel de source fixe par rapport au 0 V driver. Rossetto et Spiazzi [10] ont cependant discuté du bruit généré par la commutation du dispositif de puissance SiC sur ce potentiel de source et de ses effets négatifs sur la mesure  $V_{DS_{ON}}$ . Ils proposent alors un circuit auxiliaire pour découpler le potentiel de référence du système de mesure du potentiel de mesure (potentiel de source).

### 1.2. Module de puissance

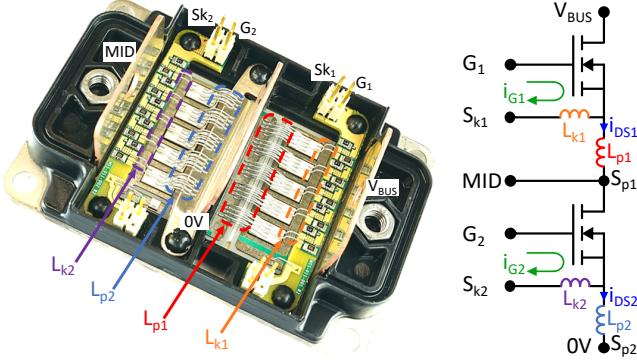

Les composants de puissance SiC permettent une fréquence de commutation plus élevée afin d'atteindre un rendement et une densité de puissance plus élevés que leur homologue Si [11]. Néanmoins, cela signifie que les éléments parasites du boîtier impactent davantage le convertisseur de puissance. Les oscillations de tension dues à la commutation du courant de charge sur les fils de liaison lors du blocage et de l'amorçage du semi-conducteur de puissance peuvent affecter la tension de grille. Ainsi, la connexion Kelvin sépare le chemin du courant de grille ( $i_{G_1}$  ou  $i_{G_2}$ ) du chemin du courant de charge ( $i_{DS_1}$  ou  $i_{DS_2}$ ) pour garantir un contrôle sûr du dispositif d'alimentation, comme illustré à la Fig. 2.

Comme le courant de charge circule dans les fils modélisés par  $L_{p1}$  et  $L_{p2}$ , les circuits de mesure  $V_{DS_{ON}}$  doivent les prendre en compte. Néanmoins, le gate driver étant connecté à la source Kelvin, les DVCCs classiques ne peuvent pas être utilisés car ils supposent que le potentiel de la source est directement connecté à la référence du gate driver.

### 1.3. Oscillations aux bornes des fils de liaison

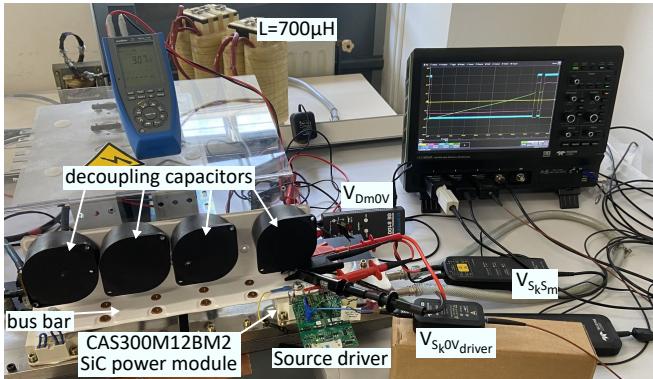

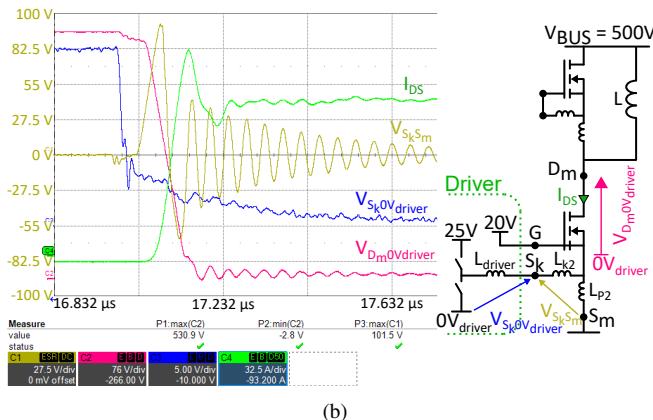

Afin de quantifier l'amplitude des oscillations de tensions aux bornes des fils de liaison  $S_k S_p$ , on effectue un essai double pulse sur un module SiC CAS300M12BM2. Le test se fait sous une tension de bus  $V_{BUS} = 500$  V. Toutes les tensions acquises lors du test sont illustrées à la figure 3b.

FIG. 2. Vue interne du module de puissance SiC CAB450M12XM3 1.2 kV-450 A du fabricant Wolfspeed

(a)

FIG. 3. Essai double pulse pour extraire les oscillations de tensions aux bornes des fils de liaison  $S_kS_p$  (a) Plateforme expérimentale. (b) forme d'ondes expérimentales à l'amorçage.

On utilise durant l'essai un source driver développé au sein du laboratoire IETR [12]. Comparé aux gate drivers conventionnels, le source driver fixe la grille du composant de puissance au potentiel 20 V. Le buffer connecté sur la source kelvin du composant de puissance va alors appliquer les potentiels 0/+25 V afin d'obtenir les tensions de commandes  $V_{GS}$  requises pour son pilotage (+20 V/-5 V). Cette topologie de commande a été développée afin de rendre les circuits de DESAT et d'estimation du courant de fuite de grille compatibles [12].

A partir des formes d'ondes de la figure 3b, on remarque que la tension de drain  $V_{D0V}$  présente des oscillations de tension de faible amplitude (10 V crête-à-crête). Dans le cas de la tension  $V_{Sksm}$  aux bornes des fils de liaison  $L_{p2}$ , on observe de fortes oscillations de tension (180 V). Ces oscillations fortes tensions doivent être bloquées pour protéger l'électronique de mesure.

## 2. SYSTÈME D'ACQUISITION DE DONNÉES NUMÉRIQUES PROPOSÉ

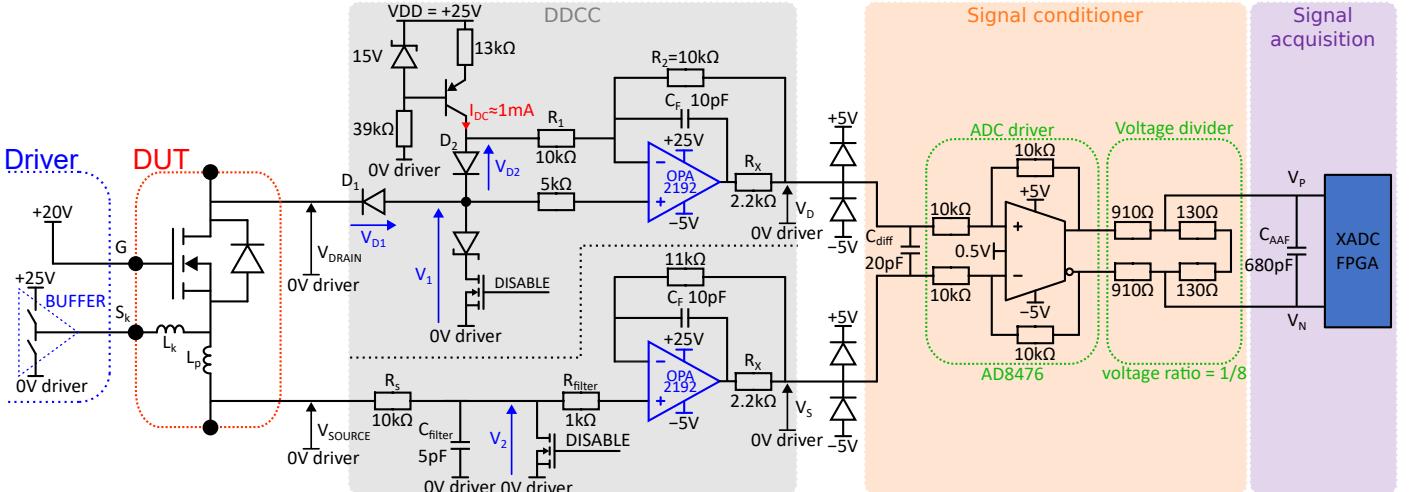

Nous nous concentrons sur un système d'acquisition de données numériques (Digital Data Acquisition System : DDAS) comprenant un circuit de blocage différentiel (Dual Differential Clamping Circuit : DDCC) pour module de puissance SiC moyenne tension (jusqu'à 3.3 kV) compatible avec la topologie du source driver [12]. Le DDAS complet avec son DDCC est présenté figure 4.

### 2.1. Description de la chaîne de mesure

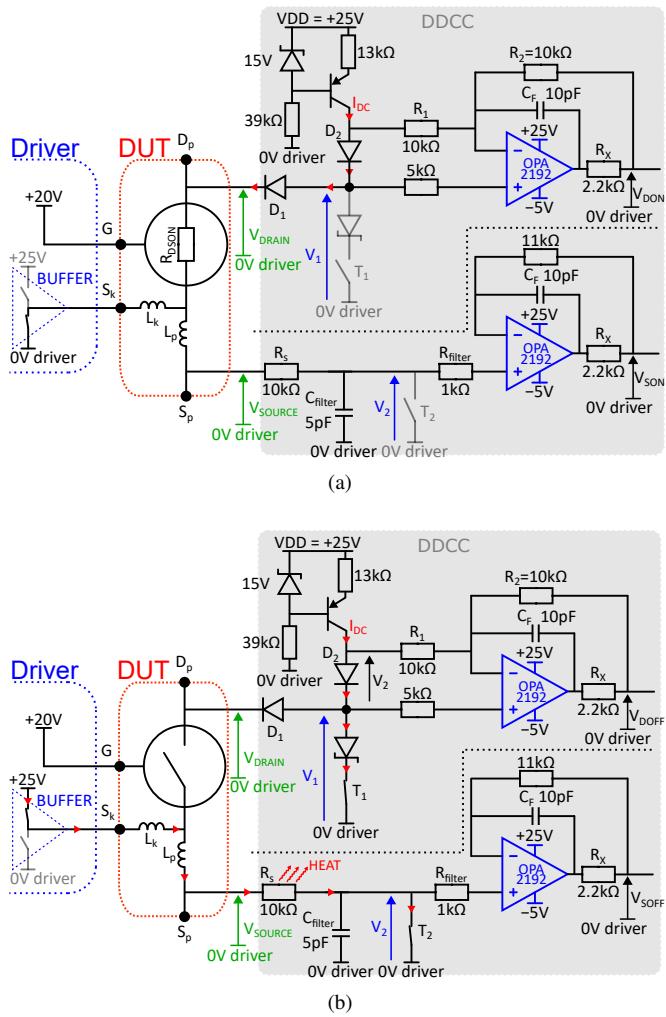

Le DDCC est composé de deux circuits DVCCs. Le circuit DVCC du drain (partie supérieure) utilise un D2D standard ( $D_1$  et  $D_2$  sur la figure 4). Le circuit DVCC de source (partie inférieure) utilise un DVCC basé sur une résistance ( $R_s$  sur la figure 4). Comme les oscillations de commutation de la tension  $V_{Sksm}$  peuvent atteindre des amplitudes de +150 V/-150 V, deux transistors  $T_1$  et  $T_2$  commandés par un signal "DISABLE" clampent les potentiels  $V_1$  et  $V_2$  afin de protéger le circuit conditionneur lorsque aucune mesure n'est requise.

Lorsque le composant de puissance est amorcé (figure 5a), le source driver fixe le potentiel de source kelvin au 0V driver. Le potentiel de drain  $V_{drain}$  peut être mesuré en compensant la chute de tension aux bornes de  $D_1$  [13]. L'équation (1) met en évidence le principe de compensation. Pour atténuer le problème de bruit thermique des circuits D2D dû aux diodes haute tension [7], les diodes  $D_1$  et  $D_2$  sont amorcées par une source de courant ( $I_{DC} \approx 1 \text{ mA}$ ). Le potentiel de source  $V_{source}$  peut être mesuré en compensant la chute de tension aux bornes des résistances  $R_s$  et  $R_{filter}$ .

$$V_{D_{ON}} = V_{DRAIN} + V_{D_1} - \frac{R_2}{R_1} \times V_{D_2} \quad (1)$$

Lorsque le semi-conducteur est bloqué (figure 5b), le source driver applique +25 V à la source Kelvin. Les deux transistors imposent les potentiels  $V_1$  et  $V_2$ . La diode de puissance  $D_1$  bloque la tension de drain. Comme la tension  $V_1$  est proche de 0 V, le circuit de compensation donne  $V_{D_{OFF}} = -V_{D_2}$ .  $T_2$  étant passant,  $R_s$  supporte la tension  $V_{S_{k0V}driver}$  (=+25 V). Une résistance de clamping  $R_s = 10 \text{ k}\Omega$  est utilisée pour limiter la puissance dissipée autour de la moitié de la puissance nominale des boîtiers des résistances 0805 SMT (i.e 62.5 mW).

### 2.2. Circuit conditionneur et d'acquisition numérique

Pour protéger les entrées de l'AD8476 pendant les mesures, les résistances  $R_X$  limitent le courant de sortie de l'amplificateur OPA2192 au cas où la tension de sortie atteindrait +25 V. Une résistance  $2.2 \text{ k}\Omega$  limite le courant autour de 1 mA. Pour éviter l'instabilité des circuits due aux résistances de limitation de courant  $R_X$  [14], des capacités de compensation  $C_F = 10 \text{ pF}$  sont insérées entre l'entrée inverseuse et la sortie de l'OPA2192. Leur valeurs sont calculées à partir de l'équation (2) avec  $R_0$ , la résistance de sortie de l'OPA2192.

$$C_F \geq \left( 1 + \frac{1}{\left| 1 + \frac{R_2}{R_1} \right|} \right) \left( \frac{R_1 + R_2}{R_2^2} \right) \cdot R_0 \cdot (2 C_{diff}) \quad (2)$$

Le FPGA Artix-7 de Xilinx intègre deux ADCs 12 bits, pouvant traiter 1 million d'échantillons par seconde (1MSPS). La plage d'entrée des ADCs peut être configurée en mode unipolaire de 0 V à 1 V ou en mode différentiel avec une plage de  $\pm 0.5 \text{ V}$  centrée autour de la valeur moyenne 0.5 V.

Afin de garantir une certaine immunité au bruit électromagnétique induit par la commutation des semi-conducteurs de puissance, une mesure différentielle a été privilégiée. Une paire différentielle est utilisée pour transporter le signal analogique

FIG. 4. Circuit DDAS proposé

FIG. 5. Schéma équivalent du DDCC (a) quand le DUT est amorcé (b) quand le DUT est bloqué

$V_{DS_{ON}}$  vers l'ADC. Le driver d'ADC (AD8476) dispose d'une broche pour régler la tension de mode commun de la sortie à une valeur de 0.5 V afin d'utiliser pleinement l'entrée différentielle de l'ADC. Ensuite, un diviseur de tension différentiel ajuste la plage  $V_{DS_{ON}}$  [+4 V/-4 V] à la plage d'entrée de l'ADC [+0.5 V/-0.5 V].

### 2.3. Contraintes temporelles liée à la mesure

Lorsque le contrôle commande nécessite une mesure de  $V_{DS_{ON}}$ , le FPGA synchronise le signal DISABLE du DDAS à la figure 4 sur les ordres de commande du semi-conducteur. Cela assure que les oscillations de tension à la commutation du composant ne saturent pas le circuit DDAS.

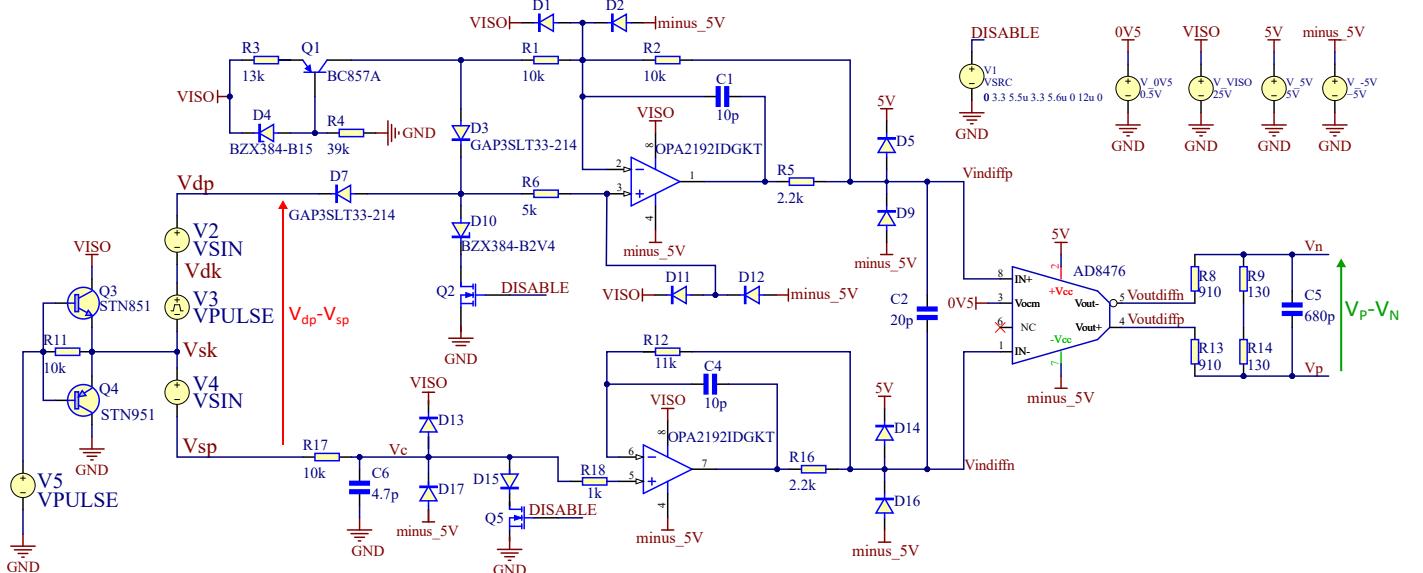

Afin de synchroniser les différentes constantes de temps du circuit, on vient émuler le DDAS à l'aide du logiciel Altium Designer. Le circuit de simulation est présenté figure 6. La mise sous tension du dispositif semi-conducteur de puissance est émulée à l'aide des sources de tension  $V_2$ ,  $V_3$  et  $V_4$ . On se base sur les résultats expérimentaux figure 3b.

La différence de potentiels  $D_k S_k$  ( $V_3$ ) est émulée par une pente linéaire de 2500 V à 2 V en 250 ns. Une forme d'onde de type sinusoïdale amortie ( $V_4$ ) émule l'oscillation de tension aux bornes des fils de liaison  $S_k S_m$  pendant la commutation. L'amplitude crête-à-crête des oscillations vaut 300 V. Le signal DISABLE est synchronisé sur les ordres de commande émulés par  $V_5$ . L'amplificateur push-pull  $Q_3/Q_4$  permet de simuler l'impact du source driver sur le potentiel  $S_k$ .

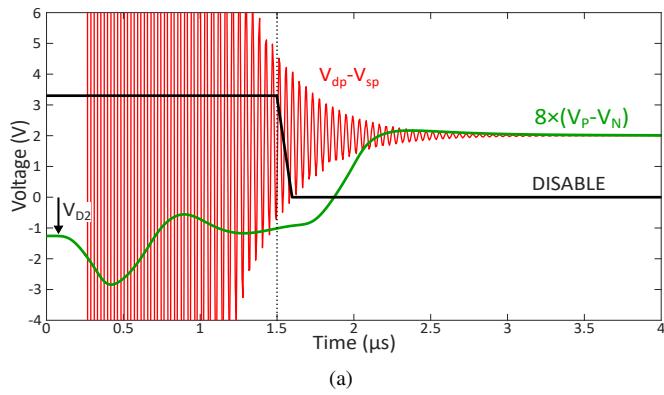

À partir des résultats de simulation figure 7a, le chronogramme du DDAS est présenté figure 7b. L'ouverture des transistors  $Q_2$  et  $Q_5$  (par la commande DISABLE) est effectuée après un temps de sécurité de 1.5 µs après l'ordre d'amorçage du semi-conducteur de puissance. Cela garantit une amplitude d'oscillation de tension  $V_{S_k S_p}$  inférieure à 5 V pour protéger l'AD8476. La tension de sortie du circuit  $8 \times (V_p - V_n)$  (courbe en vert) figure 7a commence à converger vers le mesurande  $V_{dp} - V_{sp}$  (courbe en rouge). D'après la simulation, le DDAS requiert 5 µs afin de garantir un écart  $\Delta$  entre la tension de sortie du circuit et le mesurande inférieure à la moitié de la résolution du circuit. En utilisant les entrées analogiques auxiliaires de l'ADC, Xilinx recommande un temps d'acquisition  $\geq 300$  ns. Un temps d'acquisition 500 ns est choisi. Le DDAS requiert un temps total de 7 µs pour effectuer une mesure de  $V_{DS_{ON}}$ .

### 3. MESURE DE LA TENSION DRAIN-SOURCE À L'ÉTAT PASSANT

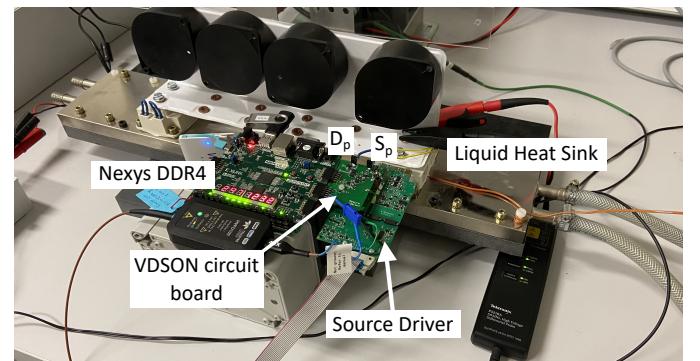

Le circuit DDAS est testé en fonctionnement sur un module de puissance SiC CAS300M12BM2. Le module est soumis à un test double pulse sous une tension continue  $V_{BUS} = 500$  V pour différentes températures de semelle du module. On utilise un capteur thermique Fluke pour surveiller la température de la semelle du module. La valeur de courant  $I_{DS}$  est acquise sur un oscilloscope à l'aide d'une sonde de Rogowski CWT 6R. La carte d'évaluation Nexys DDR4 basée sur Artix-7 FPGA est utilisée pour synchroniser le source driver et le signal DISABLE. L'ac-

FIG. 6. Simulation du DDAS dans Altium Designer

FIG. 7. (a) Formes d'ondes de la simulation Altium Designer. (b) Chronogramme du DDAS

quisition numérique des valeurs utilise l'ADC intégré à l'Artix-7. À la différence de la caractérisation, on récupère les valeurs mesurées à l'aide de l'afficheur 7 segments de la Nexys. La figure 8 illustre la plate-forme expérimentale.

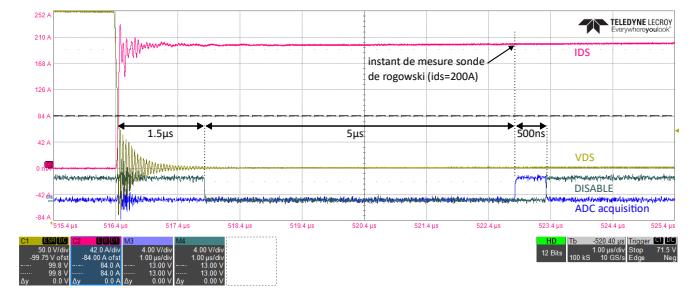

La figure 9 illustre quelques formes d'ondes de l'essai. On fait sortir du FPGA le signal *ADC acquisition* pour synchroniser l'instant de mesure du courant avec la sonde de rogowski avec celui du circuit. Sur les relevées à l'oscilloscope, le signal *DISABLE* tombe bien après la fin des oscillations de commutation ( $1.5\ \mu s$ ). Lors du test de double pulse, le DDAS parvient à acquérir la valeur  $V_{DS_{ON}}$  tout en supportant les oscillations de commutation.

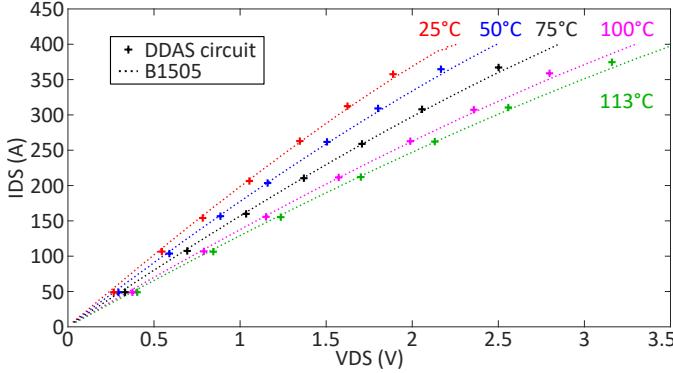

Les données acquises sont comparées à des mesures effectuées par un traceur de courbe Keysight B1505. La figure 10

FIG. 8. Banc de test expérimental du double pulse

FIG. 9. Formes d'ondes pertinentes des essais expérimentaux.  $T_{semelle} = 75^\circ C$ ,  $i_{DS} = 200 A$

compare les résultats des mesures hors tension au B1505 avec celles obtenues sous environnement de puissance. Les résultats du traceur sont affichés en lignes pointillées tandis que les résultats du DDAS sont affichés avec des croix. Lors du test double pulse, le DDAS réussit à bloquer les oscillations de commutation.

Le circuit DDAS donne des résultats proches de ceux du traceur B1505 sur toute la plage de température  $25^\circ C$  à  $113^\circ C$ . On remarque dans un premier temps que pour des valeurs de  $V_{DS}$  faible ( $< 1.5\ V$ ), le circuit surestime la valeur réelle. Au contraire, quand  $V_{DS}$  augmente, le circuit sous-estime la valeur réelle. Dans les deux cas de figure, l'erreur relative entre la valeur du DDAS et celle du B1505 reste dans la plage des  $+4\%/-4\%$ .

FIG. 10. Performances du circuit proposé pour plusieurs températures

#### 4. CONCLUSIONS

Cet article traite de la mesure en ligne des paramètres électriques sensibles à la dégradation menant à une approche de surveillance de l'état de santé du module de puissance.  $R_{DS_{ON}}$  est choisi comme indicateur de vieillissement pertinent à la fois pour le semi-conducteur de puissance et son boîtier. Cet article se focalise sur le circuit d'acquisition de la chute de tension  $V_{DS_{ON}}$  aux bornes du composant de puissance afin d'en déduire  $R_{DS_{ON}}$ . On propose un circuit de clamping qui résiste aux oscillations haute tension sur les fils de liaison des modules de puissance lors des commutations. Les mesures sous environnement de puissance sont comparées avec des mesures effectuées hors tension sur une large plage de température ( $25^{\circ}\text{C}$  -  $113^{\circ}\text{C}$ ).

Le circuit ayant pour finalité une intégration sur un module 3.3 kV, il devra être testé sur des modules de puissance SiC 1.7 kV et 3.3 kV avec une tension continue jusqu'à 2.5 kV afin de valider complètement son cahier des charges. De plus, une étude sur sa tenue en température devra valider sa fiabilité à haute température comme indiquée dans [9].

#### 5. RÉFÉRENCES

- [1] S. Ji, Z. Zhang, and F. Wang, "Overview of high voltage sic power semiconductor devices : development and application," *CES Transactions on Electrical Machines and Systems*, vol. 1, DOI [10.23919/TEMS.2017.8086104](https://doi.org/10.23919/TEMS.2017.8086104), no. 3, pp. 254–264, 2017.

- [2] L. Dorn-Gomba, J. Ramoul, J. Reimers, and A. Emadi, "Power electronic converters in electric aircraft : Current status, challenges, and emerging technologies," *IEEE Transactions on Transportation Electrification*, vol. 6, DOI [10.1109/TTE.2020.3006045](https://doi.org/10.1109/TTE.2020.3006045), no. 4, pp. 1648–1664, 2020.

- [3] F. Blaabjerg, H. Wang, I. Vernica, B. Liu, and P. Davari, "Reliability of power electronic systems for ev/hev applications," *Proc. IEEE*, vol. 109, DOI [10.1109/JPROC.2020.3031041](https://doi.org/10.1109/JPROC.2020.3031041), no. 6, pp. 1060–1076, 2021.

- [4] C. H. Van der Broeck, S. Kalker, and R. W. De Doncker, "Intelligent monitoring and maintenance technology for next generation power electronic systems," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, DOI [10.1109/JESTPE.2021.3119590](https://doi.org/10.1109/JESTPE.2021.3119590), pp. 1–1, 2021.

- [5] E. Ugur, F. Yang, S. Pu, S. Zhao, and B. Akin, "Degradation assessment and precursor identification for sic mosfets under high temp cycling," *IEEE Transactions on Industry Applications*, vol. 55, DOI [10.1109/TIA.2019.2891214](https://doi.org/10.1109/TIA.2019.2891214), no. 3, pp. 2858–2867, 2019.

- [6] W. Zhang, S. B. Sohid, F. Wang, H. Cui, and B. Holzinger, "High-bandwidth combinational Rogowski coil for sic mosfet power module," *IEEE Transactions on Power Electronics*, vol. 37, DOI [10.1109/TPEL.2021.3127545](https://doi.org/10.1109/TPEL.2021.3127545), no. 4, pp. 4397–4405, 2022.

- [7] B. Yu, L. Wang, and D. Ahmed, "Drain-source voltage clamp circuit for online accurate on-state resistance measurement of sic mosfets in dc solid-state power controller," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 8, DOI [10.1109/JESTPE.2019.2954038](https://doi.org/10.1109/JESTPE.2019.2954038), no. 1, pp. 331–342, 2020.

- [8] R. Gelagaev, P. Jacqmaer, and J. Driesen, "A fast voltage clamp circuit for the accurate measurement of the dynamic on-resistance of power transistors," *IEEE Transactions on Industrial Electronics*, vol. 62, DOI [10.1109/TIE.2014.2349876](https://doi.org/10.1109/TIE.2014.2349876), no. 2, pp. 1241–1250, 2015.

- [9] B. Yu and L. Wang, "Online accurate measurement of steady-thermal resistance of sic mosfets for dc solid-state power controller," *IEEE Transactions on Power Electronics*, vol. 36, DOI [10.1109/TPEL.2020.3028844](https://doi.org/10.1109/TPEL.2020.3028844), no. 5, pp. 5006–5021, 2021.

- [10] L. Rossetto and G. Spiazzini, "A fast on-state voltage measurement circuit for power devices characterization," *IEEE Transactions on Power Electronics*, vol. 37, DOI [10.1109/TPEL.2021.3129613](https://doi.org/10.1109/TPEL.2021.3129613), no. 5, pp. 4926–4930, 2022.

- [11] N. Baker, F. Iannuzzo, and H. Li, "Impact of kelvin-source resistors on current sharing and failure detection in multichip power modules," in *2018 20th European Conference on Power Electronics and Applications (EPE'18 ECCE Europe)*, pp. P.1–P.7, 2018.

- [12] A. Laspeyres, L. Makki, C. Darbas, A.-S. Descamps, C. Batard, N. Ginot, S. Azzopardi, T. Long Le, and T. Youssef, "An improved monitoring of gate leakage current on SiC Power MOSFETs using source driver topology," in *PCIM Europe Conference*, Nuremberg, Germany, May. 2022.

- [13] M. Guacci, D. Bortis, and J. W. Kolar, "On-state voltage measurement of fast switching power semiconductors," *CPSS Transactions on Power Electronics and Applications*, vol. 3, DOI [10.24295/CPSSTPEA.2018.00016](https://doi.org/10.24295/CPSSTPEA.2018.00016), no. 2, pp. 163–176, 2018.

- [14] S. Bendaoud and G. Marino, "Practical Techniques to Avoid Instability Due to Capacitive Loading," Tech. Rep. Volume 38-02, June 2004.