# Optimisation multi-objectifs pour le réglage de l'inductance de fuite d'un transformateur planar

Gautier CORGNE<sup>1</sup>, Reda BAKRI<sup>1,2</sup>, Xavier MARGUERON<sup>1</sup>, Frédéric GILLON<sup>1</sup>

<sup>1</sup> Univ. Lille, Arts et Metiers Institute of Technology, Centrale Lille, Junia, ULR 2697 - L2EP, F-59000 Lille, France

<sup>2</sup> Univ. Lille, Arts et Metiers Institute of Technology, Centrale Lille, Junia, HESAM Université, ULR 2697, L2EP, F-59000 Lille, France

**RESUME** – L'inductance de fuite est un paramètre essentiel des transformateurs HF dans les convertisseurs DC/DC isolés. Avec l'utilisation de la technologie planar et des enroulements en PCB, ce paramètre peut être réglé à une valeur pré-déterminée en ajustant le positionnement des conducteurs dans la fenêtre des transformateurs. Cet article présente une étude autour de la minimisation, de la maximisation et du réglage de l'inductance de fuite d'un transformateur planar. La méthodologie développée est basée sur des simulations par éléments finis (FEM) couplées avec un algorithme d'optimisation multi-objectifs qui permettent de régler une inductance à une valeur donnée, tout en minimisant les pertes cuivre induites.

**Mots-clés**—Transformateur planar, HF, inductance de fuite, pertes cuivre, optimisation.

## 1. INTRODUCTION

L'estimation précise de l'inductance de fuite est primordiale dans le dimensionnement d'un transformateur haute-fréquence (HF) pour les convertisseurs DC/DC isolés. En effet, suivant le type de convertisseur, la valeur de ce paramètre doit être minimisée pour éviter des pertes supplémentaires ou, au contraire, réglée à une certaine valeur pour servir de réserve d'énergie dans des applications à commutation douce ou pour certaines topologies spécifiques [1]. Dans une optique de minimisation de la masse et du volume d'un convertisseur, l'intégration de l'inductance de résonnance dans les fuites d'un transformateur permet d'éviter d'avoir recours à une inductance supplémentaire [1, 2].

Les composants magnétiques planar sont de plus en plus utilisés dans les convertisseurs HF DC/DC, en raison notamment de leur compacité, de leurs bonnes performances électriques et thermiques, ainsi que la répétabilité de leurs paramètres [3, 4]. L'inductance de fuite de ce type de transformateur est connue pour être relativement faible [5]. De nombreux modèles sont développés dans la littérature pour prédire leur valeur sur la plage de fonctionnement des convertisseurs [6-8]. Il est aussi possible d'augmenter leur valeur d'inductance de fuite en rajoutant une couche de fuite basée sur un matériaux de type ferrite souple [9, 10]. Ceci implique une modification de la structure complète du circuit imprimé (PCB).

Cet article propose d'étudier les possibilités de réglage de l'inductance de fuite ( $L_{lk}$ ) d'un transformateur planar, en agissant sur le positionnement des conducteurs dans le PCB. Après avoir présenté le cas d'étude, les plages de variations de l'inductance de fuite seront étudiées, sur la base de simulation éléments-finis (FEM) réalisées via le logiciel FEMM [11], pour différents entrelacements. Dans la dernière partie, des optimisations multi-

objectifs seront réalisées pour régler l'inductance de fuite une valeur donnée, tout en minimisant les pertes cuivre engendrées.

## 2. DESCRIPTION DU CAS D'ETUDE ET CONTRAINTES

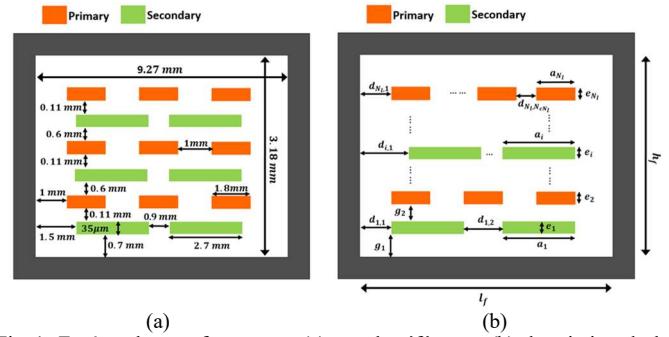

Le transformateur planar à 2 enroulements servant de support à cette étude est basé sur un noyau planar E/PLT32 [12]. Le PCB est constitué de 6 couches de 35µm d'épaisseur. Le primaire (P) contient 9 spires réparties sur 3 couches tandis que le secondaire (S) possède 6 spires, elles aussi réparties sur 3 couches. Ce stackup est facilement réalisable chez un fabricant de PCB. La Fig.1a présente une coupe d'une fenêtre de bobinage. Sur cette figure, les conducteurs sont centrés dans la fenêtre. Ce cas sera appelé cas de référence dans la suite de l'article. Son inductance de fuite sera notée  $L_{lkref}$  et ses pertes cuivre  $R_{acref}$ . Les couches de conducteurs sont entrelacées au maximum sur cette figure: PSPSPS. Cet entrelacement est connu pour minimiser l'inductance de fuite et les pertes cuivre.

Fig. 1. Fenêtre de transformateur : (a) cas de référence, (b) description de la fenêtre avec variables

La Fig.1b illustre les différentes variables susceptibles d'évoluer dans la fenêtre du transformateur planar. Une étude de sensibilité a permis d'établir que les paramètres les plus influents sur la valeur de l'inductance de fuite sont les variables  $d_{i,j}$ , représentant l'écartement horizontal entre les conducteurs, et entre noyau et conducteurs de la couche  $i$ , ainsi que l'écartement vertical  $g_k$  pour  $k \in [2,6]$ . Ce dernier paramètre étant fixé par les fabricants de PCB multicouches, la variable d'optimisation  $d_{i,j}$  a été retenue pour cette étude. L'influence des entrelacements sera également étudiée mais le paramètre d'optimisations restera inchangé.

Les équations (1) et (2) présentent les fonctions contraintes induites par la géométrie présentée sur la Fig.1b, afin d'assurer une distance minimale  $d_{min1}$  entre le noyau et le premier conducteur de chaque couche, ainsi que  $d_{min2}$  entre deux conducteurs successifs.

$$(1 \dots 1).D_i \leq l_f - N_{ci} \cdot a_i - d_{min1} \quad (1)$$

$$-D_i \leq \begin{pmatrix} d_{min1} \\ d_{mi} \\ \dots \\ d_{min2} \end{pmatrix} \quad (2)$$

avec  $D_i$  le vecteur d'optimisation comprenant les distances de la couche  $i$ ,  $N_{ci}$  le nombre de conducteurs de la couche  $i$ , et  $a_i$  et  $l_f$  définis comme sur la Fig.1b.

### 3. MINIMISATION ET MAXIMISATION DE L'INDUCTANCE DE FUITE

Les équations (3) et (4) présentent les fonctions objectifs des optimisations permettant respectivement de minimiser et de maximiser l'inductance de fuite.

$$\min L_{lk} \quad (3)$$

$$\min -L_{lk} \quad (4)$$

avec  $L_{lk}$  l'inductance de fuite obtenue par simulation numérique.

#### 3.1. Entrelacement de référence PSPSPS

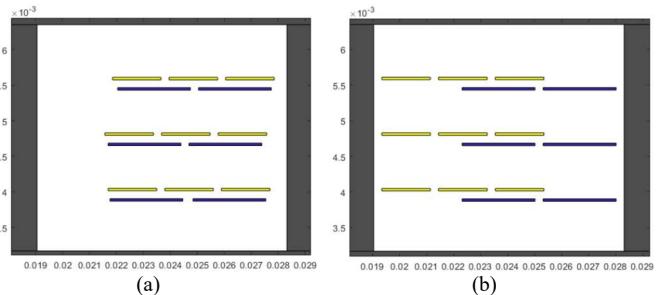

Le Tableau 1 présente les résultats de la minimisation et de la maximisation de l'inductance de fuite en basse fréquence (BF) (i.e. sans courants induits), à 100kHz et à 1 MHz, pour l'entrelacement PSPSPS (Fig.1). Alors que le cas de référence PSPSPS, avec conducteurs centrés, est connu pour minimiser la valeur de  $L_{lk}$ , il est possible, en BF comme en HF, de diminuer davantage celle-ci. Concernant la maximisation, elle est possible au prix d'une forte augmentation de la résistance des conducteurs ( $R_{ac}$ ), et donc des pertes cuivre en HF (Tableau 2). La Fig.2 présente la disposition des conducteurs dans la fenêtre du transformateur après minimisation (a) et maximisation (b) pour une fréquence d'1MHz. Les résultats de l'optimisation en BF et à 100kHz présentent des dispositions similaires.

Tableau 1. Résultats de l'optimisation simple objectif en BF, à 100kHz et à 1MHz

|                             | Minimisation | Maximisation |

|-----------------------------|--------------|--------------|

| $L_{lk}/L_{lkref}$ en BF    | 0.4          | 15           |

| $L_{lk}/L_{lkref}$ à 100kHz | 0.5          | 13           |

| $L_{lk}/L_{lkref}$ à 1MHz   | 0.8          | 9.0          |

Tableau 2. Pertes cuivre associées aux optimisations à 100kHz et 1MHz

|                             | Minimisation | Maximisation |

|-----------------------------|--------------|--------------|

| $R_{ac}/R_{acref}$ à 100kHz | 0.95         | 2.43         |

| $R_{ac}/R_{acref}$ à 1MHz   | 0.82         | 4.85         |

Fig. 2. Résultat de l'optimisation mono-objectif à 1MHz : (a) minimisation, (b) maximisation

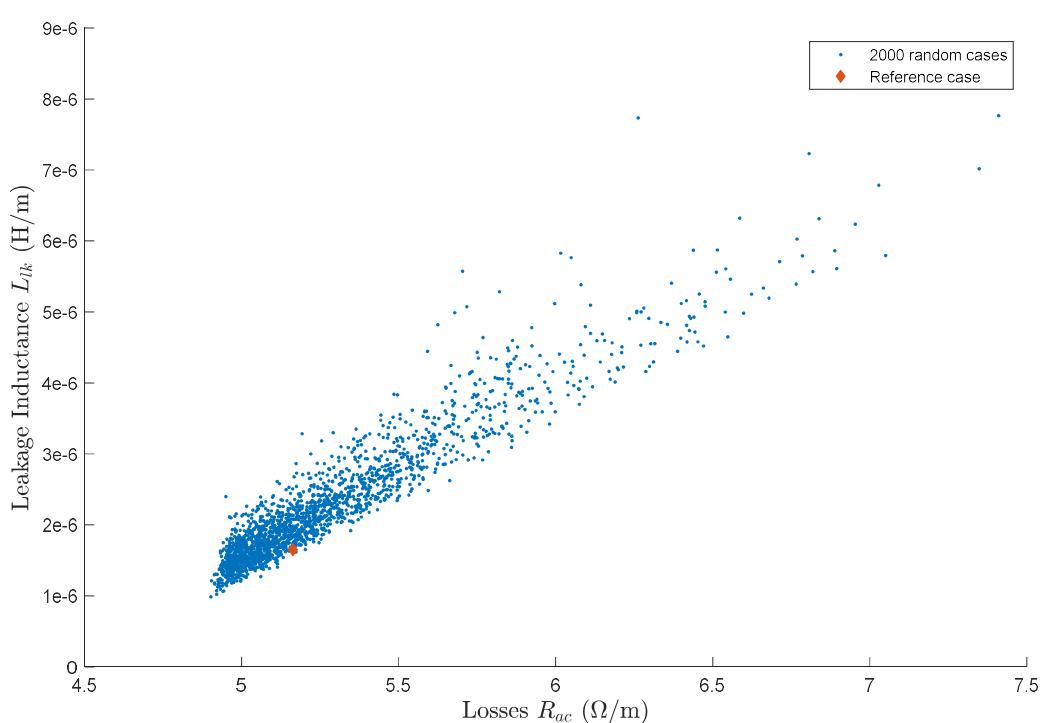

Avant de procéder au réglage de  $L_{lk}$  par optimisation, 2000 simulations FEM sont lancées de manière aléatoire, pour une fréquence de 100 kHz, en respectant les contraintes géométriques décrites par les équations (1) et (2). Pour chaque simulation, l'inductance de fuite par unité de longueur et la résistance série AC par unité de longueur, équivalente aux pertes cuivre, sont calculées. Les 2000 points sont reportés sur la Fig.3 avec le cas de référence (point rouge).

Fig. 3. Inductance de fuite  $L_{lk}$  en fonction des pertes cuivres – 2000 points aléatoires à 100 kHz

Ces simulations montrent :

- Que la plage de variation de l'inductance de fuite, avec cet empilement est assez grande, conformément aux résultats présentés en Table I.

- Que pour une valeur d'inductance de fuite fixée, différents positionnements des conducteurs sont possibles.

- En maintenant la valeur de l'inductance de fuite du cas de référence, il est possible de réduire les pertes cuivre en jouant sur le positionnement des conducteurs. Ceci peut être réalisé par optimisation multi-objectifs.

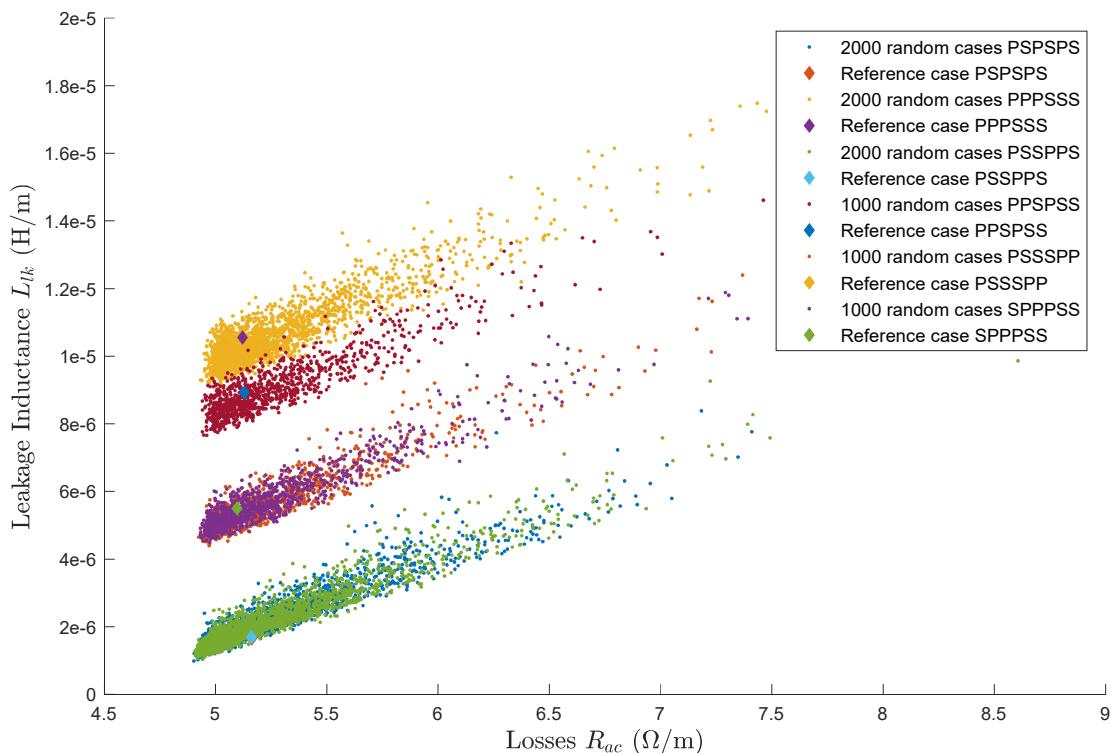

### 3.2. Influence des entrelacements

La Fig.4 présente un nuage de points obtenu avec la même méthode que pour la Fig.3 mais en faisant varier les

entrelacements. En effet, le cas d'étude à 6 couches permet la réalisation de six entrelacements différents : PSPSPS, PPPSSS, PSSPPSS, PPSPSS, PSSSPP et SPPPSS. Le cas de référence est toujours celui où les conducteurs sont centrés avec les écartements présentés sur la Fig.1a.

Les observations sont encore valables en modifiant l'entrelacement. Ainsi, pour chaque entrelacement, il est possible de réduire la valeur de l'inductance de fuite en comparaison avec le cas de référence. Il semble également toujours possible de trouver, pour chaque entrelacement, une inductance de fuite identique au cas de référence avec des pertes cuivre moindres.

Fig. 4. Inductance de fuite  $L_{fk}$  en fonction des pertes cuivres avec différents entrelacements à 100kHz

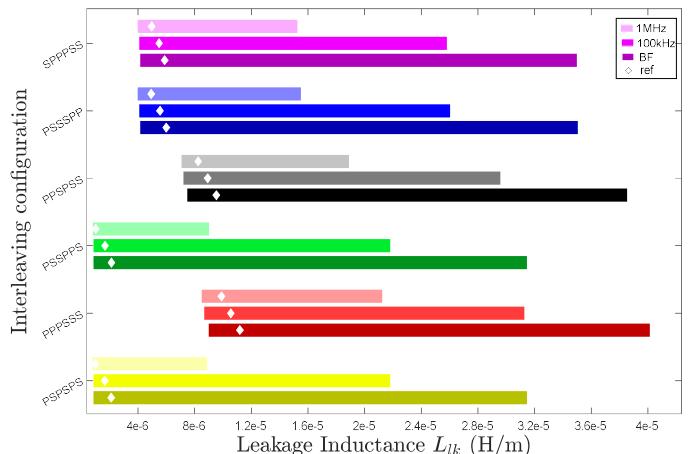

La Fig.5 présente les résultats de l'optimisation mono-objectif réalisée en BF, à 100kHz puis à 1MHz avec les six entrelacements possibles.

La valeur de l'inductance de fuite varie en fonction de la fréquence. De nombreuses configurations d'enroulement (positionnement & entrelacement) permettent d'obtenir une même valeur de  $L_{fk}$ . Par conséquent, il est nécessaire d'intégrer un second objectif de minimisation des pertes cuivre afin d'extraire la configuration la plus intéressante pour une valeur de  $L_{fk}$  donnée. Ceci peut permettre à un concepteur d'avoir recours à des agencements de conducteurs moins conventionnels lors de la phase de dimensionnement, permettant ainsi d'obtenir des transformateurs planar avec de meilleures performances.

Fig. 5. Plage de variation de l'inductance de fuite en BF, à 100kHz et 1MHz

#### 4. REGLAGE DE L'INDUCTANCE DE FUITE ET MINIMISATION DES PERTES CUIVRE

Pour cette partie de l'étude, les contraintes du problème d'optimisation restent inchangées (Equations (1) et (2)). Deux méthodes d'optimisation multi-objectifs ont été implémentées pour assurer la fiabilité des résultats obtenus. La première est la méthode « epsilon-contrainte » qui a été implémentée en réglant l'inductance de fuite (5) à pas fixe  $p$  entre ses valeurs minimale et maximale atteignables dans l'entrelacement considéré. Pour chaque pas, cent points de départ aléatoires ont été définis et l'optimisation retenue est celle présentant le moins de pertes cuivre. La seconde méthode implémentée est une méthode des moindres carrés, dont la fonction objectif est présentée en (6). Elle permet le réglage de l'inductance de fuite à une valeur fixée  $L_{lkreg}$  tout en minimisant les pertes cuivre.

$$\min |L_{lk} - (L_{lkmin} + p)| \quad (5)$$

$$\min - \left( (L_{lk} - L_{lkreg}) \cdot \frac{2}{L_{lkmin} + L_{lkmax}} \right)^2 + \left( R_{ac} \cdot \frac{2}{R_{acmin} + R_{acmax}} \right)^2 \quad (6)$$

avec  $L_{lk}$  et  $R_{ac}$  l'inductance de fuite et la résistance AC, image des pertes cuivre, obtenues par simulation numérique.  $L_{lkmin}$ ,  $L_{lkmax}$ ,  $R_{acmin}$  et  $R_{acmax}$  sont respectivement les valeurs minimum et maximum de  $L_{lk}$  et celles de  $R_{ac}$ .

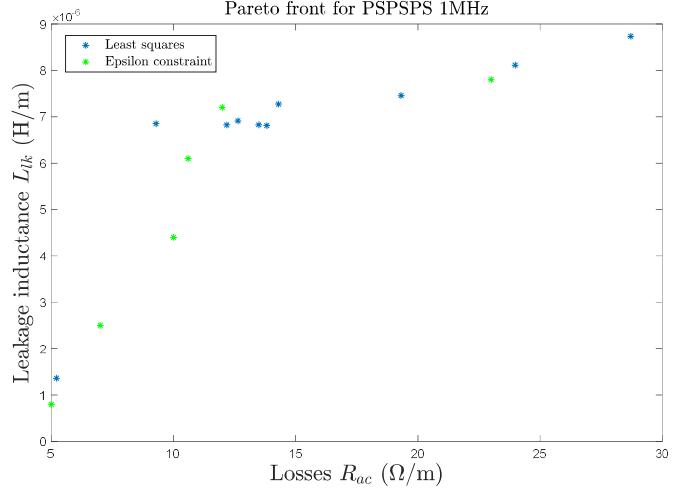

La Fig.6 présente la superposition des résultats obtenus, pour 1 MHz (entrelacement PSPSPS), à l'issue des optimisations avec les deux méthodes présentées précédemment. Le cinquième point obtenu avec la méthode epsilon-contrainte a été ajouté par une simulation supplémentaire, offrant un résultat dans la zone la plus intéressante. En effet, la forme de coude obtenue permet d'obtenir une zone dans laquelle le ratio inductance de fuite sur résistance AC est élevé. Le point ainsi ajouté, permet d'obtenir environ 90% de la valeur de l'inductance de fuite maximale avec cet entrelacement, le tout avec 2.5 fois moins de pertes cuivre que la configuration maximisant l'inductance. Pour la méthode des moindres carrés, les points ont été volontairement resserrés, dans la même zone, pour les mêmes raisons, faisant ainsi émerger le second point du front qui offre également un compromis intéressant.

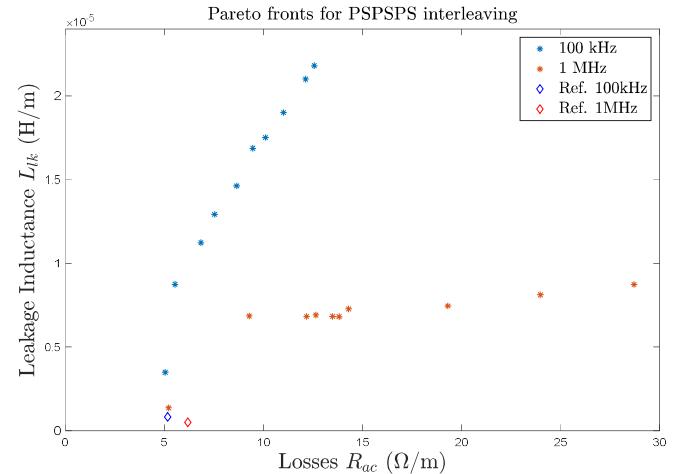

La méthode des moindres carrés a ensuite été appliquée pour deux fréquences différentes, 100kHz et 1MHz, toujours dans le cas de l'entrelacement PSPSPS. Les résultats obtenus sont comparés, sur la Fig.7, aux cas de référence. L'optimisation proposée permet de trouver des configurations qui réduisent les pertes pour offrir une plus grande inductance de fuite que le cas de référence avec les conducteurs centrés.

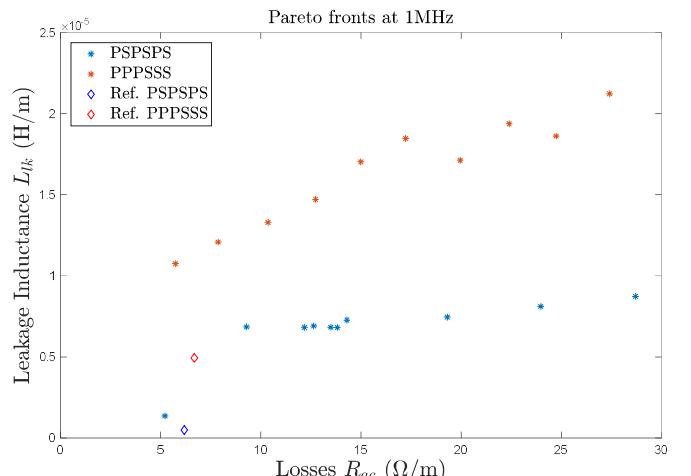

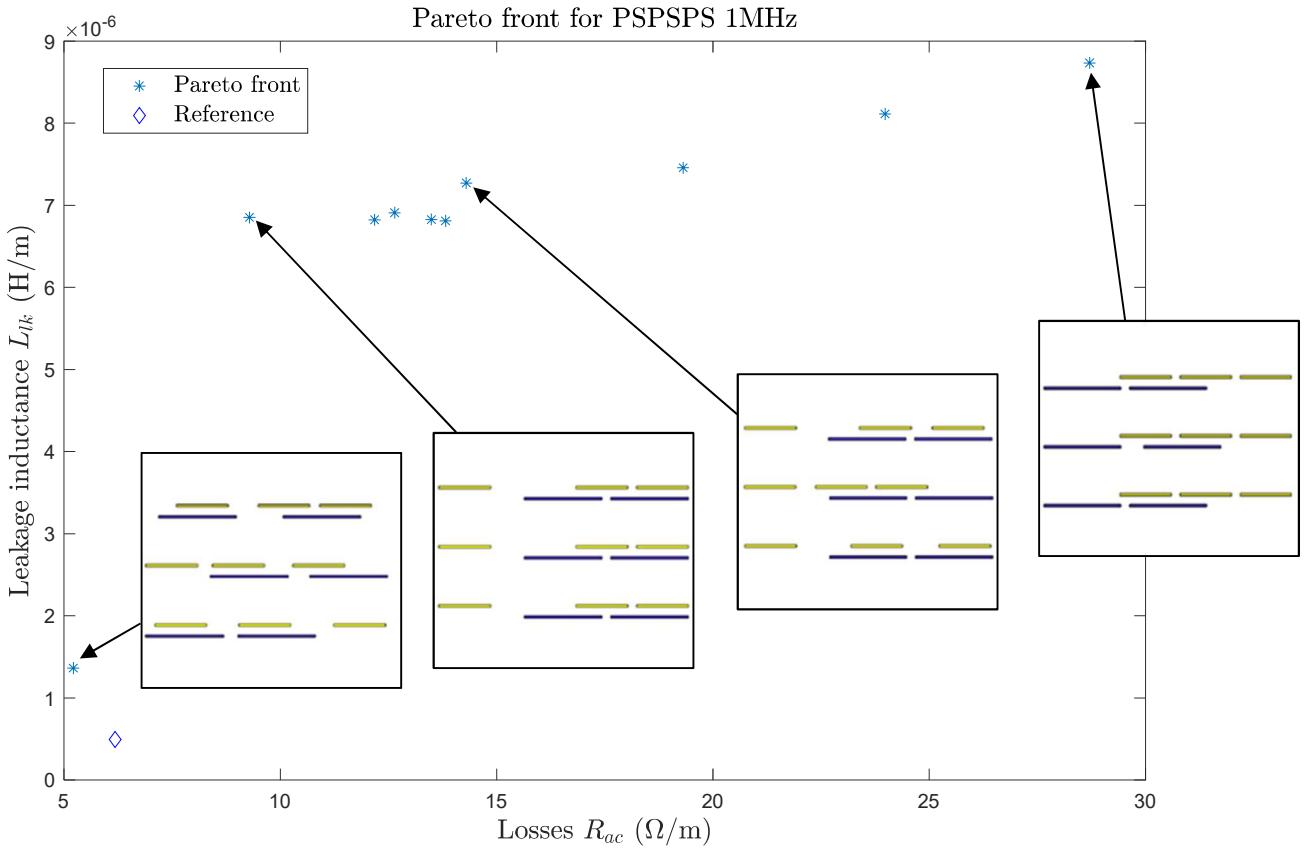

Dans un dernier temps, des fronts de Pareto ont été tracés pour différents entrelacements, permettant de trouver le meilleur compromis entrelacement & positionnement. La Fig.8 présente la superposition des fronts à 1MHz pour les entrelacements PSPSPS et PPPSSS. Cette superposition met à nouveau en avant la possibilité, à pertes constantes, de multiplier par un facteur 5 l'inductance de fuite. Enfin, la Fig.9 présente le front de Pareto à 1MHz pour l'entrelacement PSPSPS avec le positionnement optimal des conducteurs pour 4 situations sélectionnées : le premier point, le dernier point, et deux points intermédiaires du front.

Même en HF et avec tous les entrelacements, les configurations minimisant et maximisant l'inductance de fuite semblent uniques et sont celles déterminées par optimisation en

BF. Ainsi, dans ces cas précis, il apparaît que les optimisations exploitant des modèles analytiques BF, comme celui développé dans [6] par exemple, offrent le meilleur compromis avec un temps de calcul nettement inférieur à l'optimisation par simulation numérique.

Fig. 6. Fronts de Pareto à 1MHz avec entrelacement PSPSPS obtenus par la méthode epsilon-contrainte et celle des moindres carrés

Fig. 7. Fronts de Pareto à 100kHz et 1MHz avec entrelacement PSPSPS obtenus par la méthode des moindres carrés

Fig. 8. Fronts de Pareto à 1MHz avec entrelacements PSPSPS et PPPSS

Fig. 9. Front de Pareto à 1MHz avec entrelacement PSPSPS et positionnement des conducteurs dans la fenêtre pour 4 points du front

## 5. CONCLUSIONS

L'inductance de fuite des transformateurs est un paramètre important dans le dimensionnement d'un convertisseur DC/DC. Des solutions pour régler la valeur de ce paramètre, le minimiser ou le maximiser ont été investiguées dans le cas d'un transformateur planar. Avec un seul paramètre géométrique qui est le positionnement des conducteurs sur les couches du PCB, il est déjà possible de faire évoluer fortement les valeurs de l'inductance de fuite. Ce réglage, associé à une minimisation des pertes cuivre à HF au sein d'une optimisation multi-objectifs permet de tracer plusieurs fronts de Pareto avec les différents entrelacements possibles. Pour une fréquence de travail donnée, le concepteur d'un transformateur planar peut ainsi obtenir différents positionnements, pour chaque entrelacement, afin de choisir un bon compromis entre inductance de fuite et pertes cuivre.

## 6. REFERENCES

- [1] J. Ferrell, J. .-S. Lai, T. Nergaard, X. Huang, L. Zhu and R. Davis, "The role of parasitic inductance in high-power planar transformer design and converter integration," Nineteenth Annual IEEE Applied Power Electronics Conference and Exposition, 2004. APEC '04., Anaheim, CA, USA, 2004, pp. 510-515 Vol.1.

- [2] J. M. Cho, B. J. Byen, Y. J. Lee, D.-H. Han, H.-S Kho and G.-H. Choe, "Design of leakage inductance in resonant DC-DC converter for electric vehicle charger," IEEE Trans. Magn., vol. 48, no. 11, pp. 4417-4420, Nov. 2012.

- [3] Z. Ouyang and M. A. E. Andersen, "Overview of Planar Magnetic Technology – Fundamental Properties," IEEE Transactions on Power Electronics, vol. 29, no. 9, pp. 4888-4900, Sept 2014.

- [4] J. S. Ngoua Teu Magambo et al., "Planar Magnetic Components in More Electric Aircraft: Review of Technology and Key Parameters for DC-DC Power Electronic Converter," in IEEE Transactions on Transportation Electrification, vol. 3, no. 4, pp. 831-842, Dec. 2017.

- [5] B.W. Carsten, "The low leakage inductance of planar transformers: fact or myth?," APEC 2001. Sixteenth Annual IEEE Applied Power Electronics Conference and Exposition (Cat. No.01CH37181), vol. 2, pp. 1184-1188, 2001.

- [6] X. Margueron, A. Besri, P. -O. Jeannin, J. -P. Keradec and G. Parent, "Complete Analytical Calculation of Static Leakage Parameters: A Step Toward HF Transformer Optimization," in IEEE Transactions on Industry Applications, vol. 46, no. 3, pp. 1055-1063, May-june 2010.

- [7] R. Schlesinger and J. Biela, "Comparison of Analytical Models of Transformer Leakage Inductance: Accuracy Versus Computational Effort," in IEEE Transactions on Power Electronics, vol. 36, no. 1, pp. 146-156, Jan. 2021.

- [8] Z. Ouyang, W. G. Hurley and M. A. E. Andersen, "Improved Analysis and Modeling of Leakage Inductance for Planar Transformers," in IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 7, no. 4, pp. 2225-2231, Dec. 2019.

- [9] J. Zhang, Z. Ouyang, M. C. Duffy, M. A. E. Andersen and W. G. Hurley, "Leakage Inductance Calculation for Planar Transformers With a Magnetic Shunt," in IEEE Transactions on Industry Applications, vol. 50, no. 6, pp. 4107-4112, Nov.-Dec. 2014.

- [10] W. Tan, X. Margueron, L. Taylor, and N. Idir, "Leakage Inductance Analytical Calculation for Planar Components with Leakage Layers," IEEE Transactions on Power Electronics, vol. 31, no. 6, pp. 4462-4473, June 2016.

- [11] 'FEMM, Finite Element Method Magnetics', version 4.2, User's manual, may 2020. Available at <https://www.femm.info/wiki/HomePage>

- [12] 'Soft ferrites and accessories data handbook 2013'. Available at <https://www.ferroxcube.com/en-global/download/download/11>