# Développement d'un banc d'essai séquentiel statique et dynamique pour transistors de puissance Grand Gap en environnement sévère

Cyril CHABOT, Marc ORSATELLI, Emmanuel MARCAULT, Alonso GUTIERREZ, Mathieu GAVELLE

CEA, Commissariat à l'Energie Atomique et aux Energies Alternatives, 51 rue de l'Innovation, 31670 Labège

**RESUME –** Les transistors de puissance GaN HEMT présentent des performances très intéressantes en comparaison avec leur équivalent en Silicium. Néanmoins, les méthodologies d'essais de robustesse et fiabilité de ces dispositifs sont encore en cours de développement et parfois héritées des technologies Si, pouvant potentiellement ne pas être adaptées au fonctionnement réel des composants GaN HEMT. Ainsi, afin d'évaluer la robustesse de ces dispositifs dans des conditions proches de leur application, un banc dédié aux essais séquentiels statiques et dynamiques en environnement sévère a été développé. Ce banc permet de réaliser des essais en commutation avec un suivi périodique d'indicateurs statiques de performance en déportant le transistor au sein d'une enceinte. Cette méthode permet de n'évaluer que le composant GaN HEMT et non les autres éléments constituant le banc d'essai potentiellement sensibles à l'environnement sévère du test.

**Mots-clés—**Grand Gap, GaN HEMT, commande éloignée, commutation, mesure dynamique

## 1. INTRODUCTION

Les transistors de puissance basés sur la technologie GaN HEMT (High-Electron-Mobility Transistor) démontrent des performances très intéressantes pour des utilisations à fréquence élevée, au sein d'application de conversion de puissance dans plusieurs domaines. De plus, les dispositifs GaN HEMT semblent présenter des dispositions intrinsèques de robustesse aux radiations, et sont particulièrement intéressants pour les applications spatiales<sup>[1]</sup>. Du fait du récent essor de cette technologie, les méthodologies utilisées pour les essais de vieillissement accéléré ou de robustesse en environnement sévère ont été héritées des technologies usuelles en Silicium.

Cependant, de par leur fonctionnement spécifique et leur utilisation à des fréquences bien plus élevées que leur équivalent en Si, la question de la pertinence de l'utilisation des méthodologies d'essais héritées des technologies Si pour évaluer les dispositifs de puissance GaN HEMT se pose<sup>[1]</sup>. Ainsi, la problématique de réaliser des essais de vieillissement et de robustesse en environnement sévère dans des conditions proches des applications visées, en commutation notamment, doit être explorée. Des développements de méthodologies spécifiques sont en cours, notamment par le JEDEC et l'IEC qui proposent des méthodes d'essai de fiabilité spécifiques aux composants GaN HEMT<sup>[2][3]</sup>.

Le banc d'essai présenté ici permet de faire commuter les dispositifs en « hard-switching », d'évaluer les indicateurs de performances usuels (par exemple, les courants de fuite  $I_{GSS}$ ,  $I_{DSS}$ , la tension de seuil  $V_{TH}$ , etc.), tout en déportant le transistor de puissance des autres éléments du système (commande de grille, alimentation, sondes et équipements de mesure, charge etc.), ce qui permet de n'exposer que les transistors à l'environnement sévère (par exemple, température, vide, radiation), le reste du banc demeurant à l'extérieur d'une enceinte. Ce banc a été développé dans le cadre d'un projet mené avec le CNES. Les résultats des campagnes d'essais issus de ce projet seront présentés par le CNES à la conférence RADECS 2023. Sont uniquement présentés ici le fonctionnement et les performances du banc.

## 2. DEVELOPPEMENT DU BANC D'ESSAIS DEPORTE POUR TRANSISTORS DE PUISSANCE EN COMMUTATION

### 2.1. Contexte et enjeux

Le principal objectif de ce projet est d'évaluer la robustesse de dispositifs de puissance GaN/Si en environnement sévère, en fonctionnement en fréquence, afin de vérifier si la méthodologie usuelle héritée des technologies Silicium suffit à évaluer les technologies GaN/Si. La tenue en radiation de transistors de puissance est habituellement testée en polarisation statique pour les composants conventionnels en Si. L'objectif de cette expérimentation est d'évaluer la tenue en radiation des transistors GaN HEMT en polarisation statique et en fonctionnement dynamique, afin de déterminer l'approche de test la plus pertinente pour ces composants grand gap. Néanmoins, il fut spécifié que le banc de commutation devait également pourvoir réaliser l'extraction des indicateurs de performances usuels pour ces essais : les courants de fuites DC  $I_{GSS}$  et  $I_{DSS}$ . Les choix techniques réalisés dans le cadre du développement de ce banc ont été motivés par les contraintes inhérentes à l'objectif et à la réalisation du projet.

Dans le cadre des essais sous irradiation, le dimensionnement du banc d'évaluation fut également impacté par le setup d'irradiation lui-même. Par exemple, le fait de réaliser les essais dans une enceinte sous vide limite le refroidissement de la charge pendant le fonctionnement en commutation. Il a donc été choisi de placer la charge hors de l'enceinte, ramenant des parasites dus aux longueurs de câbles entre la charge et l'enceinte ainsi qu'entre l'intérieur de l'enceinte et le DUT, limitant les performances dynamiques.

Par ailleurs, afin de s'assurer de n'évaluer que le comportement des DUT, il fut également choisi de ne placer que les DUT au sein de l'enceinte sous vide, n'exposant ainsi que les dispositifs à tester aux conditions critiques sans perturber le fonctionnement du banc. Néanmoins, ce choix limite le fonctionnement en dynamique des DUT par le placement de la charge et de la commande à des distances importantes du DUT (longueur de câble importante notamment). Pour finir, le banc d'essai nécessitant de mesurer les paramètres statiques DC  $I_{GSS}$  et  $I_{DSS}$  tout en pouvant faire commuter les composants en fréquence pendant plusieurs minutes, la commutation sous charge résistive a été choisie car offrant le meilleur compromis entre l'utilisation du banc et l'objectif à atteindre. Il est évidemment plus représentatif de faire commuter les composants en demi-pont avec une diode de roue libre ou avec un second DUT en High Side, sous charge inductive (ou R-L). Néanmoins, dans le cas présent, la configuration demi-pont perturberait les mesures des indicateurs de performances (passage du setup de mesures DC à la polarisation AC). Les commutations en demi-pont complexifieraient significativement le fonctionnement du banc (notamment pour l'extraction des paramètres DC  $I_{GSS}$  et  $I_{DSS}$ ), tout en pouvant endommager les DUT en fonctionnement du fait des importantes inductances parasites entre la charge et le DUT. De plus, l'objectif premier est de réaliser des commutations en fréquences des DUT à une distance importante, et non de réaliser des caractérisations dynamiques fines et optimales, dans un premier temps. C'est pourquoi la commutation sous charge résistive a été retenue ici, car offrant le meilleur compromis entre l'objectif et les contraintes du projet.

## 2.2. Présentation matérielle du banc

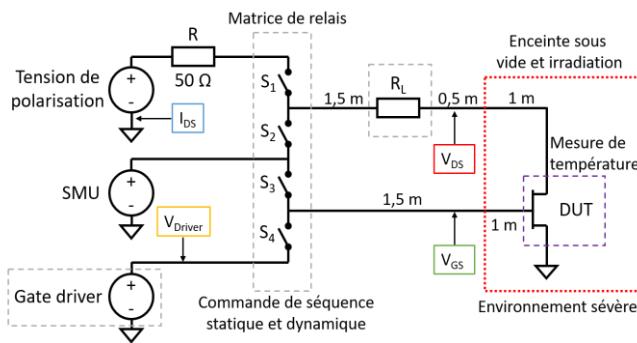

Le banc d'essai se compose d'une cellule de commutation sous charge résistive et d'équipements de caractérisation et de mesure d'indicateurs de performances (courants de fuite  $I_{GSS}$ ,  $I_{DSS}$ ). Leur est associée une matrice de quatre relais permettant de passer du fonctionnement dynamique à la mesure des paramètres statiques (voir Fig. 1). Les DUT sont déportés du reste du banc, séparés par une distance de câble de 2 à 4 m de la source de puissance et du gate driver, et placés dans une enceinte sous vide et sous irradiation. Le comportement du DUT est également contrôlé grâce à des sondes et une mesure de température, comme illustré ci-dessous

Fig. 1 : Schéma d'un exemple de mise en place du banc d'essai déporté

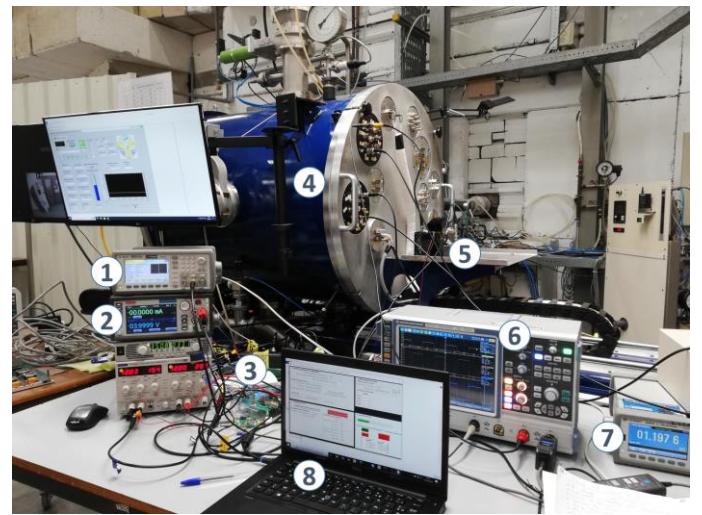

Fig. 2 : Banc d'essai déployé sur site d'irradiation à l'UCL Louvain. 1 : GBF pour pilotage de grille. 2 : SMU. 3 : carte de relais. 4 : enceinte d'irradiation sous vide. 5 : résistance de charge. 6 : oscilloscope. 7 : Multimètre pour suivi de température du DUT via RTD. 8 : interface de suivi et contrôle de l'essai.

La photo en Fig. 2 permet de se représenter le banc déployé ainsi que les distances nécessaires entre les instruments et l'enceinte sous vide d'irradiation. Les DUT sont assemblés sur des cartes coupon qui se connectent sur des cartes supports de test à l'intérieur de l'enceinte (Fig. 3).

Fig. 3 : Cartes de test. A gauche, 4 cartes supports montées sur le cadre de l'enceinte sous vide d'irradiation. A droite, une carte coupon de test avec transistor, qui se connecte sur les cartes supports.

### 2.2.1. Limitation de l'impact des effets parasites en dynamique

La polarisation statique des composants permettant d'appliquer un stress en tension à l'état bloqué n'est pas problématique. En revanche, réaliser des essais sur des transistors éloignés en fonctionnement dynamique implique de considérer les effets parasites apportés par la configuration de banc déporté (par exemple, longueur des câbles, interfaces, et impédance du PCB). En effet, ces effets parasites ont un impact important sur les signaux en dynamique, pouvant mener à une dégradation ou une défaillance du DUT, ce qui ne souhaite pas être observé, ne permettant pas d'évaluer uniquement l'environnement sévère. Cela implique des limitations de fonctionnement comme un ralentissement des fronts de commutation pour éviter les surtensions et surintensités.

D'autre part, la conception du banc a été optimisée par l'utilisation de technique de routages et de techniques RF tels que les lignes de transmission<sup>[4][5]</sup>, après avoir modélisé les différents éléments du montage (câbles, pistes) à l'aide d'outils appropriés<sup>[6]</sup>.

Une résistance de  $50 \Omega$  permet l'adaptation d'impédance en sortie de la source de puissance. Cela limite au maximum les réflexions de signal dans les lignes de transmission et donc la

perturbation du fonctionnement du dispositif à tester. Les impédances des pistes des cartes support et coupon de test sur lesquelles sont assemblés les DUT (Fig. 3) sont également contrôlées pour optimiser les signaux.

### 2.2.2. Suivi de l'auto-échauffement des composants testés

Comme indiqué sur la Fig. 1, un suivi thermique du DUT est réalisé à l'aide de capteurs RTD (Pt1000) durant l'essai. En effet, les pertes en commutation dues au montage et au ralentissement des fronts de commutation sont importantes, générant un auto-échauffement du composant.

Ce suivi thermique est nécessaire car, dans le cas où l'environnement sévère n'est pas la température (e.g. l'irradiation comme ici), une défaillance due à un auto-échauffement trop important fausserait l'évaluation du DUT. Dans notre cas, ce suivi est d'autant plus important que dans un environnement de test sous vide, il n'y a pas de dissipation thermique par convection.

Lors des essais, la température peut être mesurée en plaçant un capteur directement sur le boîtier du DUT ou en mesurant la température sur la carte coupon sur laquelle est brasé le DUT. Dans notre cas, nous avons fait le choix de mesurer la température en face arrière du coupon PCB, et de réaliser une calibration de la température mesurée par rapport à celle du composant en amont des campagnes d'essais en radiation. En effet, dans le cas d'une campagne d'irradiation, la zone active du DUT doit pouvoir être irradiée. Les dispositifs sont amincis pour s'assurer que la LET de l'ion lourd utilisé puisse traverser la face active (amincissement à environ 50 µm). Dans ce cas, il n'est plus possible de placer un capteur sur le DUT directement. D'autre part, si de nombreux essais sont réalisés, il est plus pratique et répétable de suivre la température grâce à un capteur fixé sur la carte support plutôt que de fixer un capteur sur chaque composant.

La Fig. 4 illustre le placement de capteurs thermiques sur un DUT (non aminci). Un RTD est placé sur la carte support de manière à mesurer la température en face arrière de la carte coupon et un RTD est placé sur le pad thermique qui est accessible d'un composant GaN/Si HEMT.

Fig. 4 : A gauche, carte support avec RTD mesurant la température de la face arrière du coupon de test, et, à droite, carte coupon avec RTD placé sur le pad thermique du transistor

En considérant la température du pad thermique comme étant la température de jonction du DUT, cette configuration permet de réaliser la corrélation entre la température de composant et celle mesurée en face arrière du PCB. Ainsi, il est possible d'identifier une température limite à ne pas dépasser en face arrière du PCB pour que le DUT ne se dégrade pas par effet thermique et reste dans sa SOA.

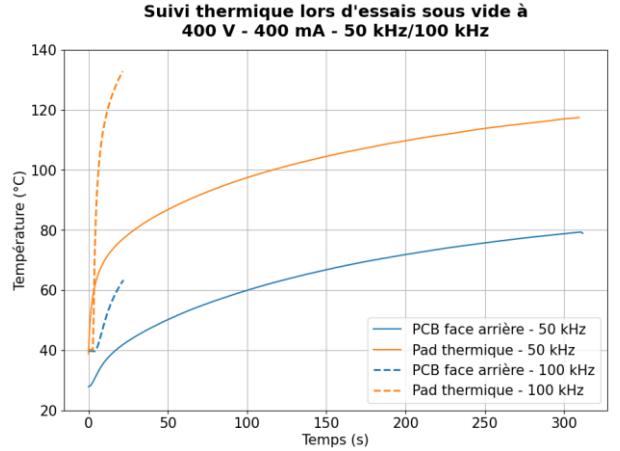

La Fig. 5 expose des résultats d'essais thermique sous vide en commutations. Elle met en évidence l'impact de la fréquence sur l'auto-échauffement. Une fréquence de 100 kHz n'a pas permis, sous vide, de réaliser des commutations pendant plus

d'une vingtaine de secondes, sans atteindre des températures élevées au niveau du pad thermique.

En abaissant la fréquence (ici à 50 kHz), il est possible d'augmenter la durée de l'essai, tout en limitant l'auto-échauffement, la température de jonction pouvant être contrôlée par la mesure de la température en face arrière du PCB.

Fig. 5 : Mesures de température du pad thermique du DUT et de la face arrière du coupon PCB, lors d'essais sous vide, en commutations à 400 V, 400 mA et pour deux fréquences de 50 kHz et 100 kHz.

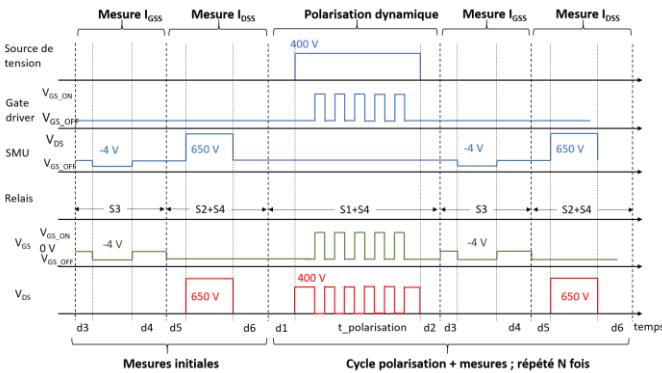

### 2.3. Séquence d'essais en polarisation statique ou dynamique avec mesures d'indicateurs statiques

Comme illustré sur la Fig. 1, le banc permet de combiner un fonctionnement dynamique sous charge résistive ainsi que des mesures statiques, ici les courants de fuite  $I_{GSS}$  et  $I_{DSS}$ , lesquels sont généralement utilisés comme indicateurs dans les essais de vieillissement. En effet, la nécessité de suivre l'état des DUT durant les essais implique de pouvoir extraire des indicateurs de fonctionnement durant les séquences de polarisation dynamique ou statique.

Ces paramètres statiques sont évalués à l'aide d'un Source Measurement Unit (SMU). Cela implique une interruption du fonctionnement dynamique du DUT pendant la mesure statique. Pour ce faire, la matrice de relais électromécaniques de puissance développée permet l'enchaînement des différentes configurations du banc : polarisation statique ou dynamique du DUT (relais S1 et S4 fermés), mesure de  $I_{GSS}$  (S3 fermé) ou mesure de  $I_{DSS}$  (S2 et S4 fermés). Un suivi des signaux  $V_{driver}$ ,  $V_{DS}$  et  $I_{DS}$  est également réalisé avec un oscilloscope pendant le fonctionnement en fréquence des dispositifs, afin de vérifier le comportement dynamique du dispositif testé.

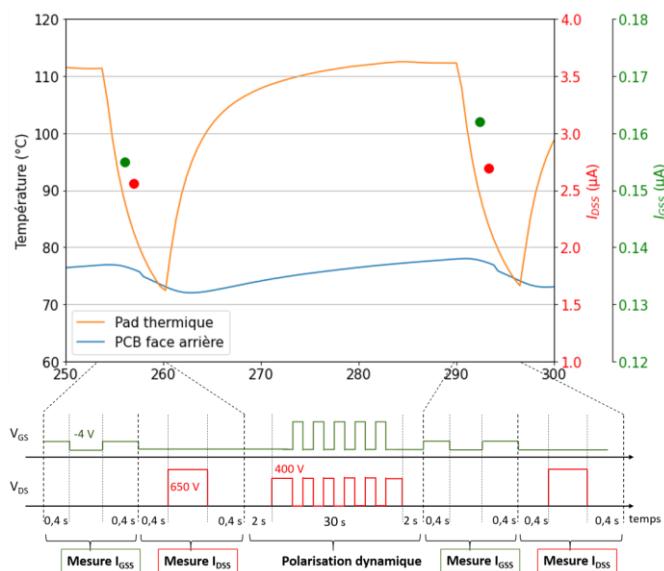

La séquence d'essai est prévue comme une polarisation statique ou dynamique du DUT, interrompue par des mesures des paramètres statiques  $I_{DSS}$  et  $I_{GSS}$ , comme illustré en Fig. 6. L'enchaînement des phases de mesures statiques et de polarisation peut se faire de façon « manuelle » avec une action requise de l'opérateur, ou de façon automatique, avec des délais établis.

La durée minimale d'interruption de la polarisation est limitée principalement par l'application et la coupure de la tension de polarisation de drain, les mesures de courants de fuites en elles-mêmes étant relativement courtes (de l'ordre de la milliseconde). En effet, nous avons pour l'instant fait le choix de faire commuter les relais uniquement en l'absence de tension. Les délais d1 et d2 (voir Fig. 6) en début et fin de phase de polarisation sont adaptés en conséquence par précaution.

Fig. 6 : Séquence du banc d'essais pour une polarisation dynamique des composants interrompue par des mesures statiques de courants de fuites

Les délais d1, d3 et d5 interviennent après un changement d'état des relais, respectivement pour la phase de polarisation AC ou DC, la phase de mesure de  $I_{GSS}$  et la phase de mesure de  $I_{DSS}$ . Ils sont donc limités par la durée minimale de commutation des relais (environ 10 ms). Les délais d2, d4 et d6 interviennent en fin de phases de polarisation, de mesure de  $I_{GSS}$  et de mesure de  $I_{DSS}$  respectivement. Ils jouent un rôle de précaution afin de s'assurer de réaliser le changement d'état des relais sans tension appliquée. Le temps de polarisation statique ou dynamique n'est pas limité, ni le nombre de cycles ou le temps total de l'essai.

Cette séquence d'essai est entièrement pilotée par un programme développé en Python. Celui-ci gère l'instrumentation des divers équipements, la séquence temporelle ainsi que la sauvegarde des données. L'opérateur interagit avec le programme via une interface utilisateur, permettant le suivi des essais et le contrôle des paramètres.

### 3. EXEMPLE DE RESULTATS

Les figures Fig. 7 et Fig. 8 exposent des résultats issus du banc lors d'un essai en commutation, avec interruptions pour l'évaluation des courants de fuite menés sur un transistor GaN HEMT 650 V – 60 A du commerce. Cet exemple ayant pour but d'illustrer le fonctionnement du banc, le DUT n'est pas placé en environnement sévère : le test se déroule dans l'air, à une température ambiante de 25°C.

La séquence appliquée est représentée en Fig. 6, avec les valeurs suivantes :

- $d1 = d2 = 2 \text{ s} ;$

- $d3 = d4 = d5 = d6 = 400 \text{ ms} ;$

- $t_{\text{polarisation AC}} = 30 \text{ s} ;$

- nombre N de cycles : 20 ;

- durée totale de fonctionnement dynamique : 10 min.

Afin de se rapprocher des conditions des essais sous irradiations réalisés avec le CNES, le DUT est ici séparé du banc d'essai par environ 3 mètres de câbles coaxiaux, tel qu'indiqué sur le schéma de la Fig. 1. La valeur de la résistance de charge  $R_L$  est de  $1 \text{ k}\Omega$ . Le DUT est polarisé en dynamique à 100 kHz et à la tension  $V_{DS}$  de 400 V, produisant un courant à l'état passant d'environ 400 mA. Un courant plus élevé peut être envisagé en diminuant  $R_L$ , mais il est nécessaire de s'assurer de ne pas exacerber les effets des parasites du montage. Dans notre cas, le cadre de notre campagne d'essais sous irradiation n'exigeant pas le courant nominal des dispositifs testés, celui-ci est donc fixé à une valeur relativement faible afin de s'assurer de l'absence de surtensions à la commutation du dispositif. Ceci permet de s'affranchir de problématiques de vieillissement causées par les effets parasites du banc plutôt que par l'environnement sévère.

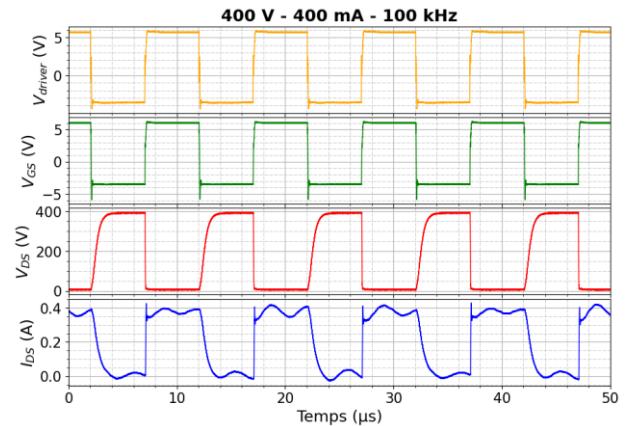

Dans cet exemple, et comme illustré sur la Fig. 1, le signal  $V_{\text{driver}}$  est extrait directement à la sortie du gate driver. Le signal  $V_{GS}$ , extrait au niveau de l'interface de l'enceinte sous vide, sert de vérification de l'intégrité du signal. Les signaux  $V_{DS}$ , également extrait au niveau de l'interface de l'enceinte, et  $I_{DS}$  correspondent à la tension drain-source et au courant dans la charge. La Fig. 7 présente une acquisition des formes d'ondes pendant l'essai, sur une fenêtre de 50 µs.

La forme du signal  $V_{DS}$  à l'ouverture s'explique par un effet capacitif des câbles coaxiaux qu'il est nécessaire de charger pour réaliser la commutation (autour de 100 pF/m pour les câbles RG58). Cependant, malgré une distance de câble importante, et donc de parasites inhérents à une telle configuration, les formes d'ondes extraites ne présentent pas d'oscillation critique lors du fonctionnement du dispositif.

Fig. 7 : Formes d'ondes d'un essai en commutation réalisé à 400 V – 100 kHz sur composant GaN HEMT. La résistance de charge  $R_L$  est fixée à  $1 \text{ k}\Omega$  afin de limiter le courant  $I_{DS}$ .

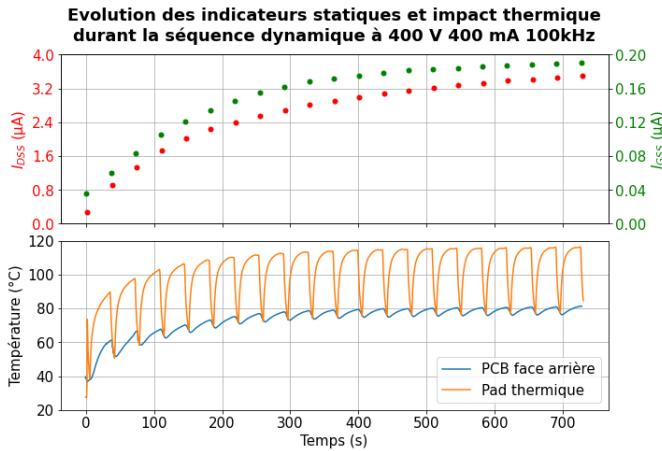

Le suivi de l'évolution des signaux dynamiques ainsi que des indicateurs de performances statiques  $I_{GSS}$  et  $I_{DSS}$  (voir Fig. 8) permettent de vérifier l'état du dispositif, mais également d'observer son éventuelle dégradation lors de l'essai.

Les mesures des courants de fuite à l'aide du SMU ont été réalisées ici avec un même range de 100 µA, pour lequel l'exactitude est de 0,02 % de la valeur lue + 6 nA. Le choix du range de mesure dépend de l'ordre de grandeur des courants de fuite de la référence testée, ainsi que de la priorité qui est mise soit à la mesure précise des indicateurs lorsque leur valeur est faible, soit au suivi de leur possible dérive vers des valeurs élevées durant l'essai. Ainsi, plus le range est élevé, plus il est possible de suivre le comportement du DUT lorsque l'environnement sévère induit une dégradation progressive des performances, mais plus la résolution et l'exactitude sont élevées.

La polarisation grille-source durant la mesure de  $I_{GSS}$  est de -4 V. La polarisation drain-source pendant la mesure de  $I_{DSS}$  est de 650 V. Les résultats expérimentaux montrent une augmentation faible des courants de fuite (Fig. 8), les valeurs restant dans un même ordre de grandeur. Cette augmentation est due à l'augmentation de la température du DUT, les pertes en commutation induisant un auto-échauffement significatif.

Fig. 8 : Evolution des courants de fuite  $I_{DSS}$  et  $I_{GSS}$  utilisés comme indicateurs de performance et suivi thermique lors de l'essai. Chaque mesure est séparée de 30 secondes de fonctionnement en dynamique à 400 V – 400 mA – 100 kHz, tel qu'illustré en Fig. 7.

Fig. 9 : Zoom sur les résultats de mesures de courants de fuite et d'évolution de température et correspondance avec la séquence d'essai.

Durant cet essai, la température est mesurée avec deux RTD positionnés sur le pad thermique du DUT et en face arrière du coupon PCB, comme illustré en Fig. 4. Les Fig. 8 et Fig. 9 présentent l'augmentation de ces températures, en parallèle des augmentations des courants de fuite. Sur la Fig. 9, l'évolution des températures est exposée par rapport aux différentes phases

de polarisation dynamique et de mesures des indicateurs de fonctionnement.

#### 4. CONCLUSIONS

Afin d'évaluer la robustesse de composants de puissance GaN HEMT dans un environnement sévère tel que sous radiation et sous vide, un banc d'essai en commutation déporté a été développé. En prenant en compte les contraintes liées à l'éloignement des DUT et de suivi d'état de fonctionnement de ceux-ci, le banc présenté permet de comparer les tenues en radiation de composants de puissance proche de leur conditions d'utilisation en fréquence (fonctionnement dynamique) et en polarisation statique.

Il est envisagé d'optimiser cette première approche concluante pour de prochaines campagnes d'essais, en intégrant notamment un système de refroidissement pour rapprocher la charge des DUT dans l'enceinte sous vide. Cela permettrait d'optimiser les fronts de commutation afin d'évaluer le dispositif dans des conditions plus représentatives en fréquence et en courant. Concernant le suivi de l'état de fonctionnement des DUT, il est aussi envisageable de coupler les mesures statiques avec une détection de défaillance par l'oscilloscope.

#### 5. REMERCIEMENTS

Les auteurs souhaitent remercier M. Jean-Baptiste Sauveplane et le CNES pour la collaboration dans le cadre du projet R&T ayant permis ces travaux. Ils remercient également le personnel de l'UCL Louvain ainsi que Nancy Postiau pour son aide quant à la logistique de mise en place du banc sur site d'irradiation.

#### 6. REFERENCES

- [1] J. -B. Sauveplane et al., "Heavy-Ion Testing Method and Results of Normally OFF GaN-Based High-Electron-Mobility Transistor," in IEEE Transactions on Nuclear Science, vol. 68, no. 10, pp. 2488-2495, Oct. 2021, doi: 10.1109/TNS.2021.310.

- [2] JEDEC JEP180, "Guideline for switching reliability evaluation procédures for GaN power devices", Version 1.0, January 2021.

- [3] IEC 63284:2022, "Semiconductor Devices - Reliability Test Method By Inductive Load Switching For Gallium Nitride Transistors", IEC Standards, 2022.

- [4] A. G. Galeano, E. Marcault, C. Alonso and D. Tremouilles, "Transmission Line Approach for the PCB Gate Interconnection Design in GaN-Based High-Frequency Power Converters," PCIM 2021.

- [5] I. Sirot, A. Fromentel, "Canaux de transmission I: Propagation guidée lignes de transmission fibres optiques », EFREI, Paris Sud, 2012

- [6] E.Sicard, A. Boyer, IC-EMC (2.9) [Logiciel], 2022, <http://www.ic-emc.org/>