# Commande rapprochée d'un IGBT pour l'atténuation des perturbations électromagnétiques

Daniel Sting Martinez-Padron<sup>1</sup>, Nicolas Patin<sup>1</sup> et Eric Monmasson<sup>2</sup>

<sup>1</sup>Université de technologie de Compiègne, Roberval (Mechanics, energy and electricity), Centre de recherche Royallieu – CS 60319 – 60203 Compiègne Cedex – France.

<sup>2</sup>CY Cergy Paris Université, SATIE laboratory, Cergy-Pontoise, France.

**RESUME** –Les transistors de puissance comme les IGBT et les MOSFET sont une source d'interférences électromagnétiques (EMI) pendant les commutations en raison des variations rapides de tension/courant. L'augmentation de la durée des commutations peut réduire la production des EMI mais augmente les pertes. Plusieurs techniques de commande rapprochée pour réduire ces EMI ont été proposées dans la littérature. Dans ce travail, une commande basée sur le contrôle d'un profil de courant de grille, rendu possible par de nouveaux drivers disponibles sur le marché, est proposé. Pour cela, on s'appuie sur la caractéristique du transistor de tension grille-source en fonction de la charge injectée dans la grille. Afin de démontrer la performance de cette méthode, elle est évaluée par simulation SPICE à l'aide d'un facteur de mérite permettant de la comparer quantitativement à une technique de référence dénommée CATS (Commande autour de la Tension de Seuil).

**Mots-clés – IGBT, commande rapprochée, EMI, Pertes.**

## 1. INTRODUCTION

Les transistors de puissance comme les IGBT et les MOSFET sont largement utilisés dans de nombreuses applications telles que les variateurs de vitesse industriels, les groupes motopropulseurs des véhicules électriques/hybrides ou les applications grand public. Cependant, un inconvénient de ces dispositifs est qu'ils génèrent des perturbations électromagnétiques (EMI) pendant les commutations car les niveaux élevés de  $dv/dt$  et  $di/dt$  produisent des EMI conduites et rayonnées [1]. Néanmoins, ces EMI peuvent être réduites en augmentant la durée des commutations, mais cela tend à augmenter les pertes dans les semiconducteurs. On notera que la durée et la forme des  $dv/dt$  et  $di/dt$  sont liées au courant injecté dans la grille. Le moyen le plus simple (et le plus classique) de ralentir la commutation des transistors est d'intercaler entre le driver (source de tension quasi idéal) et la grille (capacitive) du transistor une résistance qui augmentera la constante de temps d'évolution de la charge stockée dans la grille. Toutefois, le choix d'une résistance de grille relève d'un compromis entre les pertes et les EMI mais cette technique ne garantit pas l'optimalité des EMI pour un niveau de pertes donné. Pour cela, un contrôle plus fin de la commutation est nécessaire pour agir sur sa forme indépendamment du temps requis pour la commutation. Pour ce faire, une première solution consiste en un driver de commande basé sur une source de courant externe et la détection du plateau de Miller, présenté dans [2, 3, 4]. Celle-ci permet d'obtenir un rapport adéquat entre la génération d'EMI et les pertes. Dans cette approche, un circuit push-pull est utilisé pour modifier la valeur de la résistance de la grille entre l'amorçage et le blocage du transistor. La valeur de la résistance de la grille pendant l'amorçage est choisie pour réduire la génération d'EMI en augmentant la durée du  $di/dt$ . La chute de tension est accélérée par l'injection d'un courant provenant d'une source externe qui est activée par un circuit de détection du plateau de Miller afin de compenser les pertes. Lors du blocage, la résistance est sélectionnée pour

réduire autant que possible les pertes par commutation induites par la queue de courant, classique pour un transistor IGBT. Un autre circuit de commande, basé sur une boucle fermée, est rapporté dans [5] et [6]. Un correcteur proportionnel-intégral (PI) contrôle le courant de grille injecté dans l'IGBT pour asservir le  $di/dt$  et le  $dv/dt$ . Il faut alors noter que la principale difficulté avec cette solution est d'obtenir un temps de réponse compatible avec les formes de consignes imposées et les temps de commutations attendus pour satisfaire aux contraintes de pertes. Dans [7] et [8], un circuit de contrôle de capacité Miller externe est ajouté afin de contrôler le  $dv/dt$ . Là encore, l'objectif est de contrôler la forme de  $di/dt$  et  $dv/dt$  avec un lissage des fronts de commutation.

La méthode CATS (Commande Autour de la Tension de Seuil) est proposée dans [9] pour réduire la génération d'EMI en lisant une fois encore les formes d'ondes de tension et de courant en appliquant un niveau de tension de grille intermédiaire, qui comme son nom l'indique se trouve au voisinage du  $V_{gth}$  du transistor.

Il est notamment prouvé dans [10] qu'une forme gaussienne (ou plutôt des fronts obtenus avec l'intégrale d'une gaussienne) minimise les EMI indépendamment du temps de commutation.

Récemment, des circuits de pilotage [11]-[15] basés sur une source de courant de grille avec une résolution fine ont été mis sur le marché. Dans cet article, une méthode de pilotage basée sur un profil de courant de grille permettant de contrôler la forme de  $dv/dt$  est proposée. Elle consiste à appliquer un profil de courant constant par intervalles pour lequel on sera capable de fixer l'amplitude et la durée de chacun de ces intervalles. Ces paramètres sont ajustés en prenant en compte le comportement non-linéaire du transistor au début du plateau de Miller. Cette méthode est décrite dans la section 2 et les résultats des simulations obtenues sont présentés dans la section 3. Une comparaison entre cette technique et la commande CATS est effectuée à la section 4 pour ensuite aboutir à la conclusion de l'article.

## 2. MÉTHODE PROPOSÉE

La méthodologie proposée est basée sur la charge de la grille du transistor qui détermine la forme et la durée des  $dv/dt$  et  $di/dt$  entre collecteur et émetteur. Le comportement du transistor tout au long de la charge de la grille est décrite dans le paragraphe suivant.

### 2.1. Charge de la grille du transistor

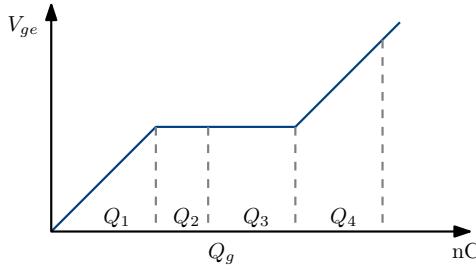

La courbe typique de tension grille-émetteur en fonction de la charge injectée dans la grille d'un transistor IGBT (ou MOSFET) est montrée dans la Figure 1. Elle peut être divisée en plusieurs parties liées aux différents régimes de fonctionnement du transistor. Cette caractéristique, fournie par les constructeurs, peut être obtenue en pratique en injectant un courant constant dans la grille. La croissance de la valeur de la charge  $Q_g$  sera donc linéaire en fonction du temps et par ailleurs, le courant

FIG. 1. Courbe de tension  $V_{ge}$  en fonction de la charge injectée dans la grille.

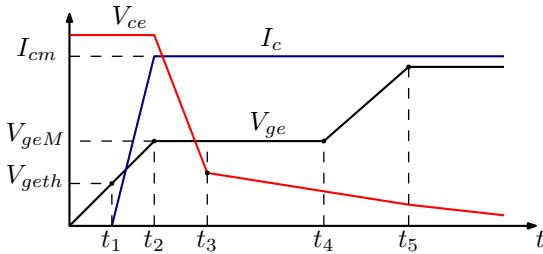

constante permet également de s'affranchir des effets des inductances parasites de la connexion entre le transistor et la source [16]. La courbe de la Figure 2 montre ensuite la dynamique du courant et de la tension entre collecteur et émetteur durant cette charge de la grille à courant constant. Cette courbe peut être divisée en 4 étapes :

- **Étape 1** :  $0 < t < t_1$ . La tension de grille  $V_{ge}$  est inférieure à la tension de seuil  $V_{geth}$ . Le courant de collecteur  $I_c$  est fortement limité (seulement quelques  $\mu\text{A}$ ). On considère alors que le transistor est bloqué.

- **Étape 2** :  $t_1 < t < t_2$ . Une fois que  $V_{geth}$  est atteint, le transistor est mis en conduction et le courant de collecteur circule jusqu'à atteindre sa valeur maximale  $I_{cm}$  (fixée par le courant dans la charge). Durant toute cette phase, le transistor fonctionne en régime linéaire et dissipe donc beaucoup de puissance.

- **Étape 3** :  $t_2 < t < t_4$ . Pendant le plateau de Miller,  $V_{ge} = V_{geM}$  à cause de la capacité grille-collecteur (capacité de Miller).  $V_{ce}$  commence à chuter avec différentes pentes déterminées pour différentes valeurs de charge de la capacité de Miller [16] (d'où un découpage en deux phases avec un instant  $t_3$  intermédiaire). En fait, le courant de grille ne sert plus à charger la capacité grille-émetteur ( $C_{ge}$ ) mais à décharger la capacité grille-collecteur (d'où la chute du potentiel de collecteur par rapport à la grille mais aussi par rapport à l'émetteur).

- **Étape 4** :  $t_4 < t < t_5$ . Dès que l'effet de Miller se termine, la tension de grille recommence à augmenter vers sa valeur finale. Le transistor tend alors vers son régime de saturation avec des pertes qui se stabilisent au niveau des seules pertes par conduction.

FIG. 2. Courbe dynamique de tension et courant dans un IGBT durant la charge de grille.

## 2.2. Profil de courant de grille proposé

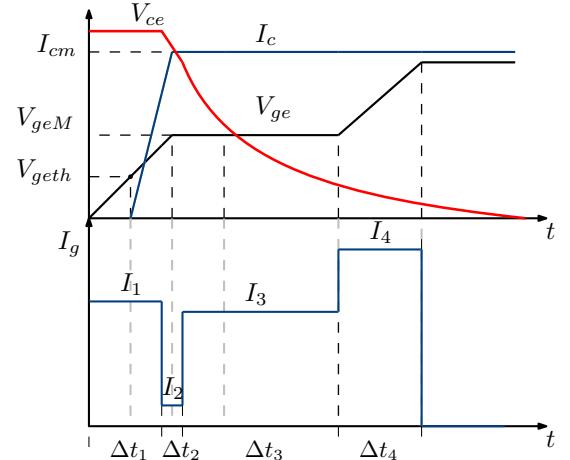

Comme indiqué précédemment, le comportement transitoire de commutation, qui détermine la génération des EMI et les pertes, est fortement lié à la charge de la grille, elle-même contrôlée par le courant injecté par le driver. Pour cette raison, dans cet article, il est proposé de piloter la grille par un profil d'échelons de courant (*Current Step Profile* - CSP) de telle sorte qu'il soit possible de réguler chaque étage de charge et de pouvoir contrôler le transitoire de tension. Ainsi pendant l'amor-

cage du transistor, le CSP doit permettre de ralentir la chute de tension  $v_{ce}$  au début de la plateforme de Miller. Le ralentissement de cette transition permet un contrôle en  $dv/dt$  plus conforme à l'objectif qui est l'intégrale d'une gaussienne. Le CSP est présenté dans la Figure 3 : il est formé (pour des raisons de recherche de modération de la complexité) de 4 échelons de courant d'amplitude  $I_j$  avec  $1 \leq j \leq 4$  et durée  $\Delta t_j$  et chacun permet d'effectuer différentes étapes de la charge de grille. L'am-

FIG. 3. Profil de courant de grille proposé (CSP).

plitude de chaque échelon est calculée en considérant les étapes de la courbe dynamique présentée dans la Figure 2 comme suit :

- **Échelon 1.** Ce premier échelon sert à réaliser les deux premières étapes de la charge du transistor, à savoir, premièrement le courant pour atteindre la tension de seuil du IGBT et deuxièmement la mise en conduction du transistor. Pendant l'étape 1, le courant de grille est déterminé par la charge  $C_{ge}$  et par :

$$I_{g1} = C_{ge} \frac{dV_{ge}}{dt} \approx C_{ge} \frac{V_{gth}}{\Delta t_{s1}}, \quad (1)$$

où  $I_{g1}$  est le courant de grille pour l'étape 1,  $\Delta t_{s1}$  la durée de temps pour que  $V_{ge} = V_{geth}$ . Durant l'étape 2,  $I_c$  augmente jusqu'à  $I_{cm}$  pendant  $\Delta t_{s2}$  et  $C_{gc}$  est chargé par le courant :

$$I = C_{gc} \frac{dV_{gc}}{dt}. \quad (2)$$

En considérant que  $V_g = V_{ge} - V_{ce}$ , avec  $V_{ce}$  constant et que la transconductance de l'IGBT est  $g_m = \Delta I_c / \Delta V_{ge}$ , le courant de grille est calculé par :

$$I = \frac{C_{ies}}{g_m} \frac{dI_c}{dt} \approx \frac{C_{ies}}{g_m} \frac{\Delta I_c}{\Delta t_{s2}}, \quad (3)$$

où  $I_{g2}$  est la courant de grille pour l'étape 2. Pour la méthode proposée,  $\Delta I_c$  est considéré comme une proportion du courant maximal tel que  $\Delta I_c = \alpha I_{cm}$  avec  $0 < \alpha \leq 1$ . En prenant  $I_1 = I_{g1} = I_{g2}$ , la durée de l'échelon 1,  $\Delta t_1$  est calculée à partir des équations (1) et (3) et  $\Delta t_1 = \Delta t_{s1} + \Delta t_{s2}$ .

- **Échelon 2.** Cet échelon contrôle la fin du transitoire de courant et la transition entre  $di/dt$  et  $dv/dt$  (début du plateau de Miller). Afin d'avoir un contrôle adéquat du  $dv/dt$  et en raison du comportement non-linéaire de la capacité d'entrée et de l'effet de la récupération de la diode, dans cette méthodologie, il est proposé de ralentir cette transition avec un échelon de faible amplitude  $I_2$  dont la durée  $\Delta t_2$  est calculée avec l'équation (3).

- **Échelon 3.** Pendant cette étape, le  $dv/dt$  est contrôlé. A partir de l'échelon 3. Le courant de grille peut être estimé par :

$$I_3 = C_{gc} \frac{dV_{ce}}{dt} \approx C_{gc} \frac{\Delta V_{ce}}{\Delta t_3}. \quad (4)$$

En fixant la durée  $\Delta t_3$ , le  $dv/dt$  est contrôlé par l'amplitude de l'échelon 3.

- **Échelon 4.** Afin de finir la charge de grille, l'amplitude de l'échelon  $I_4$  est calculée en utilisant (1) et en considérant la capacité équivalente pendant ce temps.

### 3. ÉVALUATION

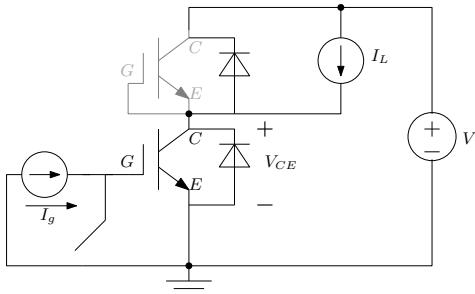

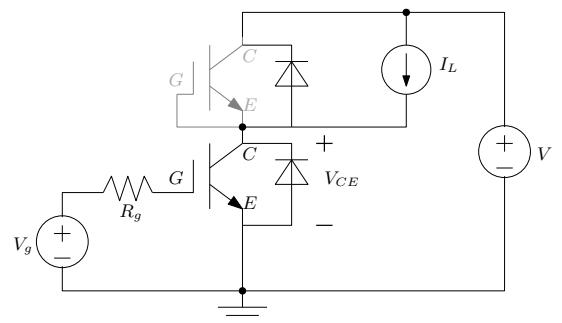

Le CSP est évalué par simulation en utilisant le logiciel Lts-pice et le modèle SPICE de l'IGBT IKW40N65ET7. Le circuit de test est présenté à la Figure 4. La source de courant générant le CSP est paramétré avec quatre amplitudes ( $I_1$ ,  $I_2$ ,  $I_3$  et  $I_4$ ) successives et leurs durées associées ( $\Delta t_1$ ,  $\Delta t_2$ ,  $\Delta t_3$  et  $\Delta t_4$ ). Tous les paramètres sont fixés à l'exception de  $I_3$  qui est celui qui va permettre de contrôler la durée de chute de la tension  $V_{ce}$ . On fait alors varier sa valeur afin d'évaluer son impact sur la génération des EMI et les pertes. Les simulations ont été réalisées avec un pas minimal de 100 ps et les paramètres électriques du circuit sont résumés dans le Tableau 1. La sélection de chaque

FIG. 4. Circuit de test pour l'évaluation du CSP.

TABLEAU 1. Paramètres d'essai.

| Paramètre                                   | Valeur     |

|---------------------------------------------|------------|

| Capacité d'entrée ( $C_{ies}$ )             | 2.475 nF   |

| Capacité de transfert inverse ( $C_{res}$ ) | 25 pF      |

| Transconductance ( $g_m$ )                  | 21 S       |

| Tension de seuil ( $V_{geth}$ )             | 5.8 V      |

| Tension d'entrée ( $V$ )                    | 130 V      |

| Courant de collecteur ( $I_c$ )             | 10 A       |

| Période de commutation ( $T_s$ )            | 50 $\mu$ s |

échelon du CSP est décrite comme suit.

- **Échelon 1.** Tout d'abord, en considérant la valeur de  $V_{geth}$  et  $C_{ies}$  montrée dans le Tableau 1 et en proposant  $t_{s1} = 100$  ns, le courant de grille pour atteindre  $V_{geth}$  est calculé par :

$$I_1 = C_{ies} \frac{V_{geth}}{\Delta t_{s1}} = 143,5 \text{ mA}. \quad (5)$$

Pour la deuxième partie, afin de ralentir la pente du courant avant d'atteindre le plateau de Miller, il est proposé d'atteindre 80% de  $I_{cm}$ , à savoir  $\alpha = 0,8$ . Car

$I_1 = 143,5 \text{ mA}$ , la durée est donnée par

$$\Delta t_{s2} = \frac{C_{ies} \alpha I_{cm}}{g_m} = 25,3 \text{ ns}. \quad (6)$$

Par conséquent, l'amplitude d'échelon 1 est de  $I_1 = 143.5 \text{ mA}$  avec une durée de  $\Delta t_1 = 125.3 \text{ ns}$ .

- **Échelon 2.** Afin de terminer la pente du courant et de commencer le plateau de Miller, un échelon de faible amplitude  $I_2$  est proposé. Dans ce cas  $I_2 = 14.3 \text{ mA}$  est sélectionné, ce qui correspond à 10% de la valeur de  $I_1$ . La valeur de  $C_{ies}$  estimée est 250 pF, alors la durée est calculée par

$$\Delta t_2 = \frac{C_{ies} (1 - \alpha) I_{cm}}{g_m} = 63,3 \text{ ns}. \quad (7)$$

L'amplitude d'échelon 2 est  $I_2 = 1.5 \text{ mA}$  avec un durée de  $\Delta t_2 = 63,3 \text{ ns}$ .

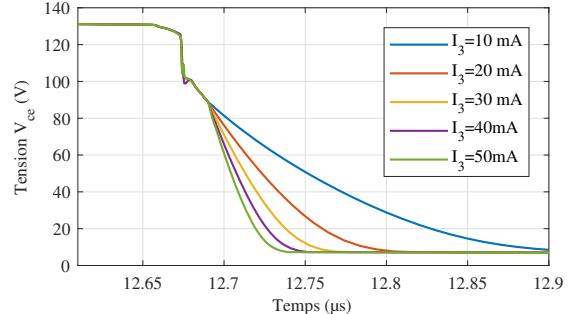

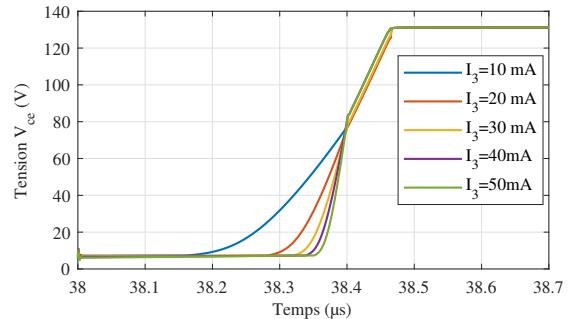

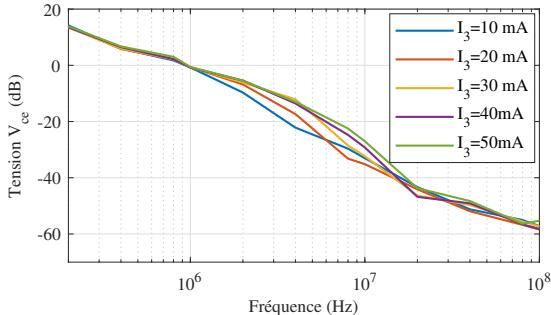

- **Échelon 3.** Pour cet échelon, cinq valeurs différentes sont sélectionnées :  $I_3 = 10 \text{ mA}$ ,  $I_3 = 20 \text{ mA}$ ,  $I_3 = 30 \text{ mA}$ ,  $I_3 = 40 \text{ mA}$  et  $I_3 = 50 \text{ mA}$ . La durée est fixée à  $\Delta t_3 = 400$  ns pour tous les cas.

- **Échelon 4.** Afin de terminer la charge de grille, la durée proposée est  $\Delta t_4 = 500$  ns, la capacité estimée à partir de la courbe de charge de grille de la documentation du composant est  $C = 20 \text{ nF}$  et l'amplitude est calculée par

$$I_4 = C \frac{\Delta V}{\Delta t_4} = 296 \text{ mA}. \quad (8)$$

L'amplitude du pas 4 est de  $I_4 = 296 \text{ mA}$  avec une durée de  $\Delta t_4 = 500$  ns.

FIG. 5. Résultats des simulations pour différentes valeurs de  $I_3$  pour le front descendant.

FIG. 6. Résultats des simulations pour différentes valeurs de  $I_3$  pour front montant.

FIG. 7. Spectres de fréquence à différents niveaux de  $I_3$ .

Les résultats obtenus dans les Figures 5 et 6 montrent la forme d'onde  $V_{ce}$  pendant le front descendant et montant à différentes amplitudes de  $I_3$ . Les spectres pour chaque à la Figure 7 montrent que la génération des EMI peut être réduite en diminuant l'amplitude de  $I_3$ . Les pertes par commutations générées sont calculées comme indiqué dans la documentation du transistor [17] :

- Pour la mise en conduction, les pertes par commutations sont mesurées pendant l'intervalle de temps entre 10 % de  $V_{ge \max} = 15 \text{ V}$  et 2% de  $V_{ce \max} = 130 \text{ V}$ .

- Pour le blocage, les pertes par commutations sont mesurées pendant l'intervalle de temps entre 90 % de  $V_{ge \max}$  et 2% de  $I_{cm} = 10 \text{ A}$ .

Les pertes globales, regroupées dans le Tableau 2, tendent à diminuer lorsque l'amplitude de  $I_3$  augmente car cette augmentation accélère le transitoire de tension du transistor.

Du point de vue des perturbations électromagnétiques, un facteur de mérite (FOM) introduit dans [19] a été utilisé. Celui-ci est basé sur l'inégalité de Heisenberg-Gabor (HG) et le co-étalement temps-fréquence des signatures des fronts montants et descendants (le signal réel pouvant être obtenu par un produit de convolution entre le signal MLI idéal - à commutations instantanées - et un signal "signature"  $\lambda(t)$  de la forme de la commutation réelle). C'est ce signal  $\lambda(t)$  (en fait deux signaux, l'un décrivant les fronts montants et l'autre les fronts descendants) qui est analysé pour évaluer son étalement temporel  $\sigma_t$  puis, après transformée de Fourier, on évalue également son étalement fréquentiel  $\sigma_\omega$ . L'inégalité HG montre que quelle que soit la fonction  $\lambda(t)$ , on a toujours  $\sigma_t \cdot \sigma_\omega \leq \frac{1}{2}$  et que la borne est atteinte pour un  $\lambda(t)$  gaussien. Le FOM présenté étant la somme des co-étalements des  $\lambda(t)$  pour les fronts montant et descendant, le cas idéal théorique serait un FOM = 1. On peut donc voir que cette borne est loin d'être atteindre ici mais qu'il existe un optimum de réglage  $I_3 = 30 \text{ mA}$  permettant de le minimiser. Par contre, cela se fait au prix d'une légère dégradation des pertes par rapport à  $I_3 = 50 \text{ mA}$  avec une augmentation de 6.8% des pertes (mais dans le cas contraire, le choix optimal pour les pertes occasionne une dégradation de 23.5% du FOM et donc des perturbations électromagnétiques).

TABLEAU 2. Résultats de l'évaluation.

| $I_3$ | Pertes par commutation | FOM    |

|-------|------------------------|--------|

| 10 mA | 7,95 W                 | 181,45 |

| 20 mA | 6,58 W                 | 179,73 |

| 30 mA | 6,10 W                 | 170,12 |

| 40 mA | 5,95 W                 | 184,31 |

| 50 mA | 5,71 W                 | 210,76 |

#### 4. COMPARAISON

La performance du CSP est évaluée par une comparaison avec une méthode efficace rapportée dans la littérature, à savoir la méthodologie CATS.

##### 4.1. Méthodologie CATS

La méthodologie CATS est proposée dans [9] et consiste à réduire les  $di/dt$  et  $dv/dt$  en débutant l'amorçage du transistor à l'aide d'un générateur de tension  $V_g$  que l'on fixe à une valeur intermédiaire  $V_{int}$  proche (mais légèrement supérieure) à la tension  $V_{geth}$  pendant une durée  $T_{int}$  comme le montre la Figure 8(a) contrairement au pilotage classique.

FIG. 8. Principe de fonctionnement de CATS : (a) amorçage et (b) blocage.

Lors du blocage, une tension nulle ou négative est forcée pour évacuer rapidement la charge stockée, qui maintient le transistor en conduction pendant un intervalle de temps  $T_o$ . Puis un deuxième niveau  $V_{int0} < V_{int}$  est injecté pendant  $T_{int0}$  comme montré dans la Figure 8(b).

##### 4.2. Comparaison et résultats

La comparaison consiste à déterminer les performances de génération d'EMI des deux méthodes (CSP et CATS) pour un même niveau de pertes par commutations. Elle est effectuée en utilisant le circuit de test montré dans la Figure 9 avec l'IGBT IKW40N65ET7 et le logiciel Lspice en prenant toujours un pas de simulation maximum de 100 ps. Le niveau de pertes par commutations choisi est 6,58W. Les paramètres du système sont :  $V=130 \text{ V}$ ,  $T_s = 50 \mu\text{s}$  et  $I_c=10 \text{ A}$ . Pour la méthodologie CATS,

FIG. 9. Principe de fonctionnement de CATS : (a) amorçage et (b) blocage.

les paramètres  $T_{int}$ ,  $V_{int0}$ ,  $T_0$  et  $V_{int}$  sont choisis comme indiqué dans le Tableau 3. Pour le CSP, la source  $V_g$  dans 9 est remplacée par une source de courant  $I_g(t)$  et la durée et l'amplitude de l'échelon  $I_3$  deviennent les degrés de liberté pour ajuster les pertes par commutations. L'amplitude et la durée de chaque étape du CSP sont présentées dans le Tableau 4.

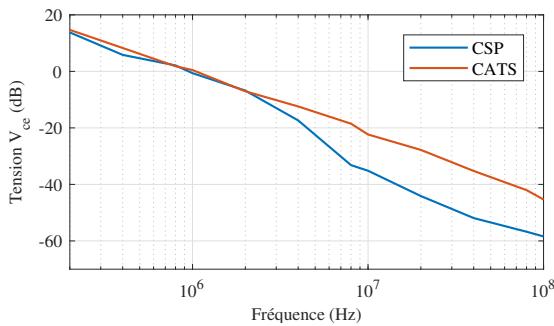

Les résultats de la comparaison sont présentés dans 10. Ils montrent l'enveloppe du spectre de fréquences de CSP et CATS pour le même niveau de pertes par commutations.

Enfin, les résultats de la comparaison montrent que le FOM pour la méthode CATS est 451,97 et pour le CSP est 144,47.

TABLEAU 3. Paramètres pour CATS.

| Paramètre  | Valeur |

|------------|--------|

| $T_{int}$  | 400 ns |

| $T_0$      | 200 ns |

| $T_{into}$ | 400 ns |

| $V_{int}$  | 7,5 V  |

| $V_{into}$ | 3,75 V |

TABLEAU 4. Paramètres pour CSP.

| Paramètre    | Valeur        |

|--------------|---------------|

| $I_1$        | 143,5 mA      |

| $I_2$        | 14,3 mA       |

| $I_3$        | 20 mA         |

| $I_4$        | 296 mA        |

| $\Delta t_1$ | 125,3 $\mu$ s |

| $\Delta t_2$ | 63,3 ns       |

| $\Delta t_3$ | 400 ns        |

| $\Delta t_4$ | 500 ns        |

FIG. 10. Résultat de la comparaison à 6,58W.

## 5. CONCLUSIONS

Dans cet article, une technique de pilotage d'IGBT basée sur un profil de courant de grille est présentée pour réduire les perturbations électromagnétiques. Le CSP proposé nous permet de contrôler le  $dv/dt$  par l'amplitude d'un palier ( $I_3$ ) de courant de grille (voire sa durée). La performance du CSP est évaluée par simulation avec différents niveaux de  $I_3$ , ce qui montre la faisabilité de la méthode de réduction des EMI. Cette technique est comparée à une autre méthode rapportée dans la littérature (CATS) et les résultats de simulation montrent que pour les mêmes pertes par commutations, le CSP génère moins d'EMI. Un inconvénient du procédé proposé, par rapport aux procédés tels que CATS, est qu'il est nécessaire de connaître certains paramètres du transistor pour effectuer un réglage pertinent des autres degrés de liberté de la commande (trois autres paliers de courant à fixer en amplitude et durée). Il est néanmoins envisageable, dans de futures études, de procéder à une adaptation en boucle fermée de ces paramètres sur la base de l'observation des commutations.

## 6. REMERCIEMENTS

Les auteurs tiennent à remercier le Conseil national de la science et de la technologie de la science et de la technologie du Mexique (CONACyT) pour la bourse d'études sous le numéro de subvention 705759.

## 7. RÉFÉRENCES

- [1] F. Costa et D. Magon, « Graphical analysis of the spectra of EMI sources in power electronics», in IEEE Transactions on Power Electronics, vol. 20, no. 6, pp. 1491-1498, Nov. 2005.

- [2] A. Galluzzo et al., « Switching characteristic improvement of modern gate controlled devices», 1993 Fifth European Conference on Power Electronics and Applications, Brighton, UK, 1993, pp. 374-379 vol.2.

- [3] A. Consoli et al., «An innovative EMI reduction design technique in power converters», in IEEE Transactions on Electromagnetic Compatibility, vol. 38, no. 4, pp. 567-575, Nov. 1996.

- [4] S. Musumeci et al., «Switching-behavior improvement of insulated gate-controlled devices», in IEEE Transactions on Power Electronics, vol. 12, no. 4, pp. 645-653, July 1997.

- [5] Y. Lobsiger et J. W. Kolar, «Closed-Loop d ii/ d tt and d vv/ d tt IGBT Gate Driver», in IEEE Transactions on Power Electronics, vol. 30, no. 6, pp. 3402-3417, June 2015.

- [6] H. Riazmontazer et al., «Closed-loop control of switching transition of SiC MOSFETs», 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, NC, USA, 2015, pp. 782-788.

- [7] J. D. Kagerbauer et T. M. Jahns, «Development of an Active dv/dt Control Algorithm for Reducing Inverter Conducted EMI with Minimal Impact on Switching Losses», 2007 IEEE Power Electronics Specialists Conference, Orlando, FL, USA, 2007, pp. 894-900.

- [8] Shihong Park et T. M. Jahns, «Flexible dv/dt and di/dt control method for insulated gate power switches», Conference Record of the 2001 IEEE Industry Applications Conference. 36th IAS Annual Meeting (Cat. No.01CH37248), Chicago, IL, USA, 2001, pp. 1038-1045 vol.2.

- [9] H. Sawezyn, N. Idir et R. Bausiere, «Lowering the drawbacks of slowing down di/dt and dv/dt of insulated gate transistors», 2002 International Conference on Power Electronics, Machines and Drives (Conf. Publ. No. 487), Santa Fe, NM, USA, 2002, pp. 551-556.

- [10] N. Patin et M. L. Viñals, «Toward an optimal Heisenberg's closed-loop gate drive for Power MOSFETs», IECON 2012 - 38th Annual Conference on IEEE Industrial Electronics Society, Montreal, QC, Canada, 2012, pp. 828-833.

- [11] S. Fukunaga, H. Takayama et T. Hikihara, «A Study on Switching Surge Voltage Suppression of SiC MOSFET by Digital Active Gate Drive», 2021 IEEE 12th Energy Conversion Congress & Exposition - Asia (ECCE-Asia), Singapore, Singapore, 2021, pp. 1325-1330.

- [12] H. Takayama, T. Okuda et T. Hikihara, «A Study on Suppressing Surge Voltage of SiC MOSFET Using Digital Active Gate Driver», 2020 IEEE Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA Asia), Suita, Japan, 2020, pp. 1-5.

- [13] K. Miyazaki et al., «General-purpose clocked gate driver (CGD) IC with programmable 63-level drivability to reduce  $I_c$  overshoot and switching loss of various power transistors,» 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 2016, pp. 1640-1645.

- [14] R. Morikawa, T. Sai, K. Hata et M. Takamiya, «New Gate Driving Technique Using Digital Gate Driver IC to Reduce Both EMI in Specific Frequency Band and Switching Loss in IGBTs», 2020 IEEE 9th International Power Electronics and Motion Control Conference (IPEMC2020-ECCE Asia), Nanjing, China, 2020, pp. 644-651.

- [15] W. Frank, A. Arens et S. Hoerold, «Real-time adjustable gate current control IC solves dv/dt problems in electric drives», PCIM Europe 2014 International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 2014, pp. 1-7.

- [16] F. Portuese et M. Melito, «Gate charge leads to easy drive design for Power Mosfet circuits», PCIM '90 Proceedings of the 18th International Intelligent Motion Conference, pp. 237-243, 1990.

- [17] Infineon, «Low Loss Duopack : IGBT with Trench and Fieldstop technology IKW40N65ET7», TRENCHSTOP, 2020,Datasheet version 2.2.

- [18] C. R. Paul, «Introduction to Electromagnetic Compatibility», 2nd ed. Hoboken, NJ : Wiley, 2006.

- [19] D. S. Martinez-Padron, N. Patin et E. Monmasson, «Definition and Implementation of an EMI Figure of Merit for Switching Pattern in Power Converters», IECON 2022 – 48th Annual Conference of the IEEE Industrial Electronics Society, Brussels, Belgium, 2022, pp. 1-6.