# Courts-circuits répétitifs non-destructifs sur des transistors HEMT-GaN 650 V

Adrien LAMBERT<sup>1,2</sup>, Hervé MOREL<sup>1</sup>, Dominique TOURNIER<sup>1</sup>, Dominique PLANSON<sup>1</sup>, Luong Viêt PHUNG<sup>1</sup>, Laurent GUILLOT<sup>2</sup>

<sup>1</sup>Laboratoire Ampère INSA-Lyon, <sup>2</sup>STMicroelectronics

**RESUME** - L'étude consiste à analyser la robustesse des composants HEMT GaN 650 V vis-à-vis des courts-circuits. L'objectif est d'appliquer des courts-circuits répétitifs et non destructifs sur un composant pour évaluer les dégradations éventuelles. Des caractérisations électriques sont effectuées avant et après les cycles de courts-circuits afin d'identifier d'éventuelle variation de certains paramètres dudit composant, cela afin d'identifier les mécanismes de défaillance.

**Mots-clés**— court-circuit, robustesse, fiabilité, GaN, transistor, MIS-HEMT, normally-ON.

## 1. INTRODUCTION

Les composants grand-gap, en particulier les transistors HEMT en nitride de gallium (GaN) sont hautement prometteurs dans le domaine de l'électronique de puissance. En effet, ces transistors présentent d'enviables performances avec des pertes en conduction et en commutation réduites et ainsi une fréquence de découpage élevée, pouvant aller jusqu'à quelques MHz. Néanmoins, leur commercialisation à grande échelle, notamment dans le domaine automobile et aéronautique, passe nécessairement par une robustesse et une fiabilité vérifiées. Résister aux incidents d'opérations majeurs, tels que les courts-circuits en fait partie et est particulièrement pertinent dans le cas par exemple de commande moteur pour la chaîne de traction de véhicules électriques. Avec une haute tension et un fort courant simultanés, les courts-circuits représentent un des événements les plus indésirables du fait de la significative quantité d'énergie à dissiper [1]. On distingue principalement deux types de court-circuit, type I (défaut de commutation dure, le défaut se produit avant la mise « on » du composant) et type II (défaut sous charge, le défaut apparaît alors que le composant est déjà passant). Le type I, considéré comme le plus fréquent et de fait préféré pour les essais, est étudié ici.

## 2. ORIGINALITE DES TRAVAUX

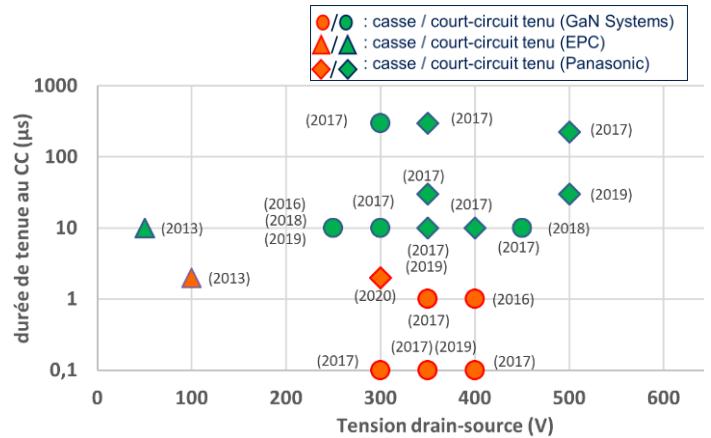

L'étude des courts-circuits a débuté il y a déjà quelques années, avec des premiers travaux publiés en 2013 [9]. Elle reste cependant limitée sur plusieurs aspects. La technologie normally-off des composants p-GaN et cascode a été étudiée de façon quasi-exclusive. La figure 1 illustre l'étendue des études pour les composants p-GaN, tout en notant que les plus hautes tensions n'ont pu être atteintes qu'au prix de concessions (environnement surchauffé, résistance de grille augmentée). Très peu, voire aucun papier, ne s'intéresse à la technologie normally-on elle-même. De plus, les études actuelles s'intéressent majoritairement à la tenue des composants face à

un court-circuit monocoup et à la durée avant défaillance. Nous pourrons ainsi étudier l'impact direct des courts-circuits sur une puce normally-on et voir quelles sont les conclusions à tirer pour les structures cascodes. De plus, l'analyse des dégradations permettra dans un second temps d'identifier les mécanismes associés et ainsi de participer à la conception de puces plus robustes en court-circuit.

Figure 1 : état de l'art bibliographique des études en court-circuit, destructifs sur composants p-GaN [1]–[8].

Les travaux présentés ci-après s'en distinguent selon plusieurs façons : des composants normally-on, de technologie MISHEMT (HEMT à grille isolée [1]) ainsi que des composants normally-off cascodes sont choisis. La technologie cascode présente l'avantage d'être, pour ce qui est de la partie GaN, identique au normally-on et de fait permet d'effectuer des comparaisons à propos du mécanisme de défaillance. De plus, il a été choisi d'étudier l'impact de courts-circuits répétitifs, non destructifs. La destruction du composant complique son étude approfondie. De plus, dans une application réelle, l'objectif est de n'avoir que des courts-circuits non destructifs, se répétant quelques fois dans la vie du convertisseur. L'étude des dégradations induites est donc un point clef. Dans notre étude, les courts-circuits non destructifs sont entrecoupés de caractérisations électriques afin de relever les possibles variations paramétriques et de mieux identifier les mécanismes de dégradation.

Tableau 1 : Principales caractéristiques initiales des composants étudiés

| Type de composant | V <sub>th</sub> | I <sub>D max</sub> | R <sub>D(on) max</sub> | V <sub>DS max</sub> |

|-------------------|-----------------|--------------------|------------------------|---------------------|

| MISHEMT           | -12.5 V         | 10 A               | 250 mΩ                 | 650 V               |

| CASCODE           | 1.8 V           | 10 A               | 250 mΩ                 | 650 V               |

### 3. CHOIX TECHNIQUES

Les précédents travaux liés aux courts-circuits font souvent état de surtensions importantes ( $>100$  V) limitant la plage de tension drain-source lors des essais en court-circuit [9]. Du fait des fronts de courant très rapides propres à la technologie GaN, la moindre inductance parasite dans la boucle de puissance implique une surtension au niveau du composant et s'avère délétère.

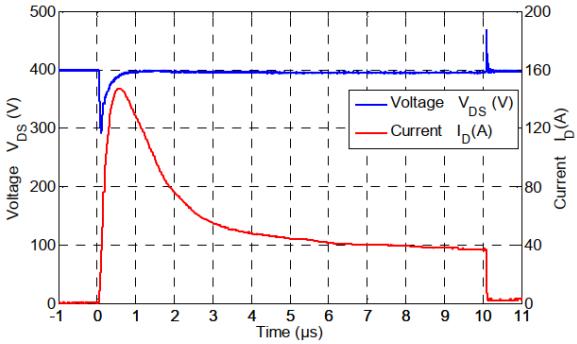

Figure 2 : Tension drain-source et courant de drain caractéristiques lors d'un court-circuit [1]

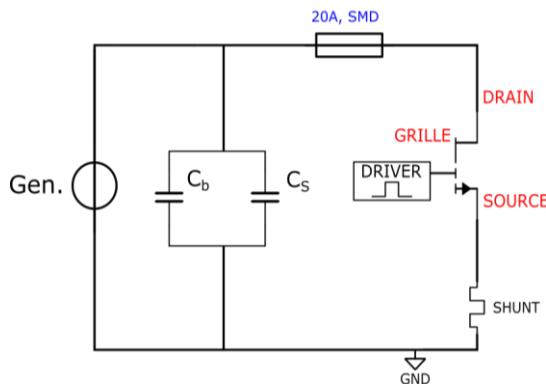

Pour les DUT étudiés, avec un courant de court-circuit autour de 50 A (estimation basse) et un temps de commutation caractéristique de 20 ns, une inductance parasite de 80 nH (soit l'équivalent de 8 cm de piste sur le PCB) occasionne 200 V de surtension ! Le circuit a donc été conçu de façon à réduire au maximum ces inductances. L'organe de protection, souvent un IGBT, considéré comme fortement inductif, est ici remplacé par un fusible CMS qui permet tout de même de préserver le composant avant sa destruction totale. Afin de reproduire les conditions d'un court-circuit et notamment l'établissement très rapide d'un fort courant, tout en minimisant la chute de tension, deux capacités respectivement de 2  $\mu$ F (céramique, Cs) et 133  $\mu$ F (polypropylène, Cb) sont branchées en parallèle.

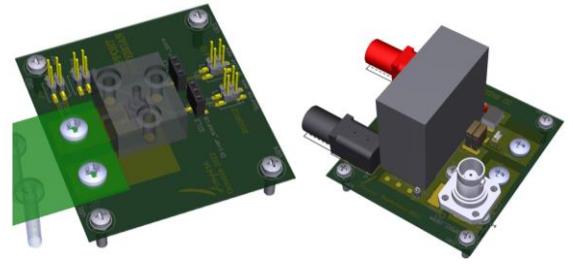

Le banc de test est composé de trois éléments clés : la carte puissance comportant les condensateurs, fusible et le shunt de mesure de courant ; la carte fille « device » comportant le transistor encapsulé dans son sarcophage, ainsi que la partie driver permettant la commande en -24 V / 0 V.

Figure 3 : schéma électrique du banc de test

Figure 4 : cartes fille « device » (à gauche) et carte puissance (à droite)

Les phases de courts-circuits sont entrecoupées de caractérisations électriques afin d'identifier les dérives de paramètres électriques. Afin de réduire les manipulations de composant, pouvant affecter ces propriétés électriques, la carte fille a été conçue de façon à pouvoir être facilement connectée au traceur de caractéristiques B1505. De plus, afin de ne pas avoir à souder / dessouder les composants sur cette carte fille, et ainsi occasionner des contraintes thermiques non négligeables, un sarcophage a été élaboré par impression 3D afin de tenir le composant et d'assurer la conduction par pression (Figure 5). Des caractérisations électriques similaires avec un composant brasé ont permis de s'assurer que le sarcophage n'entrave pas les propriétés électriques du composant.

Figure 5 : sarcophage obtenu par impression 3D

### 4. MISE AU POINT DU BANC EXPERIMENTAL

#### 4.1 Des surtensions trop importantes

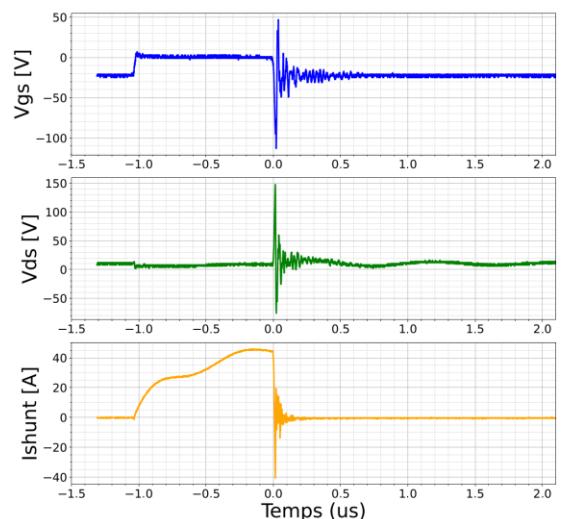

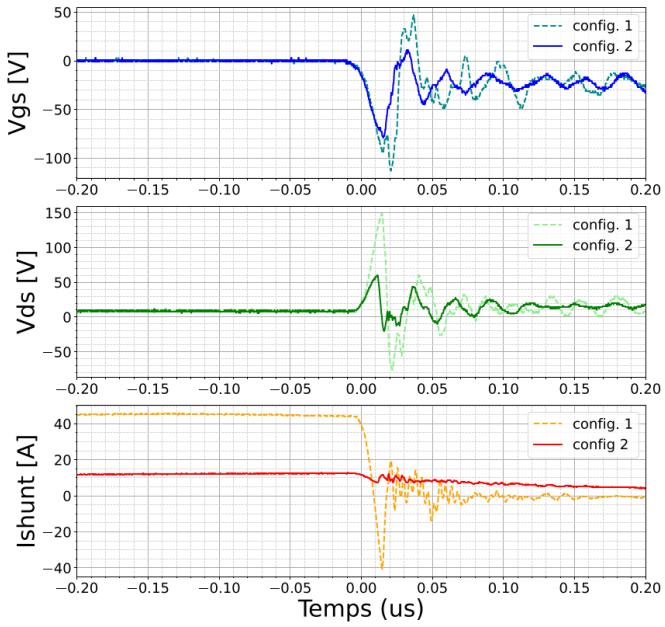

Les premières manipulations se sont concentrées sur le composant normally-ON et donnent les résultats sur le graphe ci-après Figure 6. On retrouve les formes de courant et tension caractéristiques durant un court-circuit.

Figure 6 : essai en court-circuit pour  $V_{DS} = 10$  V

Comme expliqué précédemment, le but de l'étude réside dans l'analyse de l'impact des courts-circuits sur les composants HEMT en nitride de gallium. Or, si le turn-ON ne présente pas de perturbation, ce n'est pas le cas du turn-OFF qui fait apparaître des surtensions très importantes. Nous avons alors pu distinguer deux configurations distinctes du banc expérimental. La première configuration apparaît très délétère pour le composant avec des surtensions importantes au turn-OFF visibles Figure 6. Pour une tension d'alimentation fixée à  $V_{DS} = 10$  V, le signal  $V_{DS}$  avoisine les 150 V, présentant ainsi une surtension de 140 V. Le signal  $V_{GS}$  présente aussi de fortes perturbations jusqu'il dépasse brièvement les -100 V, à mettre en parallèle de la valeur négative maximale de -50 V pour le signal  $V_{GS}$  donnée par le fabricant.

Figure 7 : photo du banc expérimental (plan large en haut) et zoom de la configuration 1 (en bas à gauche) et de la configuration 2 (zoom en bas à droite).

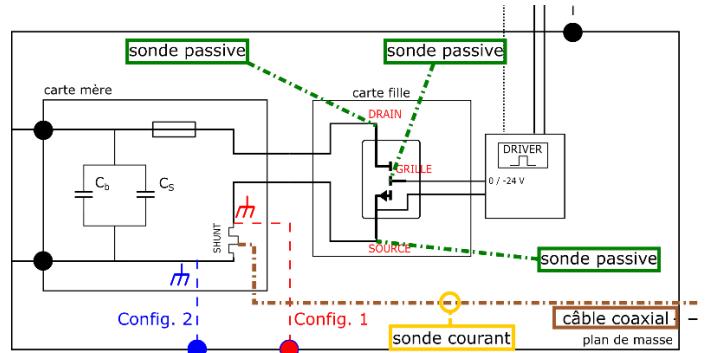

Afin de se focaliser sur l'influence des courts-circuits et réduire l'impact que peut avoir le banc sur la dégradation du composant, une deuxième configuration a été élaborée afin de réduire ces effets parasites. La liaison au plan de masse est déplacée. Dans la configuration 1, elle se situait du côté de la masse du composant, dans la seconde configuration, cette liaison se trouve désormais du côté de la masse de l'alimentation haute-tension. Le sens du shunt et la position de sa broche masse s'en trouvent alors également inversés comme explicité sur la Figure 8.

Figure 8 : schéma de principe illustrant les deux configurations du banc

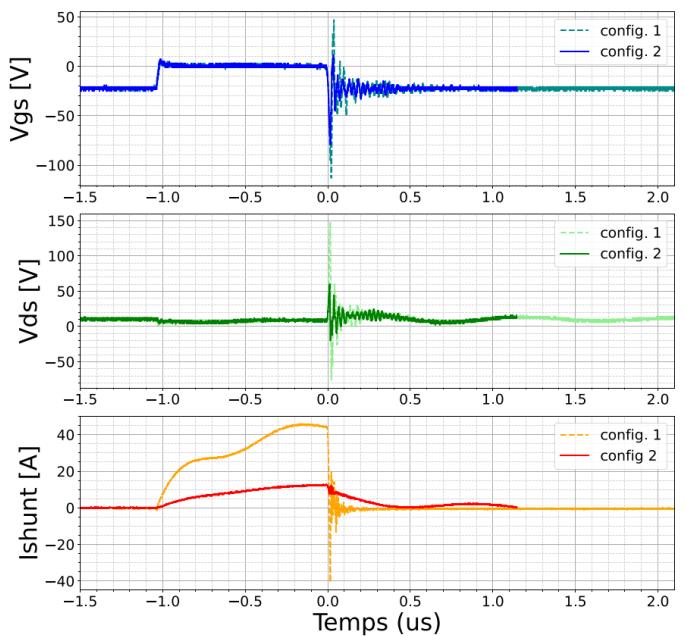

La Figure 9 présente une superposition des signaux  $V_{DS}$  et  $V_{GS}$  selon le type de configuration du banc expérimental. La Figure 10 zoomé sur la partie turn-OFF, zone présentant le plus de perturbation. Le signal  $V_{GS}$ , s'il présente toujours une surtension négative, est désormais réduite avec un passage des extrema initiaux de -110 V/+45 V à désormais -80 V/+10 V. L'évolution du signal  $V_{DS}$  est encore plus marquée et présente une réduction significative de ses extrema avec un passage de -80 V/+150 V à -20 V/+60 V.

Figure 9 : essai en court-circuit pour  $V_{DS}=10$  V (configurations 1 et 2)

Figure 10 : essai en court-circuit pour  $V_{DS} = 10$  V (vue zoomée)

Tableau 2 : extrema des signaux  $V_{GS}$  et  $V_{DS}$  selon les deux configurations expérimentales

|                    | Configuration 1 | Configuration 2 |

|--------------------|-----------------|-----------------|

| Extrema - $V_{DS}$ | -80 V           | -20 V           |

| Extrema + $V_{DS}$ | +150 V          | +60 V           |

| Extrema - $V_{GS}$ | -110 V          | -80 V           |

| Extrema + $V_{GS}$ | +50 V           | +10 V           |

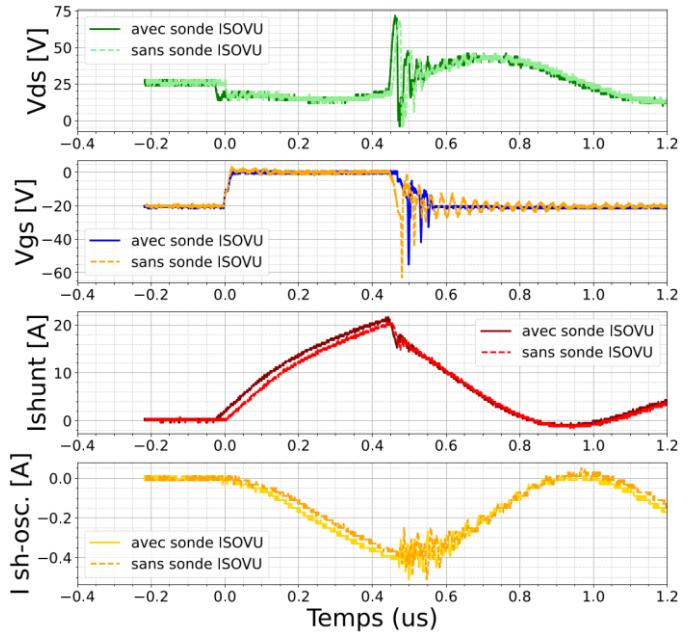

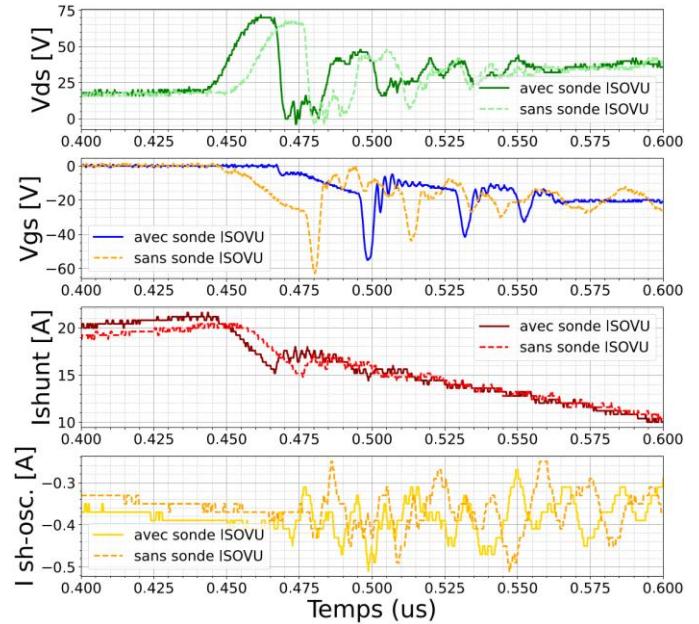

#### 4.2 Impact des sondes sur le signal $V_{GS}$

On peut noter qu'en dépit d'une configuration plus stable (n°2) du banc expérimental, le signal  $V_{GS}$  présente tout de même une surtension négative non négligeable. Dès lors la question se pose de savoir si la surtension est véritablement vue par le composant ou s'il s'agit d'un artefact des sondes de mesures. On compare alors le signal  $V_{GS}$  suivant deux protocoles de mesure distincts. Le premier consiste à utiliser deux sondes passives de référence TEKTRONIX TPP0500B pour mesurer  $V_G$  et  $V_S$  et calculer la différence afin d'obtenir  $V_{GS}$ . Le second protocole de mesure passe par l'utilisation d'une sonde ISOVU de référence TIVH05 délivrant directement le signal  $V_{GS}$ , de façon plus précise. La tension de travail  $V_{DS}$  est désormais fixée à 25V.

Figure 11 : essai en court-circuit avec ou sans sonde ISOVUE sur le signal  $V_{GS}$

La Figure 11 ainsi que la Figure 12 superposent les signaux, avec la mesure du signal  $V_{GS}$  par les sondes passives ou par la sonde ISOVU. Dans les deux cas on retrouve pour le signal  $V_{GS}$  des surtensions négatives non négligeables. Ces surtensions ne sont donc pas des artefacts des sondes passives. La circulation d'un courant de mode commun est à noter dans le câble coaxial liant le shunt à l'oscilloscope ainsi que dans les câbles d'alimentation du driver.

Figure 12 : essai en court-circuit avec ou sans sonde ISOVU sur le signal  $V_{GS}$  (zoom turn-OFF)

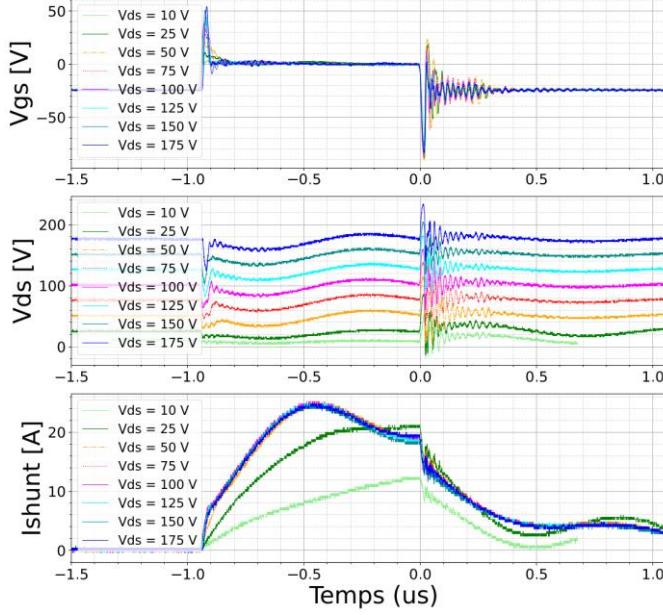

#### 4.3 Montée progressive en tension

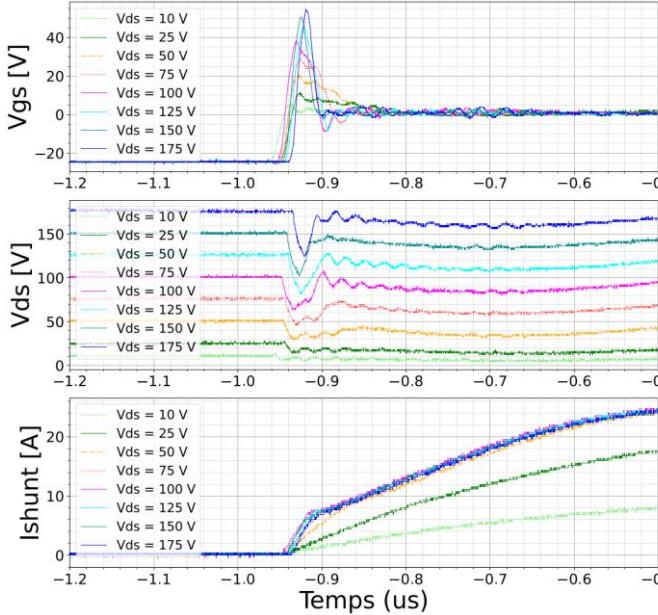

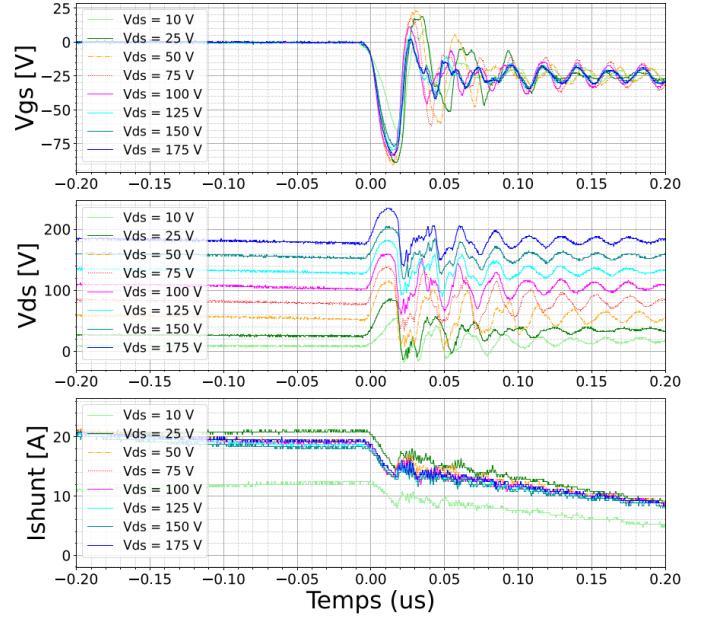

La réduction maximale des perturbations a permis d'envisager une montée progressive en tension  $V_{DS}$  de 0 V à 200 V. Les figures ci-dessous illustrent cette montée en tension jusqu'à 175 V, le composant ayant cassé pour  $V_{DS} = 200$  V.

Figure 13 : essai en court-circuit avec une montée en tension  $V_{DS}$  progressive.

Figure 14 : essai en court-circuit avec une montée en tension  $V_{DS}$  progressive (zoom turn-ON)

Figure 15 : essai en court-circuit avec une montée en tension  $V_{DS}$  progressive (zoom turn-OFF)

Les surtensions du signal  $V_{GS}$  au turn-OFF restent similaires durant la montée en tension. On note cependant l'apparition d'une surtension positive au turn-ON sur le signal  $V_{GS}$ . Celle-ci disparaît avec l'ajout d'un temps de repos du composant entre chaque court-circuit.

La stabilité des mesures et la possible montée en tension  $V_{DS}$  a permis de débuter le plan de caractérisation composé de cycles de court-circuit, entrecoupés de caractérisations électriques.

Nous continuerons à analyser les perturbations afin de les réduire au minimum. En effet dans la configuration actuelle, nous pouvons nous poser la question de savoir si les dégradations observées sont dues au court-circuit lui-même ou aux perturbations induites par l'ouverture. Dans les convertisseurs d'électronique de puissance, il n'y a pas de dispositifs de mesure et protection additionnels, ce qui permet a priori de réduire fortement les perturbations.

## 5. RESULTATS

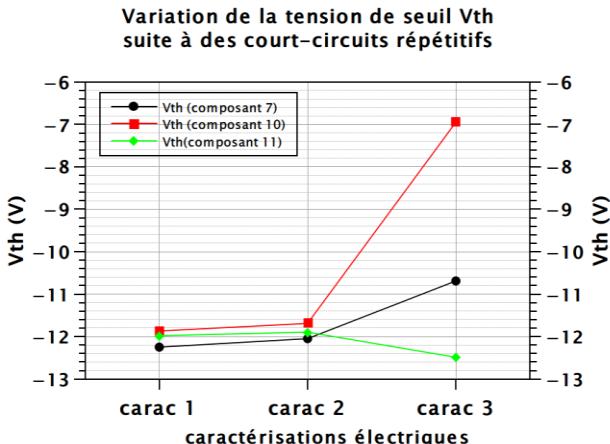

Chaque cycle de courts-circuits est constitué d'une montée progressive en tension  $V_{DS}$  de 0 V à 100 V suivie de quatre autres courts-circuits de 100 V. Chaque court-circuit est entrecoupé d'un temps de repos de cinq minutes. Le composant est caractérisé avant et après chaque cycle. Une variation de la tension  $V_{th}$  a pu être observée. Cela peut s'avérer d'autant plus préjudiciable que dans le cas d'une structure cascode, si le  $V_{th}$  de la puce GaN se rapproche trop de la valeur zéro, la mise off ne serait plus effectuée correctement, avec un risque inhérent de destruction.

Figure 16 : variation de la tension de seuil  $V_{th}$  suite à des cycles de courts-circuits à 100 V.

Ainsi, nous avons clairement obtenu dans certains cas des dégradations au moins sur le  $V_{th}$  après des essais répétés de courts-circuits répétitifs non destructifs. Toutefois et comme déjà annoncé, ces dégradations pourraient aussi être dues aux perturbations à l'ouverture qui ont été constatées.

## 6. CONCLUSIONS

Le banc de test est fonctionnel et a permis de mettre en avant des dégradations de la tension de seuil  $V_{th}$  au sein des composants soumis à des courts-circuits répétitifs non destructifs. Des simulations électriques Spice sont également à l'étude afin de mieux comprendre le comportement du banc expérimental et donc de réduire au maximum les perturbations liées à l'ouverture après court-circuit

## 7. REFERENCES

- [1] M. Landel *et al.*, « Dispersion of electrical characteristics and short-circuit robustness of 600V E-mode GaN transistors », *PCIM Europe 2017*.

- [2] C. Abbate, F. Iannuzzo, et G. Busatto, « Thermal Instability during Short Circuit of Normally-Off AlGaN/GaN HFETs », *Microelectronics Reliability*, 2013.

- [3] T. Oeder, « Electrical and thermal failure modes of 600V p-gate GaN HEMTs », *Microelectronics Reliability*, 2017.

- [4] X. Huang *et al.*, « Experimental Study of 650V AlGaN/GaN HEMT Short-Circuit Safe Operating Area (SCSOA) », *26th International Symposium on Power Semiconductor Devices & IC's*, 2014.

- [5] M. Riccio *et al.*, « Experimental analysis of electro-thermal interaction in normally-off pGaN HEMT devices », *2018 IEEE International Conference on Electrical Systems for Aircraft, Railway, Ship Propulsion and Road Vehicles & International Transportation Electrification Conference (ESARS-ITEC)*, DOI: 10.1109/ESARS-ITEC.2018.8607347

- [6] H. Li *et al.*, « Robustness of 650 V Enhancement-Mode GaN HEMTs under Various Short Circuit Conditions », *IEEE Transactions on Industry Applications*, 2019, DOI 10.1109/TIA.2018.2879289, IEEE.

- [7] M. Fernández *et al.*, « Short-Circuit Study in Medium Voltage GaN Cascodes, p-GaN HEMTs and GaN MISHEMTs », *IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS*, 2017, DOI: 10.1109/TIE.2017.2719599

- [8] P. J. Martínez, « Unstable behaviour of normally-off GaN E-HEMT under short-circuit », *Semicond. Sci. Technol.*, 2018, DOI:10.1088/1361-6641/aab078.

- [9] M. Landel, « Étude de la robustesse de transistors GaN en régime de court-circuit » Université Paris-Saclay, thèse, 2022.