# Méthode de préconditionnement du HEMT GaN pour une mesure reproductible de $V_{th}$

L. Ghizzo<sup>(1,2,3)</sup>, D. Trémouilles<sup>(2)</sup>, F. Richardau<sup>(3)</sup>

<sup>(1)</sup>THALES SIX France SAS, Toulouse – <sup>(2)</sup>LAAS-CNRS, Université de Toulouse, CNRS

<sup>(3)</sup>LAPLACE, Université de Toulouse, CNRS, INPT, UPS, Toulouse

**RESUME** – Dans les études de fiabilité, l'instabilité de la tension de seuil ( $V_{th}$ ) est problématique lorsque  $V_{th}$  est utilisé comme indicateur car elle masque une éventuelle dérive due au vieillissement réel du composant. Cette instabilité est observée lors des mesures de caractérisation électrique. Elle est liée à "l'historique de polarisation" du transistor qui peut introduire un phénomène de piégeage/dépiégeage de porteurs dans différentes couches de la structure. De nouvelles méthodes sont donc nécessaires pour surmonter ces problèmes d'instabilité liés au piégeage afin de surveiller avec précision le vieillissement des transistors en GaN. Pour résoudre le problème de répétabilité de la mesure de la tension de seuil, nous avons étudié son instabilité sur les transistors GaN. Une étape de préconditionnement appliquée juste avant la mesure réelle de  $V_{th}$  a été étudiée. La méthode de préconditionnement proposée est basée sur l'application d'une polarisation  $V_{GS}(t)$  dédiée sur l'électrode de grille qui conduit à une valeur stable et répétable de  $V_{th}$ . Les mécanismes permettant la stabilité observée de  $V_{th}$  sont identifiés grâce à l'analyse de la mesure de fuite de drain après la mesure préconditionnée de  $V_{th}$ . La modification de la courbe de fuite démontre le rôle de l'injection de trous dans la structure. La méthode de mesure préconditionnée- $V_{th}$  est proposée comme mesure complémentaire pour suivre correctement le vieillissement du p-GaN HEMT dans les futures études de fiabilité.

*transistor p-GaN Schottky, protocole de préconditionnement, fiabilité, variation de la tension de seuil, piégeage*

## 1. INTRODUCTION

La mesure des caractéristiques électriques est souvent utilisée pour suivre la dégradation des transistors dans les études de fiabilité. Cependant, dans les transistors à haute mobilité électronique AlGaN/GaN (HEMT), les mesures ne sont souvent pas reproductibles et peuvent varier en fonction de l'historique des opérations précédentes, ce qui rend délicat l'interprétation du décalage lié à la dégradation du transistor. En particulier, l'instabilité de  $V_{th}$  a été observée [1].

Néanmoins, des mesures de caractérisation reproductibles sont indispensables pour étudier la dégradation irréversible et la dérive des paramètres électriques des transistors.

Nous avons étudié une étape de préconditionnement avant la mesure  $V_{th}$  pour la stabiliser et la rendre parfaitement reproductible. Certaines méthodes de préconditionnement ont été proposées pour les dispositifs SiC [2][3][4]. Le préconditionnement pour les dispositifs GaN est très nouveau et semble n'être rapporté que dans les travaux récents de A. Deb [4]. Par rapport au travail proposé ici, il adopte une vision plus expérimentale avec des explications physiques limitées et présente des étapes de préconditionnement avec des amplitudes et des durées d'impulsion de tension de grille différentes de celles décrites dans cet article.

Pour identifier les mécanismes qui se sont produits au cours de l'étape de préconditionnement proposée, des mesures supplémentaires ont été effectuées après les mesures  $V_{th}$  préconditionnées.

La section 2 illustre l'instabilité de la tension de seuil et présente le montage expérimental. Le protocole de préconditionne-

ment de grille est expliqué en détail dans la section 3. La section 4 présente les observations sur la fuite de drain après le préconditionnement et une analyse des mécanismes physiques à l'origine de cette fuite particulière qui assurent la stabilité de la valeur  $V_{th}$  préconditionnée.

## 2. INSTABILITÉ DE LA MESURE ET PRÉCONDITIONNEMENT.

Le principal dispositif sous test (DUT) est un HEMT commercial AlGaN/GaN, 100 V, 90 A, 7 mΩ à grille p-GaN Schottky. Le même protocole a également été appliqué sur un composant de calibre 650 V, 30 A, 50 mΩ du même fabricant.

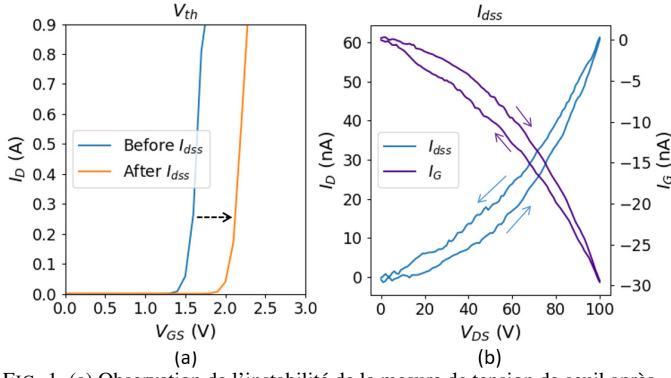

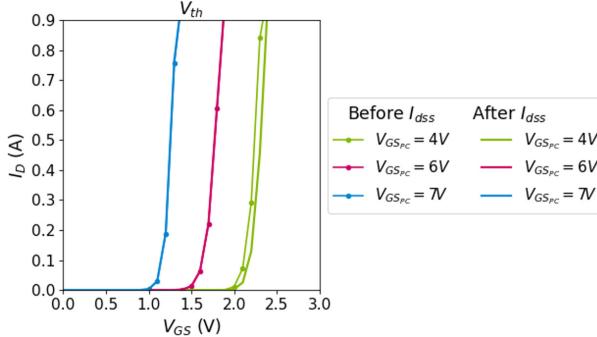

Dans notre configuration, la tension de seuil ( $V_{th}$ ) est mesurée en augmentant simultanément les tensions de grille et de drain (la mesure se comporte donc comme si les bornes de drain et de grille étaient court-circuitées ensemble). La valeur  $V_{th}$  a été choisie comme valeur de tension de grille lorsque le courant de drain  $I_D$  est égal à 400 mA. Cette valeur est suffisamment élevée pour être sur la partie linéaire des courbes de la Fig.1(a) et mesurer précisément la dérive. Comme la durée de la mesure  $V_{th}$  est très courte (bien inférieure à la seconde), la valeur mesurée n'est pas significativement influencée par l'effet d'auto-échauffement.

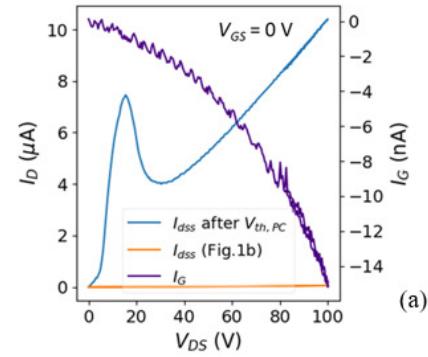

Comme dans [1] et [5] nous avons observé que la tension de seuil est instable en fonction de l'historique du transistor. Par exemple,  $V_{th}$  sera décalé positivement, jusqu'à 40 % après la mesure de fuite de drain  $I_{dss} = f(V_{DS})$  à  $V_{GS} = 0V$  à cause de la haute tension et du champ électrique élevé Fig.1(b).

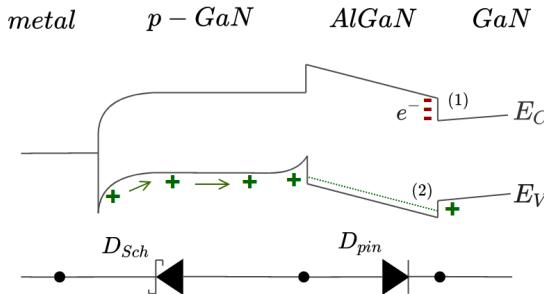

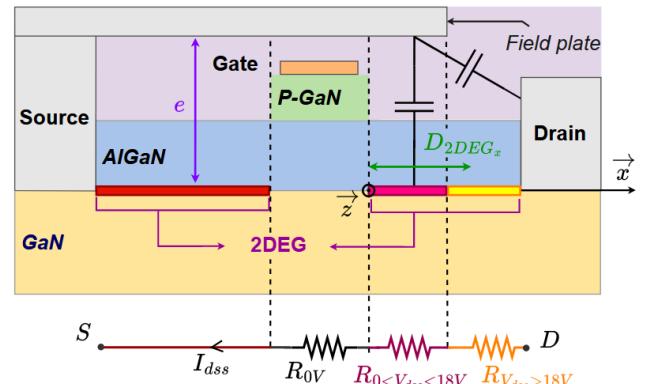

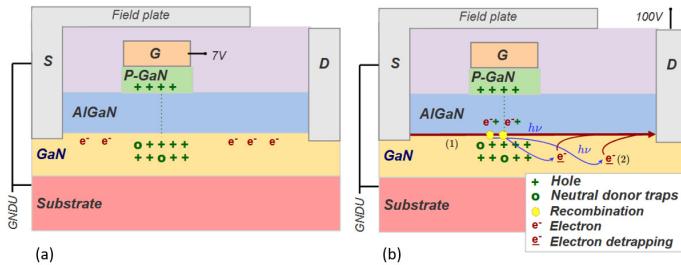

Ce décalage positif (augmentation de  $V_{th}$ ) est attribué à deux mécanismes distincts selon [6]. L'un d'eux est un mécanisme de piégeage d'électrons à l'interface AlGaN/GaN provoqué par les 100 V appliqués sur le drain à l'état OFF lors de la mesure  $I_{dss}$ . Les électrons piégés n'ont pas le temps d'être libérés avant la mesure de tension de seuil qui suit la mesure de  $I_{dss}$  (10 à 20 minutes sont nécessaires pour retrouver la valeur initiale de  $V_{th}$ ). L'autre mécanisme apparaît lorsque le courant de fuite de la diode Schottky  $D_{Sch}$  (représentée sur la Fig.2) est suffisamment élevé pour polariser et amorcer la diode pin  $D_{pin}$ . Un courant de trous, limité par  $D_{Sch}$ , peut traverser l'empilement de grille et la barrière vers le tampon. Le déplacement des charges positives (trous) qui étaient partiellement dans le p-GaN rend les charges négatives majoritaire dans la couche p-GaN. Le courant de trous laisse une charge négative nette dans la couche P-GaN sous la grille.

Les deux mécanismes augmentent le potentiel électrique nécessaire pour activer le gaz d'électrons bidimensionnel (2DEG) dans le canal, c'est-à-dire augmentent  $V_{th}$ . Même si le décalage observé est non permanent et purement temporaire, il rend la surveillance de la dégradation du transistor fondée sur la surveillance de sa dérive des caractéristiques électriques très difficile.

FIG. 1. (a) Observation de l'instabilité de la mesure de tension de seuil après une mesure  $I_{dss}$  avec  $V_{dss}$  jusqu'à 100V (b) Mesure de la fuite de courant à  $V_{GS} = 0V$  de le transistor pendant le  $I_{dss}$  qui provoque le décalage de  $V_{th}$  de (a) (balayages avant et arrière pointés par les flèches). Toutes les mesures ont été effectuées à une température ambiante de 20 °C. La vitesse de balayage est de 33 V/s.

FIG. 2. Diagramme de bande simplifié de l'empilement de grille du DUT, le mécanisme (1) est le piégeage d'électrons à l'interface AlGaN/GaN, (2) est l'épuisement des trous au-dessus de la barrière pour atteindre la couche tampon.

### 3. PRÉCONDITIONNEMENT DE LA GRILLE

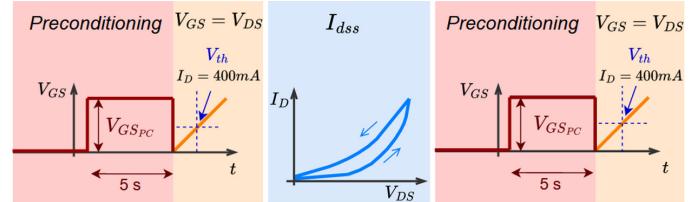

Le préconditionnement est appliqué juste avant la mesure de la tension de seuil à l'aide du mode *direct control* de l'analyseur de transistor de puissance et du traceur de courbe utilisés (Keysight B1505A). Ainsi, le temps entre l'étape de préconditionnement et la mesure de la tension de seuil est contrôlé avec précision.

Le préconditionnement consiste à appliquer une tension positive sur la grille pendant quelques secondes. Ce temps affecte la stabilité de la mesure et pourrait être minimisé avec d'autres études futures mais devrait être pris suffisamment long pour saturer les phénomènes et obtenir un résultat reproductible sur la valeur  $V_{th}$ . En effet, cette durée doit être suffisante par rapport à la constante de temps du mécanisme physique mis en jeu et pour atteindre la saturation de la densité de charge piégée détaillée plus loin. Nous n'avons pas encore trouvé d'autres études sur cette saturation.

Immédiatement après cette étape de préconditionnement, la mesure de  $V_{th}$  est effectuée en augmentant simultanément  $V_{GS}$  et  $V_{DS}$  (Fig.3).

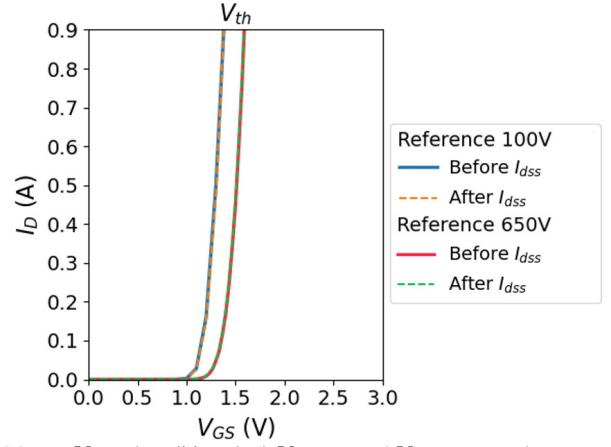

Afin de tester la reproductibilité de la mesure  $V_{th}$  et son indépendance par rapport à l'historique de polarisation du composant, une mesure préconditionnée de  $V_{th}$  après une mesure  $I_{dss}$  a été effectuée de la même manière que le  $V_{th}$  non préconditionné a été mesuré sur la Fig.1. Il est frappant de constater que la mesure préconditionnée de  $V_{th}$  est essentiellement reproductible et non affectée par l'historique (Fig.4). Ceci a été observé sur l'ensemble des seize composants testés sur cette référence. Pour évaluer la robustesse du préconditionnement proposé, ce processus a été répété avec succès avec d'autres conditions de polarisation, en plus de la mesure  $I_{dss}$  (polarisation sur la grille et le drain sans dépasser les limites recommandées par le fabri-

cant).

FIG. 3. Protocole utilisé dans les mesures sur le système de test : d'abord en rouge l'étape de préconditionnement de la grille pour obtenir des valeurs reproductibles de  $V_{th}$ , puis en orange la mesure réelle de  $V_{th}$ , en bleu une autre mesure (par exemple,  $I_{dss}$  sur la figure) pouvant influencer la mesure de la tension de seuil.

FIG. 4. Mesure  $V_{th}$  préconditionnée ( $\approx V_{GS,PC} = 7V$ ) avant et après une mesure  $I_{dss}$  pour un HEMT pGaN de 100 V et 650 V.

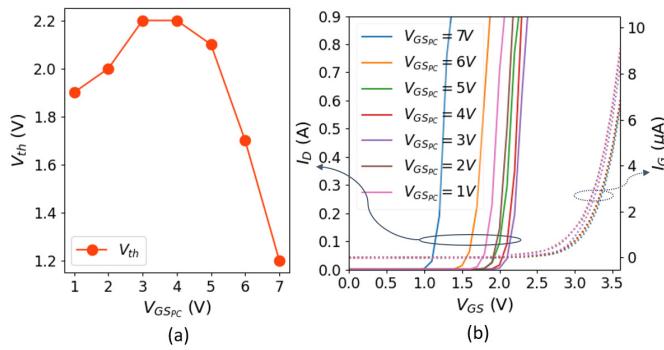

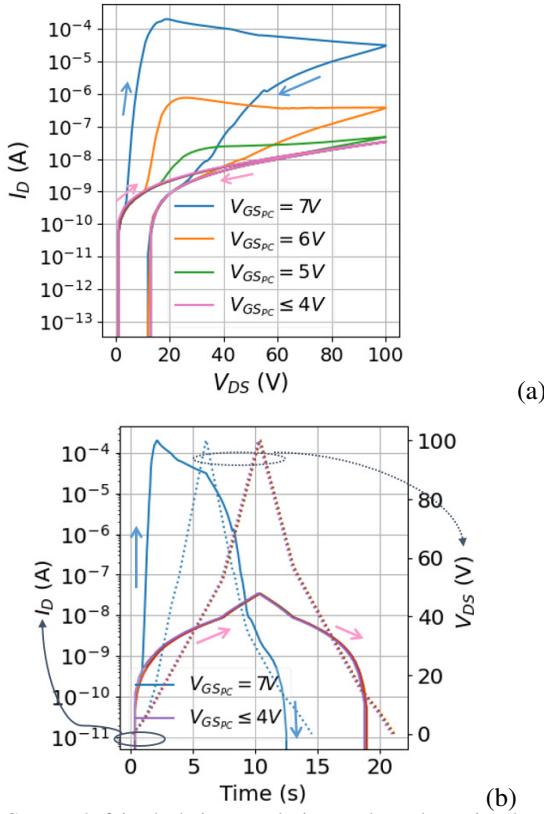

La mesure préconditionnée- $V_{th}$  est répétable et reproductible (Fig.4a). Les deux valeurs obtenues pour la tension de seuil diffèrent de moins de 0,1% ( $\approx 1mV$ ) pour deux références du même fabricant couvrant les calibres 100V et 650V.  $V_{th}$  n'est alors affecté que par l'étape de préconditionnement, cela permet de faire la mesure d'une valeur stable de  $V_{th}$ . Cette valeur varie en fonction de la tension de préconditionnement  $V_{GS,PC}$ . Il augmente pour  $V_{GS,PC}$  entre 1 et 4 V et diminue pour  $V_{GS,PC}$  entre 4 et 7 V (Fig.6). Les raisons de cette évolution sont expliquées dans le dernier paragraphe de la section 3. Une telle influence de la polarisation de grille sur le décalage de  $V_{th}$  a également été observée dans [7][8][9] sur transistors avec des structures similaires.

Il convient de souligner que seules les valeurs les plus élevées de  $V_{GS,PC}$  ( $> 5V$ ) conduisent à un  $V_{th}$  préconditionné stable, répétable et indépendant de l'historique de polarisation, comme indiqué dans la Fig.5. Par conséquent, il peut être conseillé de sélectionner la valeur  $V_{GS}$  la plus élevée autorisée. Dans le cas du composant testé testé la valeur  $V_{GS,PC} = 7V$  permet d'obtenir une mesure reproductible de la tension de seuil. Cette valeur ne doit pas dégrader le transistor ni affecter ses performances puisqu'elle s'inscrit dans les limites préconisées par le constructeur ( $V_{GS}$  dans la plage [-10V ; +7V] en mode DC) et aucun décalage de la valeur préconditionnée de la tension de seuil  $V_{th,PC}$  a été observée.

Sur la Fig.6 le décalage positif pour ( $V_{th} < V_{GS,PC} < 4V$ ) peut être expliqué par l'injection d'électrons du 2DEG vers la couche d'AlGaN cela se produit lorsqu'il y a suffisamment d'électrons dans le canal (mécanisme (1) sur la Fig.2) [9]. Le décalage négatif ( $V_{th}$  diminue) est observé pour  $V_{GS,PC} \geq 4V$  c'est-à-dire lorsque la grille commence à conduire à  $V_{GS} = 3V$  (seuil de tension de  $D_{pin}$ ) voir Fig.6b. A partir de cette tension, des trous commencent à traverser l'AlGaN, ce mécanisme provoque un piégeage de trous dans l'AlGaN et dans la couche tampon GaN (Fig.2(2))[7][8][10].

FIG. 5. Mesures de la tension de seuil avant (traits pleins pointillés) et après (traits pleins) une mesure  $I_{dss}$ . Les courbes de préconditionnement de 6 et 7 V sont les seules qui donnent exactement la même valeur de  $V_{th}$  car les courbes après et avant  $I_{dss}$  se recouvrent pour ces deux valeurs de préconditionnement. Pour des valeurs de préconditionnement plus petites, telles que  $V_{GSPC} = 4V$ , on peut voir que la mesure de  $I_{dss}$  influence la valeur de  $V_{th}$ .

FIG. 6. Effet de la tension appliquée lors de l'étape de préconditionnement sur la mesure de la tension de seuil (toutes les mesures sont effectuées après une mesure du courant de fuite  $I_{dss}$ ).

#### 4. COURANT DE FUITE APRÈS PRÉCONDITIONNEMENT.

##### 4.1. Observations

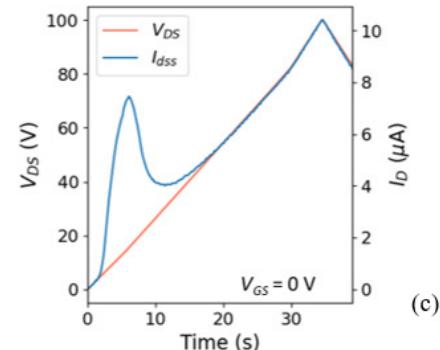

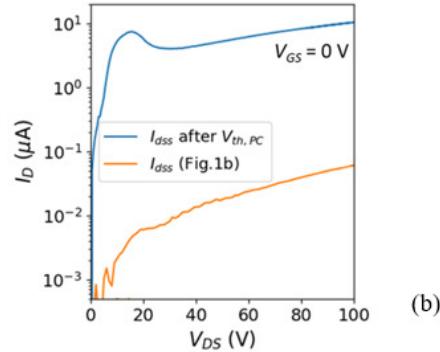

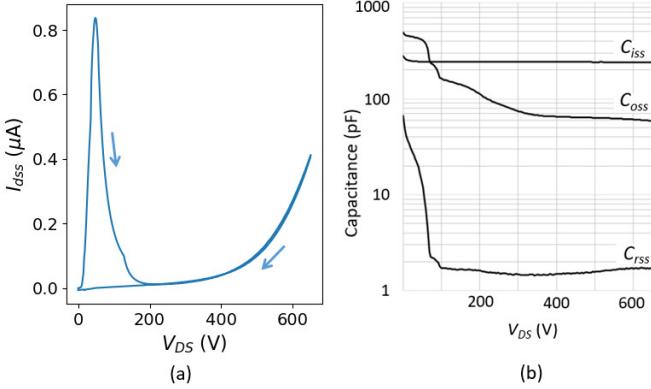

La courbe du courant de fuite entre les deux mesures de  $V_{th}$  sur la Fig.4a est visible sur la Fig.7. Par rapport à la mesure  $I_{dss}$  "normale" (Fig.1b), deux changements peuvent être observés du fait du préconditionnement : le courant moyen  $I_D$  est de trois ordres de grandeur plus grand qu'avant (comparaison du courant de drain atteint à 100 V pour  $V_{GSPC} = 7V$  par rapport à  $V_{GSPC} \leq 3V$ ), et un pic de  $7 \mu A$  se produit dans les premières 20 sec qui s'ajoutent au courant de fuite de drain existant. L'excès de courant disparaît après la mesure  $I_{dss}$ , c'est-à-dire qu'une autre mesure  $I_{dss}$  suivante donne une courbe "normale" (Fig.1b).

Les courants de drain pour différentes valeurs de  $V_{GSPC}$  sont représentés sur la Fig.9a. Ici le temps de balayage est plus court que lors de la mesure précédente (33 V/s contre 3 V/s auparavant) comme le montre la Fig.9b. Par conséquent, le "pic" de courant n'est pas entièrement évacué lors de l'incrémentation de la tension. L'augmentation du courant moyen est visible à partir de  $V_{GSPC} = 5V$ , comme le pic de courant, qui correspond au seuil d'injection de trous lors de l'étape de préconditionnement.

La forme en cloche de la pointe est influencée par la structure de la référence HEMT, en particulier sa disposition des plaques de champ. Les plaques de champ de la structure influencent l'évolution de la résistance du trajet du courant de fuite  $R$  pendant la mesure  $I_{dss}$ . A l'état OFF, l'étalement du 2DEG dans la région entre la grille et le drain ( $D_{2DEG_x}$ ) dépend de la tension  $V_{DS}$ . Au fur et à mesure que  $V_{DS}$  augmente, le 2DEG se retire progressivement entre la grille et le drain ce qui augmente la surface de blocage  $S_{blockage}$ , donc la résistance de chemin  $R$  augmente avec  $V_{DS}$ .

FIG. 7. (a) Mesure du courant de fuite de drain (avec une augmentation plus lente et constante de  $V_{DS} \approx 3V/s$ ) après une mesure préconditionnée de  $V_{th}$  ( $V_{GSPC} = 7V$ ), (échelle log sur (b)), à comparer avec la Fig.1b en orange. Le niveau global du courant de drain a augmenté anormalement (trois ordres de grandeur) et un pic de courant apparaît au début de la mesure et dure environ 20 secondes.

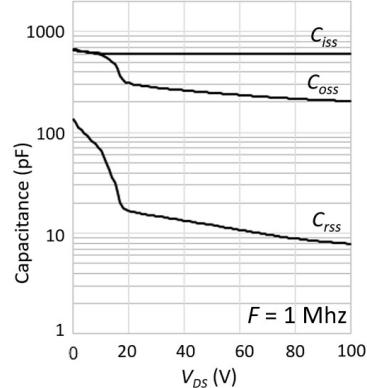

L'augmentation de  $S_{blockage}$  réduit également la valeur de capacité  $C_{DS}$ . L'évolution de  $C_{DS}$  par rapport à  $V_{DS}$  est souvent donnée par le constructeur et visible sur la Fig.10. Le retrait du 2DEG à l'état OFF peut alors être déduit. En effet lorsque la surface du 2DEG varie, la taille de l'électrode de la capacité équivalente varie ce qui affecte la capacité  $C_{DS}$ .

A l'état OFF, la région de blocage est sous le p-GaN uniquement pour  $V_{DS} = 0V$ . Sur la Fig.11, il s'agit de la région non colorée du 2DEG avec la résistance de chemin associée de  $R_{0V}$ .

Lorsque  $V_{DS}$  augmente entre 0 V et 18 V, le 2DEG se retire progressivement sous la plaque de champ :  $D_{2DEG_x}$  augmente dans la région rose de la Fig.11. La résistance de chemin vue par  $I_{dss}$  augmente jusqu'à  $R_{0V} + R_{0V < V_{dss} < 18V}$  à  $V_{DS} = 18V$ . À ce stade, le maximum du courant est atteint et commence à diminuer en raison de la forte augmentation de la résistance du chemin de fuite liée à la plaque de champ polarisée qui agit comme une grille polarisée négativement.

Lorsque  $V_{DS}$  continue d'augmenter, la "polarisation négative" relative de la plaque de champ atteint une valeur seuil qui dépend de l'épaisseur de la barrière AlGaN et de l'épaisseur de

FIG. 8. (a) Mesure du courant de fuite de drain après une mesure préconditionnée de  $V_{th}$  ( $V_{GS,PC} = 7$  V) pour la référence 650 V. Un pic de courant apparaît de la même manière qu'avec la référence 100 V, le maximum est atteint à  $V_{DS} \approx 100$  V. Un autre changement vers 150 V (moins prononcé) apparaît en raison de la disposition différente des plaques de champ de cette référence. (b) Capacité intrinsèque à  $V_{GS} = 0$  V du transistor sous  $V_{DS}$  donnée par la fiche technique du transistor. La disposition des plaques de champ est plus élaborée pour cette référence qui influence la variation de capacité avec  $V_{DS}$ .

FIG. 9. Courant de fuite de drain pour plusieurs valeurs de tension de grille de préconditionnement appliquées auparavant, (a) en fonction de la tension de drain appliquée, (b) évolution dans le temps de la tension et du courant de drain. Comme le balayage est plus rapide que sur la Fig. 7 (33V/s contre 3V/s), le pic de courant de fuite supplémentaire n'a pas le temps de s'évacuer uniquement sur la phase de balayage direct. Le courant supplémentaire du pic est évacué plus rapidement lors de la mesure avec un balayage plus rapide ( $\approx 12$ s contre 20s sur la Fig. 7), puisque la charge à évacuer est la même pour un même  $V_{GS,PC}$ , le courant maximal atteint est plus élevé à des vitesses de balayage plus rapides.

la couche isolante autour de l'empilement de grille ("e" dans la Fig.11), qui continue à retirer le 2DEG.

La forme exponentielle décroissante suivante sur la Fig.7

entre 18 et 40 V montre qu'il reste des charges à évacuer. Au-dessus de 18 V, le 2DEG continue de s'appauvrir dans la région jaune (plus lentement qu'avec une plaque de champ) ce qui augmente la résistance du chemin de fuite avec l'augmentation de  $R_{V_{dss}>18\text{V}}$ . La partie jaune du 2DEG sur la Fig.11 est entièrement retirée lorsque  $C_{OSS}$  est constante (au-dessus de 100 V).

La formule simplifiée suivante ainsi que la Fig.11 décrivent cette évolution de la résistance ( $\Delta R$ ) en fonction de  $S_{blockage}$  connaissant l'évolution de la capacité équivalente simplifiée  $C_{DS}$  du transistor donné en Fig.10 et illustré en Fig.11 :

$$\Delta C_{DS} = \frac{\epsilon \times (S - S_{blockage})}{e} \propto -\Delta R \quad (1)$$

Où  $e$  est son épaisseur (barrière AlGaN et couche isolante illustrées sur la Fig.11),  $\epsilon$  la permittivité équivalente de la capacité équivalente,  $S$  la surface où le 2DEG peut être formé et  $S_{blockage}$  est la surface de blocage du courant de drain à un  $V_{DS}$  donné.  $S - S_{blockage}$  peut être modélisé comme suit :

$$S - S_{blockage} = D_{tr_z} D_{tr_x} - D_{tr_z} D_{2DEG_z} \quad (2)$$

FIG. 10. Intrinsic capacitances at  $V_{GS} = 0$  V of the transistor under  $V_{DS}$  given by the transistor datasheet.

FIG. 11. Vue simplifiée du transistor et de l'emplacement du gaz d'électrons 2D pour un  $V_{DS} = V_{dss}$  donné. Le modèle équivalent du chemin de résistance est illustré ci-dessous. Les résistances rose ( $R_{0V}$ ) et jaune ( $R_{0V < V_{dss} < 18V}$ ) varient,  $R_{0V}$  est constante à l'état OFF.

Pour les autres références de p-GaN HEMT l'étalement du 2DEG sera affecté de la même façon par  $V_{DS}$ . Comme le HEMT 600 V p-GaN a une structure de plaque de champ différente avec des plaques de champ supplémentaires, le 2DEG sera retiré avec un plus grand nombre de sections. Chaque bordure de plaque ajoute une courbure sur la courbe  $C_{DS} = f(V_{DS})$  et ajoute un seuil de grille virtuelle qui retire le 2DEG au dessus d'un  $V_{DS}$  donné à l'état OFF.

## 4.2. Explication physique

L'impact de  $V_{GSPC}$  sur  $I_{dss}$  montre que l'injection de trous en quantité suffisante permet d'atteindre la saturation et est responsable à la fois du succès du préconditionnement et des conséquences sur le courant de fuite post mesure de  $V_{th}$  préconditionné.

FIG. 12. (a) Illustration des trous injectés dus à l'application d'un  $V_{GSPC}$  élevé, (b) effet sur le courant de fuite de drain, la flèche rouge épaisse illustre un flux de fuite élevé d'électrons, les nuages jaunes montrent processus de recombinaison qui émettent des électrons d'énergie  $h\nu$  qui libèrent l'électron piégé du tampon et qui participent à l'augmentation du courant de fuite.

Au cours de l'étape de préconditionnement à  $V_{GSPC} = 7\text{ V}$ , les trous atteignent le tampon sous la région de grille, voir Fig.12(a). Cette injection de trous abaisse  $V_{th}$  et affecte la capacité de blocage drain-source à l'état OFF du transistor sous tension, ce qui entraîne un courant de fuite de drain plus important pendant la mesure  $I_{dss}$  suivante ( $V_{GS} = 0\text{ V}$  et  $V_{DS} = 100\text{ V}$ )[11][12]. Donc ce phénomène, qui diminue la tension de seuil  $V_{th}$ , est aussi responsable de l'augmentation du courant de fuite moyen (l'ordre de grandeur de  $I_{dss}$  est  $\mu\text{ A}$  par rapport à  $\text{nA}$  sans ce phénomène).

Le courant supplémentaire qui apparaît au début de la mesure (Fig.7) pourrait s'expliquer par la recombinaison de paires électron-trou, cette recombinaison serait susceptible d'émettre un photon ayant une énergie suffisante pour ioniser les électrons piégés profondément dans la couche tampon comme illustré sur la Fig.12(b). Ces électrons sont dans le tampon GaN indépendamment du préconditionnement et sont une conséquence de la qualité de la couche tampon [13]. Ceux-ci seront libérés dans le canal créant le pic de courant observé. Ce phénomène est lié à la photo-conductivité persistante [10]. La même augmentation de l'amplitude du courant de fuite de drain avec une durée similaire jusqu'à l'équilibre (environ 30 secondes) a également été observée dans [14] [15] pour un transistor du même fabricant. La mesure de ce pic est un indicateur de la qualité de la couche tampon d'un transistor et pourrait être étudiée dans d'autres travaux futurs.

## 4.3. Conclusion du préconditionnement.

En ajoutant une étape de préconditionnement juste avant la mesure de la tension de seuil, il est possible d'obtenir des mesures  $V_{th}$  reproductibles.

Au cours de cette étape de préconditionnement, nous démontrons que la grille doit être polarisée en direct au-dessus de  $V_{th}$  près de la valeur  $V_{GS}$  la plus élevée admissible et suffisamment longtemps pour saturer le décalage négatif de la tension de seuil liée à l'injection de trous dans le tampon.

Les phénomènes observés sur la mesure du courant de fuite ( $I_{dss}$ ) après la mesure de la tension de seuil préconditionnée confirment que l'injection de trous est le mécanisme responsable de l'état préconditionné qui donne une valeur stable de  $V_{th}$ . L'augmentation du courant de fuite statique  $I_{dss}$  après la mesure préconditionnée  $V_{th}$  à l'état OFF et le flux supplémentaire d'électrons dans le courant de fuite sont une conséquence directe de la présence de trous provenant du séquence de préconditionnement. La méthode de préconditionnement est actuellement testée pour suivre le vieillissement des transistors et montre des résultats encourageants.

## 5. RÉFÉRENCES

- [1] Li X. et al,Observation of Dynamic VTH of p-GaN Gate HEMTs by Fast Sweeping Characterization,2020,IEEE Electron Device Letters, 10.1109/LED.2020.2972971

- [2] Rescher, G. and Pobegen, G. and Aichinger, T. and Grasser, T.,Preconditioned BTI on 4H-SiC : Proposal for a Nearly Delay Time-Independent Measurement Technique, 2018, IEEE Transactions on Electron Devices, 10.1109/TED.2018.2803283

- [3] JEDEC SOLID STATE TECHNOLOGY ASSOCIATION,Guidelines for measuring the threshold voltage (VT) of SiC MOSFETs, Version 1.03, January 2021,JEPE183

- [4] Deb, A. and Ortiz Gonzalez, J. and Bashar, E. and Jahdi, S. and Taha, M. and Mawby, P. and Alatise, O.,On the Repeatability and Reliability of Threshold Voltage Measurements during Gate Bias Stresses in Wide Bandgap Power Devices,2022,IEEE Workshop on Wide Bandgap Power Devices, Warwick, 10.1109/WiPDAEurope55971.2022.9936437

- [5] Murukesan, K. and Efthymiou, L. and Udrea, F., On the Challenges of Reliable Threshold Voltage Measurement in Ohmic and Schottky Gate p-GaN HEMTs,2021, IEEE Journal of the Electron Devices Society, 10.1109/JEDS.2021.3111809

- [6] Chen J. et al.,OFF-State Drain-Voltage-Stress-Induced VTH Instability in Schottky-Type p-GaN Gate HEMTs, 2021, IEEE Journal of Emerging and Selected Topics in Power Electronics, 10.1109/JESTPE.2020.3010408

- [7] Stockman A. et al.,On the origin of the leakage current in p-gate AlGaN/GaN HEMTs, 2018, IEEE International Reliability Physics Symposium (IRPS), 10.1109/IRPS.2018.8353582

- [8] Stockman, A. and Canato, E. and Meneghini, M. and Meneghesso, G. and Moens, P. and Bakeroot, B.,Schottky Gate Induced Threshold Voltage Instabilities in p-GaN Gate AlGaN/GaN HEMTs, 2021, IEEE Transactions on Device and Materials Reliability, 10.1109/TDMR.2021.3080585,

- [9] Tajalli A. et al.,2019,Impact of Sidewall Etching on the Dynamic Performance of GaN-on-Si E-Mode Transistors, 2019, IEEE International Reliability Physics Symposium (IRPS), 10.1109/IRPS.2019.8720445

- [10] Tang, X. and Li, B. and Moghadam, H. A. and Tanner, P. and Han, J. and Dimitrijev, S.,Mechanism of Threshold Voltage Shift in p - GaN Gate AlGaN/GaN Transistors, 2018, IEEE Electron Device Letters, 10.1109/LED.2018.2847669

- [11] Wang, Y. and Wei, J. and Yang, S. and Lei, J. and Hua, M. and K. J. Chen, Investigation of Dynamic IOFF Under Switching Operation in Schottky-Type p-GaN Gate HEMTs, 2019, 10.1109/TED.2019.2930315,

- [12] Li, X. and Xie, G. and Tang, C. and Sheng, K.,Charge trapping related channel modulation instability in P-GaN gate HEMTs,2016, Microelectronics Reliability, 10.1016/j.microrel.2016.07.040.

- [13] Raja, P. Vigneshwara and Bouslama, Mohamed and Sarkar, Sujan and Pandurang, Khade Ramdas and Nallatamby, Jean-Christophe and DasGupta, Nandita and DasGupta, Amitava, Deep-Level Traps in AlGaN/GaN- and AlInN/GaN-Based HEMTs With Different Buffer Doping Technologies, 2020, IEEE Transactions on Electron Devices, 10.1109/TED.2020.2988439

- [14] Tang, X. and Li, B. and Moghadam, H. A. and Tanner, P. and Han, J. and Dimitrijev, S.,Effect of Hole-Injection on Leakage Degradation in a p-GaN Gate AlGaN/GaN Power Transistor, 2018, IEEE Electron Device Letters, 10.1109/LED.2018.2849398

- [15] Li, B. and Jiang, Q., Liu, S. and Liu, C. and Chen, K.J., Degradation of transient OFF-state leakage current in AlGaN/GaN HEMTs induced by ON-state gate overdrive, 2014, Phys. Status Solidi C, 10.1002/pssc.201300445