# Transistors en diamant à effet de champ pour l'électronique de puissance : comparaison de grilles (JFET) et amélioration de la tenue en tension (MOSFET)

Martin KAH<sup>1,2</sup>, Damien MICHEZ<sup>2,3</sup>, Nicolas ROUGER<sup>2</sup>, Juliette LETELLIER<sup>3</sup>, Khaled DRICHE<sup>3</sup>, Marine COURET<sup>2</sup>, Anne CASTELAN<sup>2,4</sup>, Julien PERNOT<sup>1</sup>

<sup>1</sup>Institut Néel, <sup>2</sup>LAPLACE, <sup>3</sup>DIAMFAB, <sup>4</sup>ICAM

**RESUME** - Les transistors à effet de champ en diamant tirent bénéfice de ce matériau pour ajouter de nouveaux moyens de contrôle électro-optique, ou bien, repousser les limites de compromis tensions de claquage, résistance à l'état passant et température de jonction. Un nouvel état, actif sous illumination et passif dans l'obscurité, a été démontré expérimentalement sur des structures de type JFET (transistor à effet de champ via jonction). Pouvant servir de mémoire de par son caractère non-volatile, deux donneurs majoritaires de type n dans le diamant ont été étudiés de manière à obtenir les meilleures performances. En complément, le transistor MOSFET latéral à déplétion profonde a été démontré. Il présente, pour le moment, une tension de claquage de 175 V. Pour améliorer ce composant, une électrode de champ de type source field plate va être ajoutée et les simulations associées ont été réalisées. Elles montrent que le nouveau composant devrait avoir une tenue en tension entre 800 et 1000 V. Les propriétés de l'isolant utilisé ont été vérifiées expérimentalement, avec un champ critique mesuré de 10MV/cm.

**Mots-clés**—Diamant, Transistor de puissance, Effet de champ, Matériaux ultra grand gaps, JFET, MOSFET

## 1. INTRODUCTION

Les transistors de puissance en GaN et SiC ont apporté une rupture forte pour l'électronique de puissance : ils permettent d'améliorer les performances en conduction et en commutation, par rapport au Silicium [1]. Ils sont déjà optimisés sur plusieurs générations et sont intégrés dans les systèmes, notamment automobiles et grand public. La prochaine rupture sera apportée par les matériaux ultra grand gaps, tels que le diamant, qui permet théoriquement un champ électrique à l'état bloqué 50 (3) fois supérieur au Silicium (resp. SiC) [2]. En découle une division des pertes totales d'un facteur 3 par rapport au SiC, pour une surface 7 fois plus petite et une température de jonction pouvant être maintenue au-delà de 523 K, permettant une réduction extrême du système de refroidissement [2]. Les enjeux plus généraux associés au diamant pour l'électronique de puissance sont présentés dans la section suivante. Cet article présente ensuite les avancées récentes sur 2 types de transistors à effet de champ en diamant : le contrôle électro-optique de la grille type N du transistor à effet de champ par jonction PN (JFET), et l'amélioration de la tenue en tension d'un transistor à grille isolée utilisant le régime de déplétion profonde (D3MOSFET). Ces deux architectures s'appuient sur une conduction volumique entre Drain et Source d'un diamant type

p dopé bore lors de la croissance par MPCVD, avec une maîtrise précise du dopage et une faible densité de défauts.

## 2. RAPPEL DES APPROCHES EXISTANTES ET ENJEUX ASSOCIES AU DIAMANT POUR L'ELECTRONIQUE DE PUISSANCE

Pour l'électronique de puissance, les semiconducteurs doivent toujours s'améliorer en réduisant leur résistance à l'état passant, en augmentant le champ électrique à l'état bloqué, et en réduisant les pertes à chaque commutation. Ceci permet de toujours augmenter les rendements de conversion, et les densités de puissance. A l'échelle du système, la montée en tension permet de réduire les niveaux de courant, à puissance donnée, et donc de réduire les pertes. De façon complémentaire, l'augmentation des températures de jonction des semiconducteurs permet de réduire les systèmes de refroidissement (e.g. réduction du volume du refroidisseur ou passage d'un refroidissement liquide à refroidissement à air). Cependant, cette augmentation de température de jonction conduit de façon classique à une augmentation des pertes dans les semiconducteurs. Dans ce contexte, les matériaux ultra grands gaps tels que le diamant permettent a-priori d'aller encore plus loin dans ces compromis : réduction de la résistance à l'état passant spécifique (à tenue en tension donnée), augmentation des tenues en tension maximales tout en conservant des composants unipolaires, augmentation des températures de jonction. Ceci est permis grâce à l'augmentation du champ électrique à l'état bloqué et à l'augmentation du dopage de la zone de tenue en tension, ainsi que la faible concentration intrinsèque même à haute température.

Les approches existantes s'appuient majoritairement sur la croissance de diamant monocristallin, par homo-épitaxie ou hétéro-épitaxie. Les composants ayant les meilleures figures de mérite sont les composants verticaux, mais ils se heurtent encore à la difficulté de réaliser des substrats conducteurs à faible densité de défauts et faible résistivité, ainsi que des couches faiblement dopées de forte épaisseur et faibles densités de défauts. Les composants latéraux en diamant sont aujourd'hui les plus matures, répartis dans deux grandes catégories [2] : les transistors s'appuyant sur un gaz de trous bidimensionnels (2DHG, avec un compromis mobilité dans le gaz et concentration surfacique de porteurs), s'appuyant sur une terminaison de surface hydrogénée, et les transistors utilisant une conduction volumique dans une couche type p dopée au

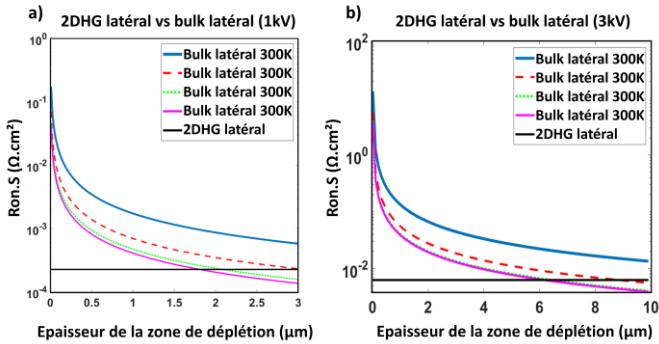

bore. Un comparatif des résistances spécifiques obtenable pour ces deux types d'architecture est présenté par la Figure 1.

Figure 1 :  $R_{on,S}$  en fonction de l'épaisseur de la zone de déplétion des transistors latéraux en diamant, en comparaison avec un transistor 2DHG, designés pour des tensions de claquage de a) 1 kV, b) 3 kV. Les paramètres de simulation sont détaillés dans [2].

Pour le moment, les meilleurs niveaux de courant ont été obtenus sur les transistors diamant FET à 2DHG [3-4], mais la maîtrise de la création du 2DHG et sa fiabilité notamment à haute température restent à encore démontrer. La maîtrise du dopage du diamant au bore, sur six décades en concentration de dopant, permet de répondre à de nombreuses briques nécessaires à la réalisation de composants en diamant (e.g. zone de tenue en tension, contacts ohmiques). Les enjeux associés au diamant et composants s'y appuyant restent encore la taille et la qualité des substrats, limitant par la suite la reproductibilité des procédés de fabrication et leur complexité nécessaire pour aller vers des architectures de composants performantes. En ce sens, le projet ANR LSD-MOSFET, MOSFET de grandes tailles en diamant, (<https://anr.fr/Projet-ANR-21-CE50-0036>) a pour ambition de réaliser de nouveaux transistors à effet de champ à grille isolée de grandes tailles en diamant sur des substrats de grandes tailles fonctionnant à haute tension / haute température. Le projet européen DCADE, Diamond Converter and Arc fault DEtection for high altitude operation (<https://cordis.europa.eu/project/id/101007868/fr>), propose d'implémenter au plus tôt les premiers transistors en diamant dans une application aéronautique, afin de démontrer les gains à l'échelle du système. Dans tous les cas, les architectures de transistors en diamant s'appuient sur une zone de tenue en tension type p dopée au bore, modulée par un effet de champ selon les régimes du transistor.

### 3. TRANSISTOR JFET : ETUDE DU DOPAGE TYPE N DE LA GRILLE

A cause de la forte énergie d'ionisation du phosphore (0,57eV) [5] et de l'azote (1,7eV) [6], le diamant dopé type n est isolant à température ambiante. Bien qu'une ionisation partielle soit atteignable pour le diamant dopé phosphore, grâce à un fort dopage [7-8], il n'a jusqu'à présent été démontré que selon l'orientation cristalline (111), direction reconnue pour faciliter son incorporation. Dans le cas d'un diamant monocristallin (100) dopé à l'azote ou bien au phosphore, l'absence totale d'électrons libres aux températures de fonctionnement des composants usuels, entraîne une impossibilité de contrôler électrostatiquement une jonction PN. La zone de charge d'espace (ZCE) n'est pas modulable par la polarisation des électrodes. Néanmoins, il est possible d'apporter par illumination, une énergie supérieure à l'énergie d'ionisation des dopants, et ainsi générer des électrons libres dans la couche de diamant dopé n. Grâce à ces porteurs photo-générés le contrôle électrostatique de la jonction PN est assuré, uniquement sous

apport d'énergie externe tel qu'une illumination ou bien des hautes températures.

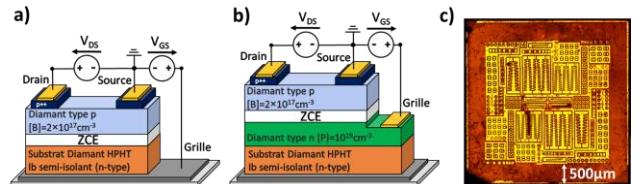

Ce principe, ayant premièrement été démontré sur jonction PN, est appliqué par la suite à la réalisation de transistors latéraux JFET en diamant monocristallin [9]. Récemment, deux types de grilles différentes ont été conçues, fabriquées et comparées, utilisant soit un substrat dopé azote (Figure 2 a)), soit une fine couche dopée phosphore (Figure 2 b)), réalisée in situ lors de la croissance CVD, en collaboration avec Arizona State University.

Figure 2 : Transistor latéral JFET en diamant. Vue en coupe, des échantillons utilisant comme grille: a) un substrat dopé azote et b) une fine couche dopée phosphore. c) image microscope optique des transistors inter-digité fabriqués.

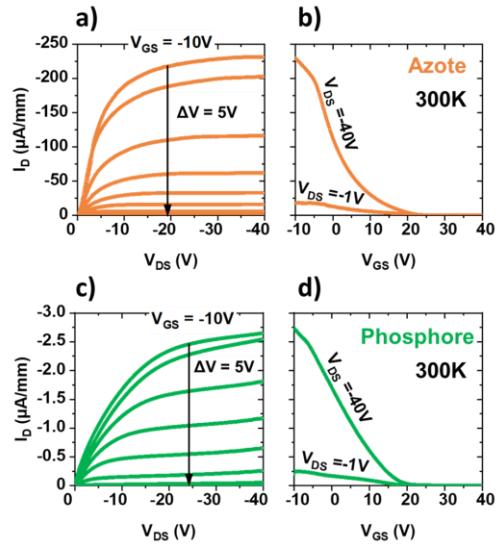

Les caractéristiques statiques IV ont été mesurées à température ambiante (Figure 3), démontrant le contrôle électrostatique des différents régimes du transistor grâce à la grille à jonction sous éclairage. Les deux transistors, étant normally-ON, passent dans leurs états bloqués pour des tensions de grille supérieure à  $V_{TH} = 20\text{ V}$  et présentent tous deux des courants de fuites inférieurs au  $\text{nA/mm}^2$  dans cet état. Le caractère innovant de la fine couche fortement dopée phosphore selon l'orientation cristalline (100) entraîne néanmoins une plus grande proportion de défauts dans la couche de type p qui la surpasse, comme en témoigne la différence de courant de saturation entre les deux échantillons. Le phosphore étant plus stérique que le carbone, des restructurations locales du réseau cristallin contraignent fortement cette couche, ce qui facilite ainsi la propagation et la création de dislocation lors de la reprise d'épitaxie de la couche de type p.

Figure 3 : Mesures IV à température ambiante des JFET fabriqués, sous illumination lumière blanche de  $11\text{ mW/mm}^2$ .  $I_D$  en fonction de a)  $V_{DS}$  et b)  $V_{GS}$  pour l'échantillon utilisant le susbrat dopé azote comme grille et  $I_D$  en fonction de c)  $V_{DS}$  et d)  $V_{GS}$  pour l'échantillon utilisant une fine couche dopée phosphore comme grille.

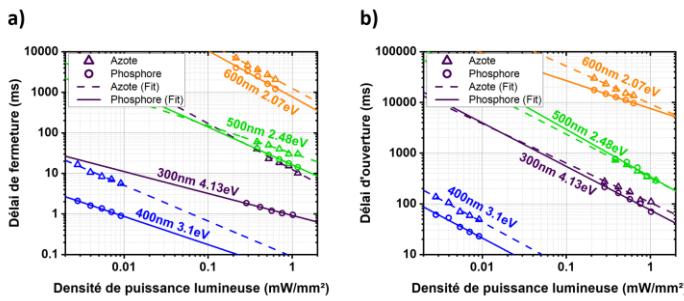

Le comportement électro-optique a aussi été caractérisé (e.g. effets de la longueur d'onde et de la puissance optique), en

statique mais aussi en dynamique, pour les 2 types de grille (azote et phosphore). Partant du principe que le processus d'ionisation des dopants est intrinsèquement dépendant de l'énergie ainsi que de la densité de puissance optique appliquée sur chaque structure, les temps de commutation de chaque transistor ont été mesurés sous différentes conditions d'éclairage (Figure 4). Les longueurs d'ondes utilisées et donc les énergies associées sont supérieures à l'énergie d'ionisation de l'azote en site substitutionnel dans le diamant ( $1,7\text{eV}$ ) sans quoi la génération d'électrons libres est impossible dans l'échantillon utilisant le substrat dopé azote comme grille. Le délai de fermeture est défini entre le moment où la tension de grille est appliquée pour fermer le canal de conduction et le moment où le courant de drain devient inférieur à 10% de sa valeur à l'état ON. Inversement, le délai d'ouverture est le temps requis pour que le courant de drain atteigne 90% de sa valeur maximal (à l'état ON), à partir du moment où la tension de grille est retirée.

La décroissance linéaire des délais d'ouverture et de fermeture des deux composants due à l'augmentation de densité de puissance optique peut dans un premier temps être modélisée au travers d'un circuit RC équivalent. La diminution de la résistance de grille interne induite par une augmentation drastique de la densité d'électrons libres, proportionnelle à la puissance d'éclairage, implique une diminution de la constante temporelle de fermeture ou d'ouverture du composant. De même lorsque l'énergie du flux lumineux augmente (e.g. la longueur d'onde diminue) les temps de fermeture et d'ouverture des canaux de conductions diminuent, excepté pour les illuminations inférieures à  $400\text{nm}$ . L'effet est proportionnel à l'augmentation de la section efficace d'ionisation d'un donneur lorsque l'énergie du flux lumineux augmente. Pour des longueurs d'ondes inférieures à  $400\text{nm}$  une chute de la transmittance du signal optique au travers le substrat a été observée. Une mise en série de résistance parasite apparaît et cause une augmentation des constantes temporelles de fermeture et d'ouverture sur les deux JFETs.

L'ajout d'une fine couche dopée phosphore permet néanmoins de diviser ces délais d'ouverture et de fermeture d'un facteur quatre, pour des illuminations identiques. En prenant en compte le fait que la couverture métallique présente sur les échantillons n'a pas été conceptualisée pour favoriser la collection lumineuse, un gain encore plus notable est attendu par l'optimisation de l'architecture de ces composants.

Figure 4 : Mesures a) du temps de fermeture et b) d'ouverture des transistors en fonction de la densité de puissance lumineuse reçue par les échantillons pour différentes longueurs d'ondes.

De nouvelles études complémentaires sur le comportement non volatile de ce type de JFET ont été réalisées, faisant suite à [9], et démontrant la complète isolation électrique de la grille sans illumination optique. L'activation optique du transistor permet d'une part l'activation et le contrôle électrostatique du

transistor mais aussi, lors du retrait de l'illumination, de geler l'état précédemment imposé au JFET durant sa mise sous lumière. Cet effet mémoire permet de tirer avantage de la profondeur des dopants de type n dans le diamant, en ajoutant un deuxième degré de liberté sur le contrôle de ces transistors utilisés comme photo-interrupteur non-volatile. Les perspectives d'application offertes par ces composants balayent un large spectre tel que l'électronique de puissance, grâce à une isolation galvanique parfaite de la grille sans éclairage, les télécommunications quantiques au travers du stockage non-volatile de l'état de charge d'un centre NV, mais aussi des implants biomédicaux chroniques, au sein desquels ces JFETs peuvent servir de brique de base à la réalisation de multiplexeur à division temporel.

#### 4. TRANSISTOR MOSFET : AMELIORATION DE LA TENUE EN TENSION

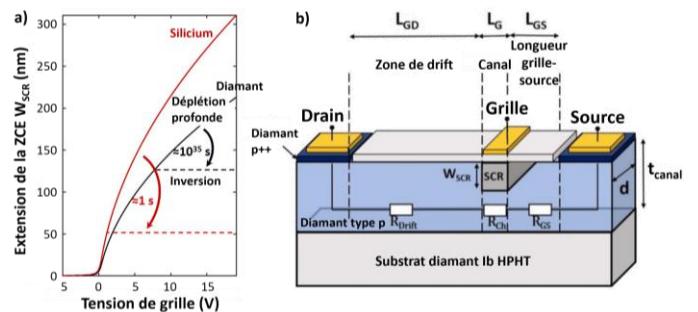

La technologie MOSFET est également étudiée depuis de nombreuses années notamment en améliorant l'interface Oxyde-Diamant dopé type p et à terminaison de surface oxygène [10]. Les travaux précédents ont introduit et validé l'utilisation du régime de déplétion profonde, présenté par la Figure 5, pour la capacité Métal – Oxyde – Diamant [11-12].

Figure 5 : Transistor en diamant à déplétion profonde. a) Comparaison à température ambiante de l'extension de la zone de charge d'espace pour le silicium et le diamant en fonction de la tension appliquée sur la grille prenant en compte le phénomène d'inversion ou non. 50 nm d' $\text{Al}_2\text{O}_3$  sont utilisés pour l'oxyde de grille et le dopage du semi-conducteur est de  $2.10^{17} \text{ at/cm}^3$

b) Schéma vue en coupe du transistor D3MOSFET.

Grâce à l'énergie de gap élevée du diamant, ce régime de polarisation est stable dans le temps et il est alors possible de dépléter une grande épaisseur de canal, sans avoir de phénomène d'inversion à l'échelle de temps humaine, via une grille isolée (Figure 5 a)). En découle la possibilité de maintenir un état bloqué pour un transistor MOSFET « sans jonction » sur un temps très long (plusieurs jours vérifiés expérimentalement à plusieurs années, selon la température). Ce phénomène est essentiel dans le fonctionnement d'un composant unipolaire en diamant tel que celui décrit par la Figure 5 b) car il permet d'augmenter l'épaisseur ou le dopage du canal de conduction, et ainsi le calibre en courant, tout en gardant la possibilité d'avoir un état bloqué stable. Des transistors D3MOSFET (Deep Depletion Diamond MOSFET) ont été conçus et fabriqués [12], ils montrent des résultats très encourageants. L'état passant du composant est présenté par la Figure 6.

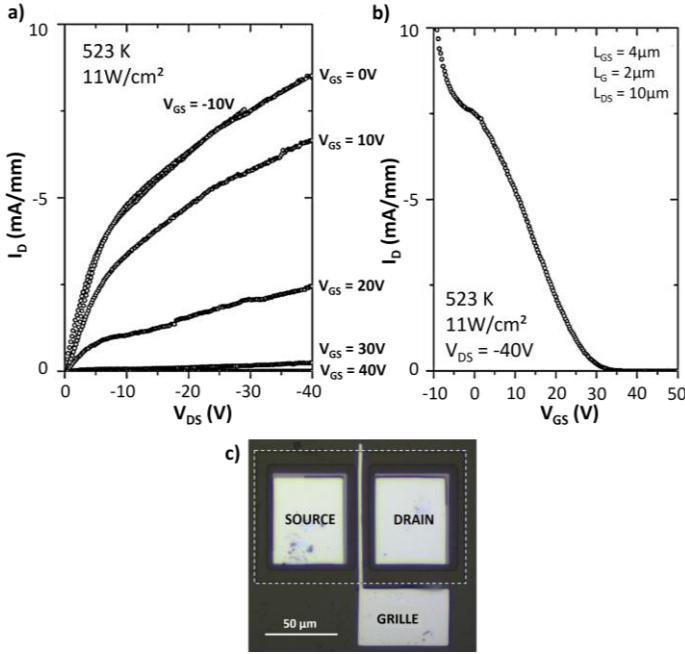

Figure 6 : Rappel de l'état de l'art D3MOSFET. a) Caractéristique IV d'un transistor D3MOSFET mesuré sous éclairage ( $11\text{mW/cm}^2$ ) et à 523K.  $I_b$  en fonction de  $V_{DS}$  et b)  $V_{GS}$ . c) Image MEB de transistors latéraux D3MOSFET en diamant.

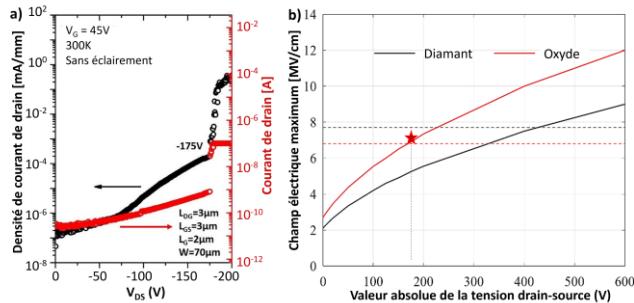

Il a montré une tension de seuil  $V_{TH}$  autour de 35V (Figure 6 b)) et un courant de drain à 15V de 5 mA/mm (Figure 6 a)). Cela correspond à une résistance spécifique  $R_{on,S}$  de  $50\text{ m}\Omega.\text{cm}^2$  à 523K. Cette valeur bien qu'attrayante peut encore être améliorée en optimisant le dimensionnement et les différents paramètres architecturaux du transistor. Le composant a aussi montré un champ électrique à l'état bloqué entre 5.4 et 6.8MV/cm [12] soit déjà au-delà du SiC et GaN. Néanmoins, du fait de l'architecture latérale du transistor, le pic de champ le plus important se trouve dans l'oxyde de grille ce qui induit un claquage prématûre de ce dernier. Ainsi la tenue en tension obtenue est de 175V (Figure 7) alors que le dimensionnement 1D de cette zone devrait permettre une tenue de 1kV.

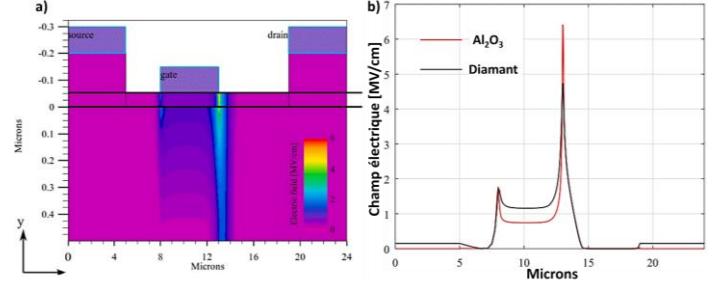

La simulation élément finis (TCAD) obtenu avec le logiciel Silvaco en 2D représentée sur la Figure 8 montre en effet que pour une tension  $V_{DS}$  de -200V le champ électrique dans l'oxyde est supérieur au champ critique de ce dernier (entre 5,7 et 6,3 MV/cm expérimentalement [12]).

Figure 8 : a) Simulation éléments finis du transistor D3MOSFET estimant le champ électrique à  $V_{DS}= -200\text{V}$  et  $V_{GS}= +40\text{V}$ . b) Evolution du champ électriques à l'état bloqué aux interfaces métal/ $\text{Al}_2\text{O}_3$  et  $\text{Al}_2\text{O}_3/\text{diamant}$ .

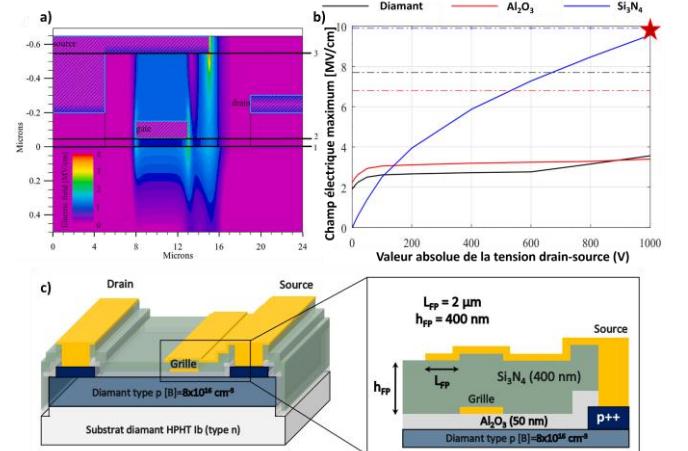

Afin d'augmenter la tenue en tension tout en conservant l'architecture simple de transistor D3MOSFET latéral et sans détériorer la valeur de courant, des simulations éléments finis 2D ont été conduites afin d'optimiser différentes géométries d'électrodes de champ [13]. De façon classique, les électrodes de champ permettent d'étaler le champ électrique et donc d'augmenter la tenue en tension des composants. Par son bon compromis efficacité – simplicité technologique, une électrode de champ unique de type « Source Field Plate » a été optimisée, couplée à un diélectrique de type  $\text{Si}_3\text{N}_4$  (Figure 9). Les simulations ont montré le bon fonctionnement de l'électrode de champ, en réduisant le champ électrique dans le diamant et dans l'oxyde de grille ( $\text{Al}_2\text{O}_3$ ) et en reportant la contrainte de champ sur le nitre ( $\text{Si}_3\text{N}_4$ ) utilisé entre l'électrode de champ et la grille. La maîtrise de l'alignement entre le bord de l'électrode de champ et la grille est essentielle, la côte retenue est de  $2\mu\text{m}$ , pour être compatible avec les contraintes technologiques et pour une épaisseur de  $\text{Si}_3\text{N}_4$  comprise entre 400 et 600nm, compatibles avec les techniques de dépôts par pulvérisation.

Figure 9 : Optimisation de l'électrode de champ « Source ». a) Simulation éléments finis estimant le champ électrique à  $V_{DS}= -1000\text{V}$  et  $V_{GS}= +40\text{V}$ . b) Evolution des pics de champ électriques à l'état bloqué en fonction de la tension  $|V_{DS}|$ , dans le diamant, les isolants de grille et de field plate. Les lignes en pointillées représentent le champ critique de chaque matériau et l'étoile, où se produit le claquage. c) Vue en coupe d'un transistor D3MOSFET avec électrode de champ.

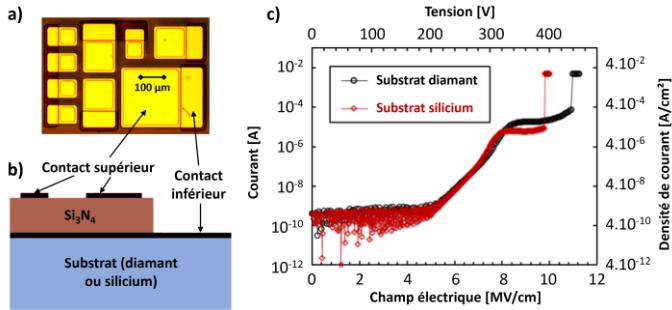

Cette nouvelle brique technologique a été développée, regroupant les étapes de dépôts, lithographies et gravures. Dans un premier temps, des capacités MIM (Métal Isolant Métal) sur substrats Si et diamant ont été réalisées. La Figure 10 présente ces résultats encourageants, avec l'obtention d'un champ de claquage du  $\text{Si}_3\text{N}_4$  autour de 10 MV/cm, ouvrant la porte à une tenue en tension du transistor D3MOSFET latéral entre 800 et 1000V au lieu de 175V, sans modification de son  $R_{on,S}$ .

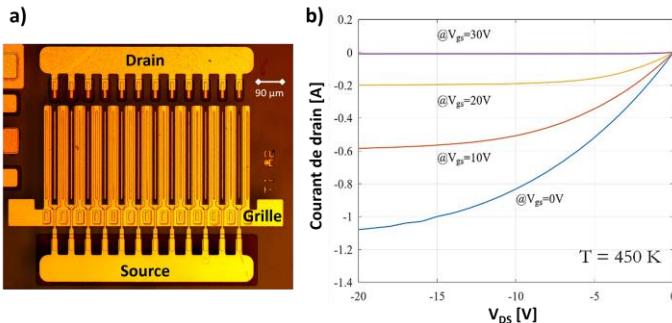

Dans l'optique d'augmenter le calibre en courant du transistor, des simulations éléments finis ont été réalisées pour optimiser son design. D'après les résultats obtenus, le composant final devrait délivrer une densité de courant de  $3,5 \text{ mA/mm}$  à  $V_{DS}=2\text{V}$ ,  $V_{GS}=0\text{V}$  et pour une température de  $450\text{K}$ . Les paramètres architecturaux sont  $L_{GS}=3\mu\text{m}$ ,  $L_G=5\mu\text{m}$ ,  $L_{GD}=6\mu\text{m}$ , le dopage  $N_A=8.10^{16} \text{ atomes.cm}^{-3}$  et  $t_{canal}=500 \text{ nm}$ . Pour obtenir un calibre en courant correspondant au besoin de l'électronique de puissance, le composant doit être fabriqué dans une version interdigité tel que cela est fait dans l'industrie sur les matériaux traditionnels. Des tests ont été réalisés pour montrer que le process technologique permettant de fabriquer des transistors D3MOSFET interdigités avec électrode de champ, tel que représenté par la Figure 9 b), est viable. La Figure 11 a) montre une image en microscopie optique d'un prototype de ce composant.

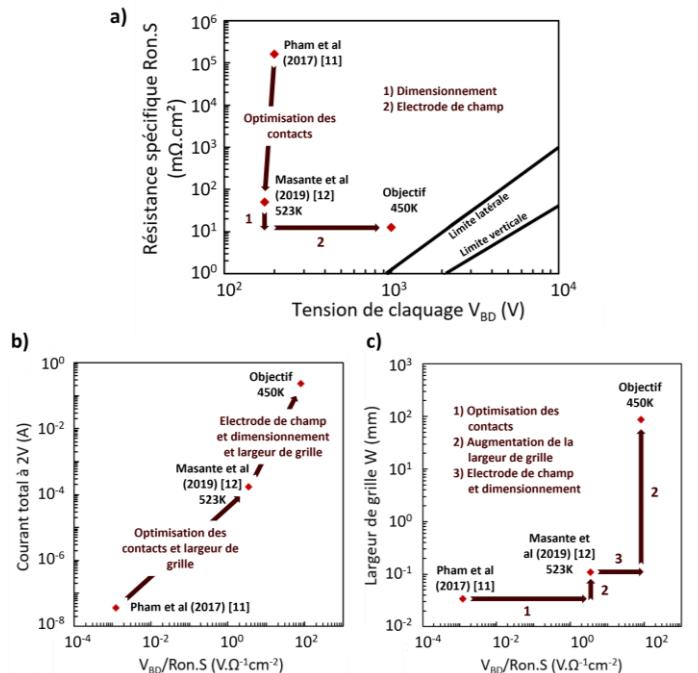

Ce transistor de grande taille n'est pas encore fonctionnel car il ne comporte pas de couche active en diamant mais il montre tout de même la faisabilité du composant d'un point de vue technologique. D'après les simulations, le transistor final pourra délivrer un courant de  $0,3\text{A}$  à  $V_{DS}=2\text{V}$  et de  $1\text{A}$  à  $V_{DS}=15\text{V}$  (Figure 11 b)) pour  $V_{GS}=0\text{V}$  et une largeur de grille équivalente de  $86,4 \text{ mm}$ . Les différentes briques en cours de développement promettent de rendre le transistor D3MOSFET plus performant dans un futur proche. La Figure 12 permet de se rendre compte de l'évolution du D3MOSFET depuis 2017 à nos jours en termes de résistance spécifique et de tension de claquage.

Au cours des dernières années, les contacts et le dimensionnement et donc la résistance spécifique  $Ron.S$  du composant ont été optimisés. De plus, la largeur équivalente de grille du composant a été augmentée pour obtenir un calibre en courant plus important. En ajoutant à cela une électrode de champ, le transistor D3MOSFET devrait pouvoir développer un courant total de  $1\text{A}$  à  $V_{DS}=15\text{V}$  et  $V_{GS}=0\text{V}$  ainsi qu'une tension de claquage entre  $800$  et  $1000\text{V}$ . L'augmentation du critère  $V_{BD}/Ron.S$  couplé à l'augmentation de la largeur de grille du transistor D3MOSFET illustre bien l'impact des améliorations prévues. D'après les simulations et les premiers résultats encourageants, ces caractéristiques en feraient un composant utilisable pour l'électronique de puissance.

## 5. CONCLUSION

Des avancées majeures ont été présentées pour les transistors à effet de champ en diamant, à grille jonction et MOS. Le pilotage optique des transistors de type JFET en diamant est reproductible et réalisable pour deux donneurs profonds différents, l'azote et le phosphore. Pour le MOSFET à déplétion profonde, des simulations éléments finis 2D ont été réalisées et de nouvelles briques technologiques ont été développées. En optimisant le dimensionnement, les contacts et la largeur de grille développée par le composant, il devrait délivrer un courant de  $0,3\text{A}$  à  $V_{DS}=2\text{V}$  et de  $1\text{A}$  à  $V_{DS}=15\text{V}$  pour  $V_{GS}=0\text{V}$ . De plus, l'ajout d'une électrode de champ de type « source field plate » permettrait d'obtenir une tension de claquage entre  $800$  et  $1000\text{V}$  d'après les simulations, appuyées par des premiers résultats expérimentaux encourageants. Les performances à haute température, au-delà de  $423\text{K}$ , de ces composants permettraient une réelle alternative et une première démonstration des bénéfices du diamant pour l'électronique de puissance.

## 6. REMERCIEMENTS

Les travaux sont financés en partie par ANR LSD-MOSFET (JFET), Cleansky2 DCade (MOSFET). Nous remercions ASU (Prof. R. Nemanich), Nanofab (Institut Néel, salle blanche et caractérisation électrique) et AIME Toulouse (Insa Toulouse, plateforme de conception et simulation).

## 7. REFERENCES

- [1] J. Millán, P. Godignon, X. Perpiñà, A. Pérez-Tomás and J. Rebollo, "A Survey of Wide Bandgap Power Semiconductor Devices," in IEEE Transactions on Power Electronics, vol. 29, no. 5, pp. 2155–2163, May 2014, doi: 10.1109/TPEL.2013.2268900.

- [2] N. Donato, N. Rouger, J. Pernot, G. Longobardi, F. Udrea. Diamond power devices: State of the art, modelling and figures of merit. Journal of Physics D: Applied Physics, 2019, 53 (9), pp.093001. ([hal-02377372](#))

- [3] N.C. Saha, S.-W. Kim, T. Oishi, M. Kasu, 875-mw/cm<sup>2</sup> low-resistance no p-type doped chemical mechanical planarized diamond mosfets, IEEE Electron Device Lett. 43 (5) (2022) 777 – 780, <https://doi.org/10.1109/LED.2022.3164603>.

- [4] H. Kawarada, T. Yamada, D. Xu, Y. Kitabayashi, M. Shibata, D. Matsumura, M. Kobayashi, T. Saito, T. Kudo, M. Inaba, A. Hiraiwa, Diamond mosfets using 2d hole gas with 1700v breakdown voltage, in: 2016 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2016, pp. 483 – 486, <https://doi.org/10.1109/ISPSD.2016.7520883>.

- [5] E. Gheeraert, S. Koizumi, T. Teraji, and H. Kanda, 'Electronic transitions of electrons bound to phosphorus donors in diamond', *Solid State Communications*, vol. 113, no. 10, pp. 577–580, Feb. 2000, doi: [10.1016/S0038-1098\(99\)00546-3](https://doi.org/10.1016/S0038-1098(99)00546-3).

- [6] B. B. Li, M. C. Tosin, A. C. Peterlevitz, and V. Baranauskas, 'Measurement of the substitutional nitrogen activation energy in diamond films', *Appl. Phys. Lett.*, vol. 73, no. 6, pp. 812–814, Aug. 1998, doi: 10.1063/1.122010.

- [7] Y. Koide *et al.*, 'Admittance spectroscopy for phosphorus-doped n-type diamond epilayer', *Appl. Phys. Lett.*, vol. 86, no. 23, p. 232105, Jun. 2005, doi: [10.1063/1.1944896](https://doi.org/10.1063/1.1944896).

- [8] T. Iwasaki *et al.*, 'High-Temperature Bipolar-Mode Operation of Normally-Off Diamond JFET', *IEEE J. Electron Devices Soc.*, vol. 5, no. 1, pp. 95–99, Jan. 2017, doi: [10.1109/JEDS.2016.2624301](https://doi.org/10.1109/JEDS.2016.2624301).

- [9] C. Masante, M. Kah, C. Hébert, N. Rouger, J. Pernot. Non-Volatile Photo-Switch Using a Diamond pn Junction. Advanced Electronic Materials, 2021, 8, pp.2100542 ([hal-03367390](#))

- [10] A. Maréchal, M. Aoukar, C. Vallée, C. Rivière, D. Eon, J. Pernot, and E. Gheeraert, Energy-band diagram configuration of Al<sub>2</sub>O<sub>3</sub>/oxygen-terminated p-diamond metal-oxide-semiconductor, *Applied Physics Letters*. 107. 10.1063/1.4931123.

- [11] T. -T. Pham, J. Pernot, G. Perez, D. Eon, E. Gheeraert and N. Rouger, "Deep-Depletion Mode Boron-Doped Monocrystalline Diamond Metal Oxide Semiconductor Field Effect Transistor," in IEEE Electron Device Letters, vol. 38, no. 11, pp. 1571-1574, Nov. 2017, doi: 10.1109/LED.2017.2755718

- [12] C. Masante, N. Rouger, J. Pernot. Recent progress in deep-depletion diamond metal-oxide-semiconductor field-effect transistors. *Journal of Physics D: Applied Physics*, 2021, 54 (23), pp.233002. ([hal-03287047](#))

- [13] M. Courret, D. Michez, J. Letellier, A. Castelan, J. Pernot, N. Rouger, Field-plated D3MOSFET design for breakdown voltage improvement, *Diamond and Related Materials*, Volume 135, 2023, 109827, ISSN 0925-9635