# Etude expérimentale de la mise en parallèle de plusieurs diodes

Frédéric REYMOND-LARUINA<sup>1,2,3</sup>, Tanguy PHULPIN<sup>1,2</sup>, Yasmine BAAZIZI<sup>1,2</sup>, Richard BELJIO<sup>1,2</sup>, Loïc QUEVAL<sup>1,2</sup>, Djamel HADBI<sup>3</sup>, Philippe EGROT<sup>3</sup>, Marc PETIT<sup>1,2</sup>

<sup>1</sup> Université Paris-Saclay, CentraleSupélec, CNRS, Laboratoire de Génie Electrique et Electrotechnique de Paris, 91190 Gif-sur-Yvette, France.

<sup>2</sup> Sorbonne Université, CNRS, Laboratoire de Génie Electrique et Electrotechnique de Paris, 75252 Paris, France

<sup>3</sup> EDF R&D – Electrical Equipment Laboratory, EDF Lab Les Renardières, 77250 Moret-sur-Loing, France

**RESUME** – Un convertisseur AC/DC, raccordé au réseau électrique de distribution, est principalement soumis à des flux de puissance unidirectionnels qui peuvent dépasser les capacités thermiques des semiconducteurs et les endommager. Pour dépasser ce problème, nous nous intéressons à l'étude des pertes dans des diodes PiN en parallèle ou non avec une diode de commutation. Dans cet article, nous mesurons les pertes mesurées à l'aide d'un test à double impulsion (ou double pulse) et nous nous intéressons à la prédictibilité du résultat par rapport aux données du fabricant. Il apparaît que la parallélisation de diodes identiques entraîne une augmentation des pertes totales par recouvrement. Seule l'association avec des diodes ayant de meilleures performances en commutation entraîne une diminution des pertes totales. Cependant, cela conduit à une augmentation des pics de tension et à une distorsion des formes d'onde dans chaque composant, ce qui peut être préjudiciable à l'estimation des performances et la fiabilité d'un futur circuit avec plusieurs composants en parallèle.

**Mots-clés** — « Double Pulse », « Pertes », « Diode », « Parallélisation », « LVDC »

## 1. INTRODUCTION

Les réseaux électriques à courant continu suscitent un vif intérêt en raison du déploiement toujours plus massif de sources d'énergies distribuées et de nouveaux usages intégrant un bus en courant continu [1]–[4]. Mais la faible tenue thermique des convertisseurs d'électronique de puissance aux surcharges est souvent mentionnée comme un obstacle au déploiement d'un réseau de distribution à courant continu. Une réponse à ce problème consiste à paralléliser les composants semi-conducteurs. Cela ouvre la possibilité d'une part, d'utiliser des composants plus petits et donc moins coûteux, et d'autre part de réduire la taille des composants passifs et du refroidissement. Il en résulte que la parallélisation amène une plus grande fiabilité et une meilleure modularité.

Les études précédentes se concentrent principalement sur la caractérisation de modules de puissance parallélisés pour des applications de traction [5]–[7]. L'article [8] étudie l'influence des paramètres des modules sur les pertes. Une corrélation explicitant l'influence de la tension de saturation  $V_{ce}$  et de la tension de seuil  $V_{ge}$  d'un IGBT, ainsi que de la tension directe  $V_{ec}$  de la diode en antiparallèle, sur les pertes par commutation est proposée. La note technique [9] se focalise sur la modélisation de la répartition des courants en régime

permanents, lors de la mise en parallèle de deux diodes rapides identiques. Des mesures effectuées en commutation dans ce document tendent à montrer une augmentation des pertes par recouvrement totales lors de la mise en parallèle en diodes.

Peu d'informations sont donc disponibles quant à l'effet de la parallélisation de diodes. Ce manque de données nous conduit à nous interroger sur les performances d'une telle association et sur sa pertinence, en particulier dans le cas d'une association de diodes différentes, tel que des diodes de redressement basse fréquence et des diodes rapides de commutation. Les premières sont rarement caractérisées en commutation, malgré d'excellentes propriétés en conduction. Tandis que les secondes ont généralement de mauvaises caractéristiques en conduction, mais de très bonnes performances en commutation.

Nous proposons donc d'étudier ici la mise en parallèle de diodes de puissance à l'aide d'un banc de mesure double pulse. D'abord pour des diodes de redressement basse fréquence et ensuite avec une diode rapide. Dans un premier temps, la mesure double pulse, permettant d'étudier le comportement des diodes en régime permanent et en commutation est décrite. Ensuite les résultats de la caractérisation de diodes identiques ou différentes connectées en parallèle, sont présentés.

## 2. MESURE DOUBLE PULSE

### 2.1. Pertes par recouvrement et par commutation

Pour qu'une diode passe d'un état conducteur à un état bloqué, la répartition des charges dans la jonction semiconductrice doit changer. Cela ne peut se produire qu'avec un mouvement de charge, c'est-à-dire un courant qui transite momentanément en sens inverse. Lors d'une commutation forcée, où la tension s'inverse brutalement, l'apparition de ce courant engendre des pertes au blocage, dites « pertes par recouvrement ». Le recouvrement se produit également à la mise en conduction d'une diode, mais la rapidité de mise en conduction des porteurs minoritaires permet de négliger le phénomène.

Les pertes par recouvrement augmentent avec la température et le courant, du fait de l'augmentation des charges stockées à recombiner [10], [11]. Pour des fréquences de commutation supérieures à 10 kHz, ce phénomène devient significatif dans la contribution aux pertes d'une cellule de commutation et doit être considéré.

Notons que les pertes par recouvrement se distinguent des pertes par commutation des IGBTs ou MOSFET par le phénomène qui les génèrent. Dans ces semiconducteurs, les pertes sont dû à la charge et à la décharge des capacités parasites. Par abus de langage, les pertes par recouvrement sont souvent regroupées sous l'appellation de « pertes par commutation » que nous n'utiliserons pas ici.

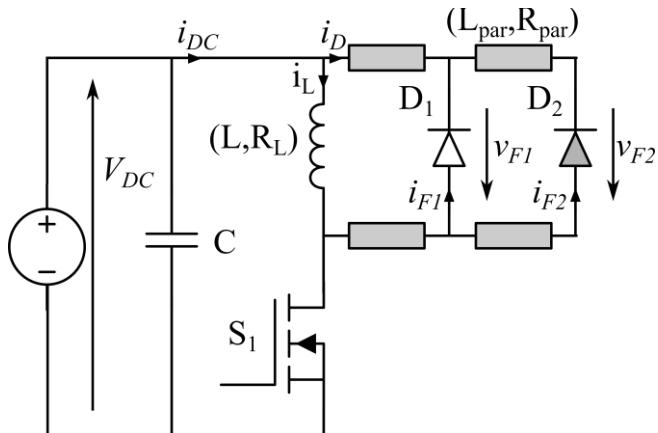

## 2.2. Principe de la mesure

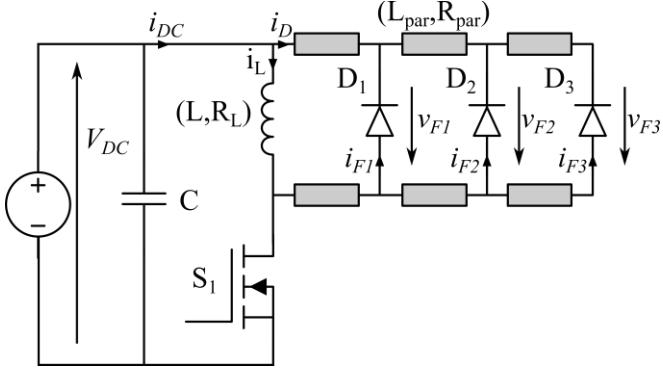

La Figure 1 représente la mesure double pulse mise en place pour la détermination des pertes par commutation et par conduction présentes dans l'étude d'un composant semi-conducteur. Pour  $t \in [0, T_1]$ , l'interrupteur  $S_1$  est fermé : le courant de l'inductance  $L$  augmente jusqu'à ce que  $i_{DC}$  atteigne la valeur choisie de test  $I_{test}$ . Pour  $t \in [T_1, T_1 + T_2]$ , l'interrupteur  $S_1$  est ouvert : le courant circule dans l'inductance et les diodes. La durée de cette phase est limitée par la diminution choisie du courant  $\Delta I_{test}$  permettant une estimation fiable des pertes par conduction. Pour  $t \in [T_1 + T_2, T_1 + T_2 + T_3]$ , l'interrupteur  $S_1$  est fermé : cela permet de mesurer le recouvrement des diodes. La durée de cette pulsation est choisie de manière à limiter le courant à un niveau acceptable pour les composants, mais également permettre le recouvrement des diodes. Pour la suite, la durée de cette dernière pulsation est fixée à  $10 \mu\text{s}$ .  $T_1$  et  $T_2$  sont définis par,

$$T_1 = \frac{L}{R_L} \ln \left( \frac{V_{DC}}{V_{DC} - R_L I_{test}} \right) \quad (1)$$

$$T_2 = -\frac{L}{R_{eq}} \ln \left( 1 + \frac{\Delta I_{test}}{I_{test} + \frac{v_F}{R_{eq}}} \right) \quad (2)$$

Avec  $R_{eq} = R_L + R_D$  la résistance de la maille de décharge de l'inductance [ $\Omega$ ],  $R_D$  la résistance équivalente à l'état passant des diodes en parallèles [ $\Omega$ ],  $v_F$  la tension de seuil des diodes [V] et  $\Delta I_{test}$  la diminution choisie de courant durant la durée  $T_2$  [pu].

Les tensions  $V_{DC}$  étudiées sont  $\{100, 200, 300, 400\} \text{ V}$ , tandis que les courants  $I_{test}$  sont  $\{5, 10, 15, 20, 25, 30\} \text{ A}$ . Nous considérons une, deux ou trois diodes en parallèles. La Figure 1 représente ce dernier cas. La configuration employée pour l'étude est dite « high side ».

Figure 1 : Schéma de principe de la mesure double pulse.  $L_{par}$  et  $R_{par}$  représentent les impédances parasites.

L'énergie dissipée dans une diode par recouvrement  $E_{rr}$  est :

$$E_{rr} = \int_{t_1}^{t_2} v_F(t) i_F(t) dt \quad (3)$$

Avec  $v_F(t)$  est la tension de la diode et  $i_F(t)$  le courant de la

diode, selon les conventions de la Figure 1.

En se référant à la littérature [8], [12],  $t_1$  correspond au moment où la tension aux bornes de la diode atteint 10 % de la tension du bus continu  $V_{DC}$ .  $t_2$  correspond au moment où le courant dans la diode atteint 25% du courant de pic inverse  $I_{rr}$ .

## 2.3. Dispositif d'essai

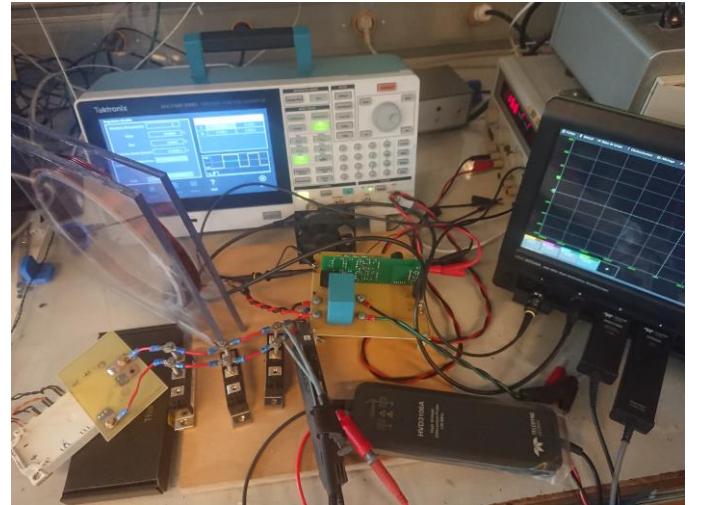

La plateforme expérimentale (Figure 2) se compose d'une source de tension continu SM1500-CP-30, d'un générateur de signaux AFG31000, d'une source de tension 15 V, d'un oscilloscope Teledyne Lecroy HDO6034A, de sondes de courant CP030A et de tension HVD3106A. Le driver 2SC0108T2F1 est utilisé pour la commande de l'IGBT STW69N65M5, nommé  $S_1$ . La bobine à air a une résistance  $R_L = 180 \text{ m}\Omega$  et une inductance  $L = 313 \mu\text{H}$  à 1 kHz. Le condensateur de découplage est en céramique et a une capacité  $C = 30 \mu\text{F}$  [12]. Les conducteurs permettant la connexion des composants en parallèle, en gris sur la Figure 1, ont une inductance  $L_{par} = 38 \text{ nH}$  et une résistance  $R_{par} = 0,8 \text{ m}\Omega$ .

Figure 2 : Plateforme expérimentale pour la mesure double pulse.

## 2.4. Composants testés

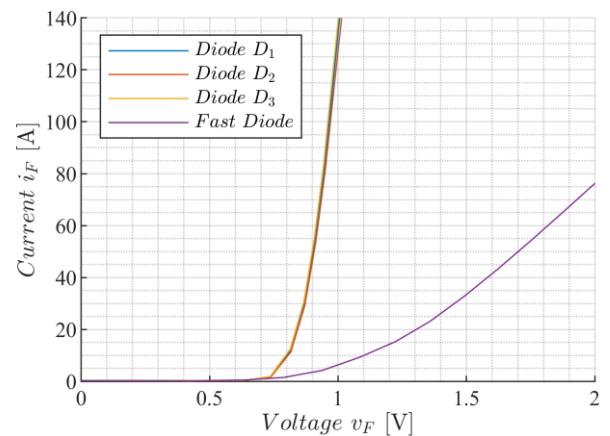

Figure 3 : Caractéristiques en conduction des diodes de redressement  $D_1$ ,  $D_2$  et  $D_3$ , ainsi que de la diode rapide « Fast Diode ».

Les diodes de redressement basse fréquence considérées ont la référence DD89N12K. Les diodes rapides de commutation sont celles situées en antiparallèle des IGBTs dans le module FS75R12KT3. Leur caractéristique I-V statique a été mesurée à l'aide de la plateforme de test Gargantua [13], avant d'être

caractérisé pour la commutation. Les résultats sont disponibles à la Figure 3. La tension de seuil des diodes de redressements et de la diode rapide sont de 0,84 V et 1,12 V, respectivement. La résistance à l'état passant est de 1,2 mΩ et 11,4 mΩ, respectivement.

### 3. RESULTATS

#### 3.1. Caractérisation des composants seuls

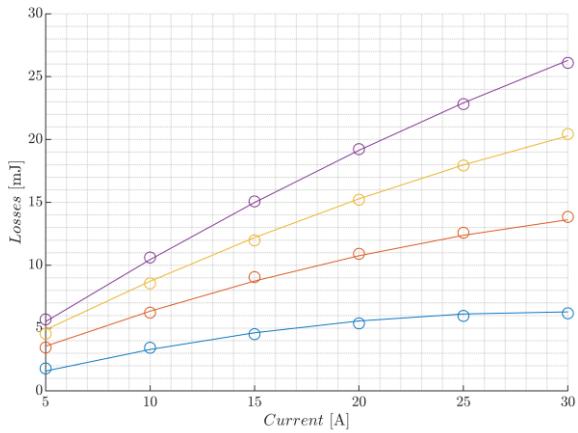

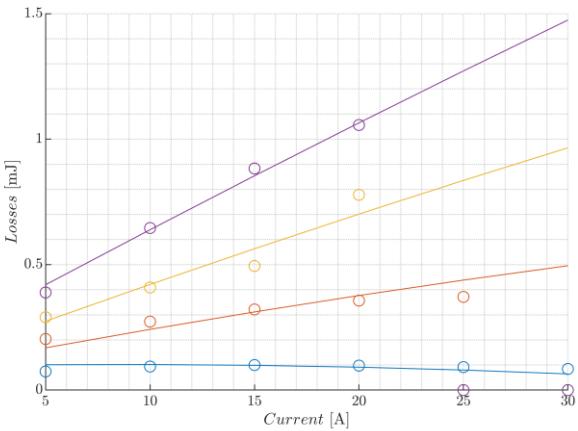

Nous avons d'abord caractérisé les pertes par recouvrement de chaque diode. La Figure 4 et la Figure 5 illustrent l'évolution des pertes pour les deux types de diodes, en fonction des courants et des tensions. Notons que certaines valeurs de courant n'ont pas pu être atteinte, en raison des capacités du driver utilisé.

Ces pertes, exprimées en [J], peuvent être approximée par un modèle polynomial,

$$E_{rr} = a \cdot I_{DC}^2 + b \cdot I_{DC} + c \cdot V_{DC}^2 + d \cdot V_{DC} \cdot I_{DC} + f \quad (4)$$

avec les coefficients a, b, c, d, et f résumés dans le Tableau 1. Les pertes dans la diode de redressement sont significatives en l'absence de circuits d'aides à la commutation, plus communément appelé « snubbers ». Ce phénomène était attendu et est conforme à la théorie pour ces diodes qui se caractérisent par un recouvrement abrupt.

Figure 4 : Evolution des pertes pour la diode DD89N12K sous 100 V (bleu), 200 V (rouge), 300 V (jaune) et 400 V (violet). En continu, le modèle fournit par l'équation (4) et le Tableau 1.

Figure 5 : Evolution des pertes pour la diode du module FS75R12KT3 sous 100 V (bleu), 200 V (rouge), 300 V (jaune) et 400 V (violet). En continu, le modèle fournit par l'équation (4) et le Tableau 1.

Tableau 1 : Coefficients de l'équation (4).

|          | <b>DD89N12K</b>         | <b>FS75R12KT3</b>       |

|----------|-------------------------|-------------------------|

| <b>a</b> | $-7,737 \times 10^{-6}$ | $-8,16 \times 10^{-8}$  |

| <b>b</b> | $2,447 \times 10^{-4}$  | $-1,316 \times 10^{-5}$ |

| <b>c</b> | $-3,312 \times 10^{-8}$ | $1,949 \times 10^{-9}$  |

| <b>d</b> | $1,895 \times 10^{-6}$  | $-6,389 \times 10^{-7}$ |

| <b>e</b> | $2,143 \times 10^{-6}$  | $1,455 \times 10^{-7}$  |

| <b>f</b> | $2,08 \times 10^{-3}$   | $1,405 \times 10^{-4}$  |

#### 3.2. Parallélisation de diodes de redressement identiques

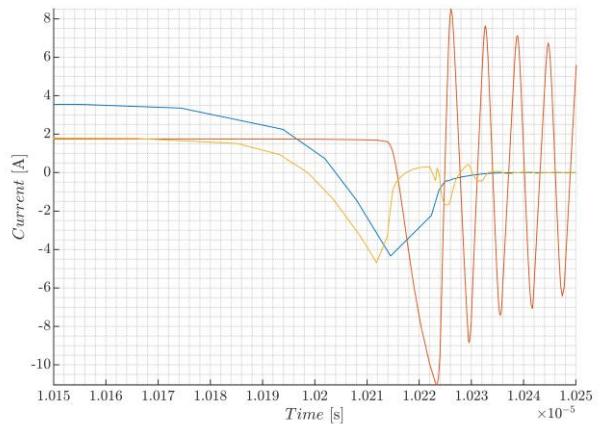

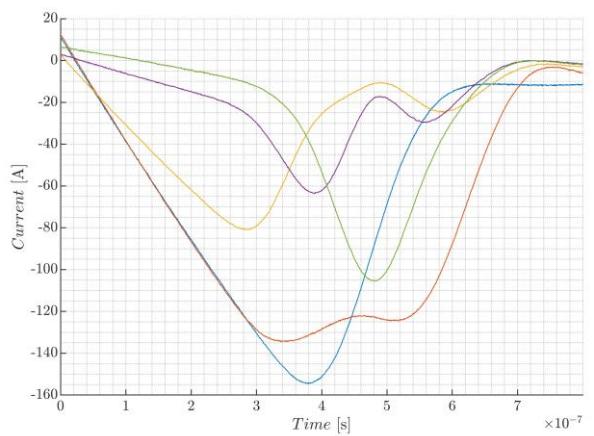

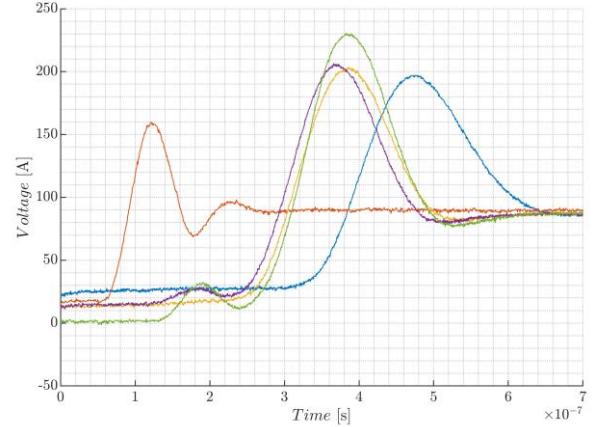

Nous nous intéressons ici à la mise en parallèle de diodes de redressement identiques. Une pré-simulation en utilisant les modèles de composant disponible sous PLECS tend à suggérer une diminution des pertes totales avec la parallélisation. En effet, le calcul des pertes est basé sur une extrapolation de la documentation constructeur [14]. Pour chaque composant, les pertes dépendent du courant et de la tension appliquée. En parallélisant, chaque composant est traversé par un courant plus faible sous une même tension, ce qui induit une diminution des pertes. Une modélisation sous LTSpice de notre structure, composée de deux diodes identiques en parallèle, tend à montrer que lors de la parallélisation, le courant dans les diodes devrait se répartir équitablement en régime permanent, aux impédances de connexion près. Cependant, le passage à l'état bloqué induit un comportement asymétrique. Une des diodes se bloque plus rapidement, tandis que l'autre présente une oscillation de courant. La Figure 6 illustre ce résultat. Notons que sur cet exemple, les diodes employées ne correspondent pas aux diodes présentées plus haut car leurs modèles n'existent pas sous LTSpice. Le résultat présenté ici n'est donné qu'à titre indicatif sur le comportement possible des diodes.

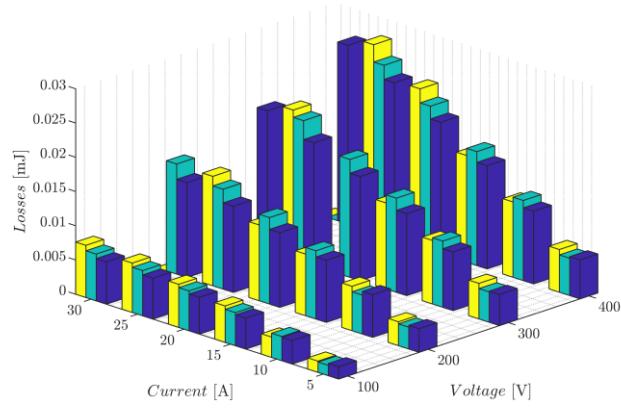

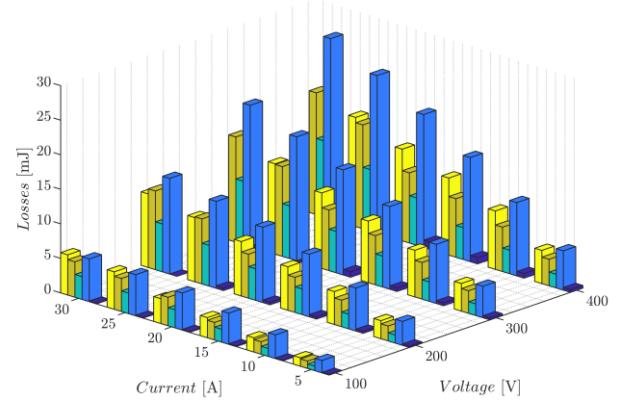

De manière générale, nos résultats de mesures tendent à montrer que les comportements constatés en simulation divergent de ceux constatés. Tout d'abord du point de vue des pertes, la Figure 7 illustre les pertes totales dans les composants en fonction du nombre de diodes mise en parallèle. Les mesures à 30 A sous 300 et 400 V n'ont pu être effectuée pour plusieurs diodes en parallèle, du fait de notre montage.

Figure 6 : Evolution des courants pour deux diodes D<sub>1</sub> (jaune) et D<sub>2</sub> (orange) en parallèle lors d'une mesure double pulse d'après LTSpice. Comparaison avec le résultat de simulation pour une seule diode (bleu)

Que ce soit avec 2 ou 3 diodes en parallèles, il est effectivement possible d'assister à une diminution des pertes pour des courants inférieurs à 10 A. La diminution maximale des pertes est par exemple de 15% sous 100 V et 5 A, pour 2 diodes en parallèles par rapport à aux pertes dans une seule diode dans

les mêmes conditions. Avec l'augmentation du courant et de la tension, ce phénomène s'atténue : les pertes totales augmentent jusqu'à égaler puis dépasser celle dans une diode seule. Cela en dépit du fait que le courant passant par chaque diode au moment de la commutation est divisé par le nombre de diodes mise en parallèle. L'augmentation maximale enregistrée pour les pertes est de 26%. Elle se produit lors de la mise en parallèle de 3 diodes sous 400 V et 25 A. Cette tendance à l'augmentation des pertes par recouvrement lors de la parallélisation corrobore les résultats de [9], mais infirme les tendances fournies avec PLECS.

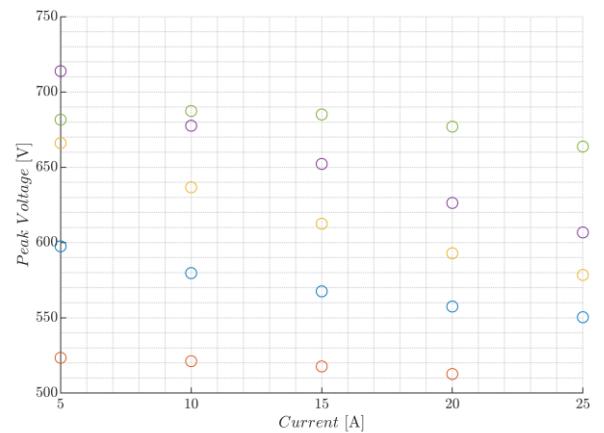

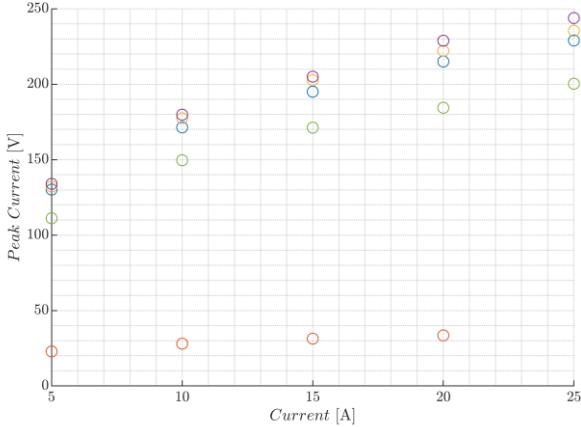

Comme illustré par la Figure 8, il est possible de constater que la tension aux bornes de chaque diode n'est pas identique. Plus une diode est éloignée de l'inductance, plus un pic de tension important sera observé durant sa commutation. Cela peut s'expliquer par une inductance de câblage supérieure. La Figure 9 montre bien cette évolution : dans le cas critique d'une tension de 400 V, quel que soit l'association, le pic de tension en entrée du montage est équivalent ou supérieur à celui d'une diode seule. Du point de vue des courants, les pics de recouvrement inverses dans chaque diode sont plus faibles que pour une diode seule, comme illustré dans la Figure 10. En revanche, le pic de courant total est proche, 13% près, de celui pour une diode seule d'après la Figure 10. La Figure 11 montre que sous certaines conditions de tensions et courant, ce pic devient plus important que pour une diode seule. La pré-simulation effectuée sous LTSpice a en partie permis de mettre en évidence ces phénomènes, à savoir l'amorçage plus rapide d'une des diodes en parallèle et la différence entre les pics de courant.

De manière générale, il est intéressant de noter que la parallélisation induit une déformation des tensions et courant dans chaque diode qui ne correspondent plus à la représentation classique des phénomènes de recouvrement inverse [12], ni aux informations fournies par le constructeur. Pour pallier ce problème et permettre une estimation des performances d'un assemblage de composant, nous proposons de modéliser les pertes par recouvrement par l'équation (4) : les pertes d'un assemblage de diodes identiques en parallèle se modélisent sur le même format que les pertes dans une diode. Les coefficients, selon la configuration choisie, sont fournis dans le Tableau 2. Cette méthode est particulièrement intéressante pour l'emploi d'un logiciel tel que PLECS.

Figure 7 : Evolution des pertes totales en fonction du courant et de la tension pour 1 diode de redressement seule (bleu), 2 diodes en parallèle (vert) et 3 diodes en parallèle (jaune)

Figure 8 : Tensions mesurées aux bornes des diodes durant le recouvrement sous 100 V – 20 A pour le cas de la Figure 1 pour la diode seule (bleu), la diode 1 (jaune), la diode 2 (violet) et la diode 3 (vert). En orange, la tension aux bornes de l'inductance.

Figure 9 : Evolution du pic de tension aux bornes de l'inductance, en fonction du courant de test et du montage, sous 400 V : diode de redressement seule (bleu), diode rapide seule (rouge), 2 diodes de redressement en parallèle (jaune), 3 diodes de redressement en parallèle (violet) et 3 diodes de redressement en parallèle avec 1 diode rapide (vert)

Figure 10 : Courants mesurés dans les diodes durant le recouvrement sous 100 V – 20 A pour le cas de la Figure 1 pour la diode seule (bleu), la diode 1 (jaune), la diode 2 (violet) et la diode 3 (vert). En orange, le courant total dans le montage  $i_D$ .

Figure 11 : Evolution du pic de courant  $i_D$ , en fonction du courant de test et du montage, sous 400 V : diode de redressement seule (bleu), diode rapide seule (rouge), 2 diodes de redressement en parallèle (jaune), 3 diodes de redressement en parallèle (violet) et 3 diodes de redressement en parallèle avec 1 diode rapide (vert)

Tableau 2 : Coefficients permettant le calcul des pertes totales dans le cas de diodes de redressement en parallèle, d'après l'équation (4).

|   | 2 diodes                | 3 diodes                |

|---|-------------------------|-------------------------|

| a | $-9,929 \times 10^{-6}$ | $-5,134 \times 10^{-7}$ |

| b | $3,578 \times 10^{-4}$  | $5,144 \times 10^{-6}$  |

| c | $-5,261 \times 10^{-8}$ | $-3,099 \times 10^{-8}$ |

| d | $2,911 \times 10^{-5}$  | $1,421 \times 10^{-5}$  |

| e | $2,38 \times 10^{-6}$   | $2,784 \times 10^{-6}$  |

| f | $-4,189 \times 10^{-3}$ | $6,958 \times 10^{-4}$  |

### 3.3. Parallélisation de diodes différentes

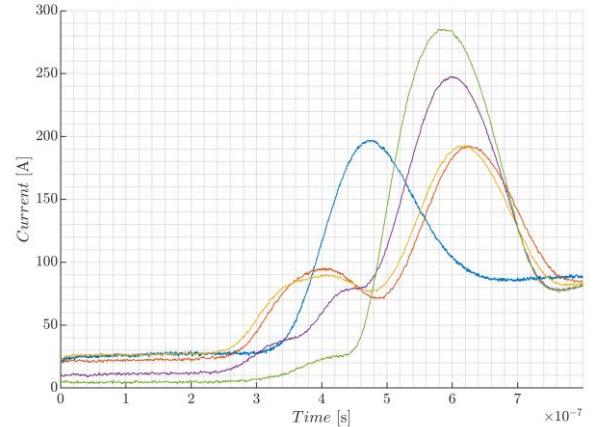

Comme évoqué au paragraphe 3.1, les diodes DD89N12K présentent des pertes importantes par recouvrement, en dépit de bonnes propriétés en conduction. Pour cette raison, nous nous sommes intéressés à l'effet de diodes en parallèles aux caractéristiques très différentes. La nouvelle configuration est représentée à la Figure 12 dans le cas d'une seule diode basse fréquence en parallèle avec une diode rapide. La déformation du courant et de la tension décrite précédemment continue de se produire, mais est beaucoup moins marquée lorsque peu de diodes de redressement sont utilisées, comme illustré à la Figure 13. Notons que la commutation a été accélérée de 0,1 µs par rapport au cas d'une diode de redressement seule, ce qui induit des pertes par commutation réduite.

Figure 12 : Schéma de la double avec deux diodes différentes : basse fréquence en blanc et rapide en gris. Cette dernière est toujours en bout des montages parallèles.

Figure 13 : Tensions mesurées aux bornes des diodes durant le recouvrement sous 100 V – 20 A : pour la diode de redressement seule (bleu), la diode rapide seule (orange) et pour une diode de redressement (violet) en parallèle de la diode rapide (vert). En jaune, la tension aux bornes de l'inductance.

La Figure 14 met en évidence la nouvelle dynamique des pertes avec l'ajout d'une diode rapide en parallèle des diodes de redressement. Par rapport à la diode rapide seule, la mise en parallèle de diode de redressement induit une forte augmentation des pertes. À mesure que le nombre de diodes de redressement en parallèle augmente, les pertes augmentent. Le cas le plus critique est celui d'une tension de 100 V, d'un courant de 30 A avec 3 diodes de redressement en parallèle et une diode rapide : les pertes augmentent d'environ 6000% par rapport à la diode rapide seule. Pour cette dernière, les pertes durant la commutation valent en effet 0,84 mJ dans ces conditions de test. A l'inverse, l'association décrite possède des pertes totales de 5,8 mJ.

Figure 14 : Evolutions des pertes totales en fonction du courant et de la tension pour 1 diode rapide seule (bleu foncé), 1 diode de redressement seule (bleu clair), 1 diode de redressement en parallèle en parallèle avec une diode rapide (vert), 2 diodes de redressement en parallèle en parallèle avec une diode rapide (orange) et 3 diodes de redressement en parallèle en parallèle avec une diode rapide (jaune)

Dans le cas où le composant à considérer est la diode rapide, l'association avec des diodes de redressement mis en parallèle conduit à dégrader fortement les performances de la cellule de commutation. Cependant, dans le cas où le composant à considérer dans la cellule de commutation est la diode de redressement, la parallélisation avec une diode rapide permet une diminution importante des pertes. Cette diminution va de 40 à 65% si une seule diode de redressement est considérée, contre 5 à 40% si 3 diodes de redressement sont mises en parallèle de la diode rapide.

Notons enfin que les pertes d'un assemblage de diodes différentes en parallèle se modélisent sur le même format que les pertes dans une diode.

Tableau 3 : Coefficients de l'équation (4) permettant le calcul des pertes totales dans le cas de 1, 2 ou 3 diodes de redressement en parallèle avec une diode rapide.

|   | 1 diode                 | 2 diodes                | 3 diodes                |

|---|-------------------------|-------------------------|-------------------------|

| a | $1,029 \times 10^{-6}$  | $5,039 \times 10^{-6}$  | $-2,34 \times 10^{-6}$  |

| b | $9,846 \times 10^{-6}$  | $-9,268 \times 10^{-5}$ | $1,679 \times 10^{-4}$  |

| c | $-2,842 \times 10^{-8}$ | $-4,136 \times 10^{-8}$ | $-2,901 \times 10^{-8}$ |

| d | $1,299 \times 10^{-5}$  | $2,242 \times 10^{-5}$  | $2,313 \times 10^{-5}$  |

| e | $8,036 \times 10^{-7}$  | $1,241 \times 10^{-6}$  | $1,124 \times 10^{-6}$  |

| f | $-9,18 \times 10^{-4}$  | $-1,049 \times 10^{-3}$ | $2,901 \times 10^{-8}$  |

#### 4. DISCUSSION DES RESULTATS

Le but premier des mesures effectuées dans cet article est de constater le comportement de diodes parallèles lors du recouvrement et leurs adéquations ou non avec des résultats théoriques connus. Pour cette raison, les mesures ne disposent pas de la meilleure précision possible car l'objectif est de déterminer des tendances. Plusieurs améliorations sont possibles afin de quantifier plus finement les pertes. Tout d'abord, afin de limiter les problèmes de bande passante, l'emploi de sondes passives peut être envisagé. Pour la mesure de tension, cela se traduit par l'emploi de sondes de tension non isolées, plutôt que de sondes différentielles. Pour la mesure de courant, l'emploi d'un shunt coaxial sera préféré lorsque son intégration est possible au PCB. Si ce n'est pas le cas, comme dans notre montage, l'emploi d'une sonde Rogowski sera préféré à une sonde à effet Hall, à condition de ne pas avoir de composante continue dans la mesure. La conséquence directe de ces changements réside dans la nécessité d'employer un oscilloscope isolé, mais également de revenir à une configuration « low side ». Cela doit permettre de limiter les effets de mode commun des sondes [12], [15].

Les mesures effectuées ont néanmoins permis de mettre en évidence la difficulté de la mise en parallèle de plusieurs diodes. Si une diode possède déjà de bonnes caractéristiques en commutation, ajouter en parallèle une diode optimisée pour la conduction conduit à une dégradation des performances en commutation. L'emploi d'une diode de redressement en parallèle pourrait cependant être pertinent dans le cas de topologies multiniveaux. En plaçant astucieusement cette dernière, il serait possible de la faire commuter très peu et de bénéficier au maximum de ces propriétés en conduction. De même, la mise en parallèle de N diodes identiques conduit à une dégradation des performances en commutation. Cette dégradation peut cependant être intéressante, si une diode de calibre équivalent à ces N diodes en parallèle possède encore plus de pertes commutations.

#### 5. CONCLUSION

La parallélisation de diodes constitue une solution permettant d'obtenir une bonne tenue thermique, mais induit une augmentation des pertes lors des commutations. Pour pallier ce phénomène, une solution consiste à mettre en parallèle une diode optimisée pour la commutation. Cependant, la déformation des formes d'ondes rend difficile l'utilisation de datasheets ou de simulations pour présumer des performances des composants en parallèle et leur positionnement. Seule une caractérisation des pertes, une fois l'assemblage défini permet de valider les performances et de fournir une extrapolation, tel que proposé

dans ce papier.

#### 6. REFERENCES

- [1] CIGRE, ‘Medium Voltage direct current (MVDC) grid feasibility study’.

- [2] D. Zhao, S. Jiang, D. Hu, Y. Wang, X. Jin, and C. Sun, ‘Summary and Prospect of Technology Development of MVDC and LVDC Distribution Technology’, in *2022 IEEE 5th International Electrical and Energy Conference (CIEEC)*, Nangjing, China: IEEE, May 2022, pp. 1294–1300. doi: 10.1109/CIEEC54735.2022.9845945.

- [3] INTERNATIONAL ELECTROTECHNICAL COMMISSION, ‘IEC/TR 63282 – LVDC systems – Assessment of standard voltages and power quality requirements’, 1, Nov. 2020.

- [4] K. Smith, D. Wang, A. Emhemed, S. Galloway, and G. Burt, ‘Overview paper on: low voltage direct current (LVDC) distribution system standards’, p. 24.

- [5] N. Chen, F. Chimento, M. Nawaz, and L. Wang, ‘Dynamic Characterization of Parallel-Connected High-Power IGBT Modules’, *IEEE Trans. on Ind. Applicat.*, vol. 51, no. 1, pp. 539–546, Jan. 2015, doi: 10.1109/TIA.2014.2330075.

- [6] J. Weigel, J. Boehmer, A. Nagel, and R. Kleffel, ‘Paralleling high power dual modules: A challenge for application engineers and power device manufacturers’, in *2017 19th European Conference on Power Electronics and Applications (EPE'17 ECCE Europe)*, Warsaw: IEEE, Sep. 2017, p. P.1-P.10. doi: 10.23919/EPE17ECCEurope.2017.8099203.

- [7] Andre Lenze, David Levett, Ziqing Zheng, and Krzysztof Mainka, ‘Hard Paralleling SiC MOSFET Based Power Modules’, *Bodo's Power Systems*, p. 26, Sep. 2020.

- [8] A. Yu, J. Sakai, K. Hatori, N. Soltau, and E. Wiesner, ‘Influence of IGBT and Diode Parameters on the Current Sharing and Switching-Waveform Characteristics of Parallel-Connected Power Modules’, in *2022 24th European Conference on Power Electronics and Applications (EPE'22 ECCE Europe)*, Hannover, Germany, Sep. 2022, p. 11.

- [9] STMicroelectronics, ‘Current sharing in parallel diodes’, 2014.

- [10] R. W. Erickson and D. Maksimović, *Fundamentals of power electronics*, Second edition, Softcover reprint of the hardcover 2nd edition 2001. New York, NY: Springer Science+Business Media, LLC, 2001.

- [11] P. Haaf, ‘Understanding Diode Reverse Recovery and its Effect on Switching Losses’, 2007.

- [12] Markus Herdin, Jens Schweickhardt, and Kevin Hermanns, ‘Tips & Tricks on Double Pulse Testing - From designing a test setup to performing accurate measurements’. Rhode & Schwarz, Mar. 2021.

- [13] L. Quéval, A. González-Parada, and F. Trillaud, ‘Station d'essai DC pour câbles électriques supraconducteurs’, presented at the Symposium de Génie Electrique (SGE 2023), Lille, France, Jul. 2023.

- [14] J. Allmeling and W. Hammer, ‘PLECS - User Manual’.

- [15] Tech Web, ‘About Double-Pulse Tests’. Jun. 23, 2021. Accessed: Sep. 25, 2022. [Online]. Available: [https://techweb.rohm.com/knowledge/si/si\\_sr/si\\_sr01/918](https://techweb.rohm.com/knowledge/si/si_sr/si_sr01/918)