# Contrôle ultra-rapide et intégré de dv/dt en boucle fermée lors de l'amorçage de transistors à semi-conducteurs grand-gap

Plinio BAU<sup>1,2</sup>, Marc COUSINEAU<sup>1</sup>, Bernardo COUGO<sup>2</sup>, Frédéric RICHARDEAU<sup>1</sup>, Nicolas ROUGER<sup>1</sup>

<sup>1</sup>LAPLACE, Université de Toulouse, CNRS, Toulouse, France <sup>2</sup>Institut de Recherche Technologique Antoine de Saint Exupéry (IRT SE), Toulouse, France

RESUME – Dans cet article, nous présentons une technique de contrôle actif de grille pour maitriser la vitesse de commutation de transistors de puissance à semi-conducteur grand—gap. Un circuit de commande rapprochée innovant, permet de ralentir la vitesse de commutation à l'amorçage du transistor de puissance, réduisant ainsi les perturbations CEM, sans pour autant impacter trop lourdement les pertes de commutation. La méthode proposée est implémentée dans deux circuits intégrés en technologie CMOS qui permettent d'obtenir des temps de réaction pour une boucle de rétroaction inférieurs à la nanoseconde. Avec de telles performances, il est montré expérimentalement qu'il est possible de contrôler des vitesses de commutation supérieures à 100 V/ns sous des tensions de 400 V.

Mots-clés— Active Gate Driver, circuit CMOS, électronique analogique, électronique de puissance, semiconducteur à grand-gap, MOSFET SiC, HEMT GaN, Compatibilité Electro-Magnétique (CEM).

#### 1. Introduction

L'utilisation de transistors de puissance à semi-conducteur grand-gap tels que les MOSFETs en Carbure de Silicium (SiC) et les Transistors à Haute-Mobilité-Electronique en Nitrure de Galium (HEMT GaN) repousse les limites usuelles en électronique de puissance. Grace à leur bon niveau de maturité actuel et leurs performances excellentes en vitesse de commutation, les transistors MOSFETs en SiC sont aujourd'hui un des vecteurs d'amélioration des convertisseurs statiques dans les applications aéronautiques (meilleurs rendements, couplé à une augmentation de la densité de puissance due à l'accroissement des fréquences de découpage, offrant une réduction de poids et du volume des convertisseurs).

Dans ce contexte, le contrôle de la vitesse de commutation des transistors GaN et SiC devient un élément critique si l'on considère le compromis existant entre pertes par commutation et perturbations électromagnétiques engendrées (CEM) [1]. En effet, l'augmentation de la vitesse de la commutation, offerte par ces nouveaux transistors de puissance, va engendrer une augmentation des sources de perturbations CEM, pouvant mettre en défaut l'intégrité du convertisseur sur tout ou partie de son cycle d'usage et son environnement rapproché. Le contrôle actif des fronts de commutation par le circuit de commande rapprochée (Active Gate Driver, en anglais) est une voie d'amélioration importante. Des travaux de recherche sont nécessaires à la fois sur la conception de fonctions spécifiques analogiques en technologie intégrée CMOS [2], [3] et également sur l'amélioration des performances de ce circuit de commande

intégré au sein de cellules de commutation à base de transistors à semi-conducteur grand-gap [4], [5], [6], [7].

Des travaux antérieurs de dispositifs de contrôle de vitesse de commutation ont déjà été publiés dans [8], [9] et [10]. Le Tableau 1 donne une comparaison de ces travaux avec ceux présentés ici et avant par l'équipe. [11] [12] [13] [14].

Tableau 1. Comparatif des dispositifs de contrôle de vitesse de commutation.

|                      | Ref [8]   | <b>Ref</b> [9] | Ref [10] | Cet article    |

|----------------------|-----------|----------------|----------|----------------|

| Année de publication | 2015      | 2016           | 2018     | 2020           |

| Vitesse de           | 27 V/ns à | ~20 V/ns       | >20 V/ns | 175 V/ns à 120 |

| commutation dv/dt    | 8.8 V/ns  |                |          | V/ns (HV GaN)  |

| Tension du bus DC    | 200 V     | 300 V          | 200 V    | 50V et 400V    |

| Résolution           | CMOS 180  | Discrets       | CMOS     | CMOS 180 nm    |

| technologie          | nm        |                | 140 nm   |                |

Cet article présente la conception d'une boucle de contrôle de vitesse de commutation intégrée ultra-rapide et montre les limites théoriques liées au choix de la technologie. Le chapitre 2 présente le circuit mis en jeu et montre la méthode retenue de dimensionnement des transistors utilisés. Le chapitre 3 aborde l'étude théorique de la bande passante de la boucle de rétroaction et donne le lien avec la fréquence de transition de la technologie. Le chapitre 4 est consacré à l'étude de la surface totale de silicium occupée par le circuit fonction de la répartition du gain de la boucle. Le chapitre 5 montre le circuit intégré réalisé ainsi que la carte de test. Enfin le chapitre 6 présente les résultats obtenus pour deux types d'application 50 ou 400V.

# 2. PRINCIPE DE LA METHODE UTILISEE AVEC OPTIMISATION ET DIMENSIONEMENT DES ELEMENTS CONSTITUTIFS.

## 2.1. Principe de la méthode

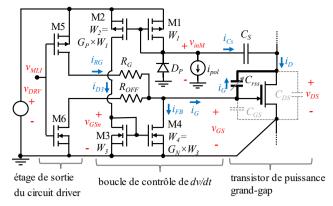

Afin de contrôler la vitesse de commutation en tension (dv/dt) sans affecter la vitesse de commutation en courant (di/dt), la méthode proposée consiste à émuler une capacité électronique présente entre le Drain et la Grille du transistor de puissance (Fig. 1). Cette méthode va permettre de contrôler la valeur apparente de cette capacité virtuelle par le biais d'une électronique intégrée rapide. Le principal bénéfice de cette approche consiste à contrôler le dv/dt lors de la commutation de façon séparée sans affecter le di/dt, permettant ainsi de réduire les sources de perturbations CEM sans pour autant augmenter considérablement les pertes occasionnées, par comparaison avec l'approche classique consistant à modifier la valeur de la résistance de grille.

Fig. 1. Schéma du circuit du buffer de commande rapprochée (Active Gate Driver) implémentant une boucle de rétroaction rapide pour le contrôle de la vitesse de commutation (dv/dt) durant l'amorçage. Tous les éléments sont implémentés dans un ASIC sauf les résistances de Grille et le composant de puissance. La méthode émule l'effet d'une capacitance virtuelle contrôlable électroniquement par un gain G pour améliorer le compromis vitesse de commutation vs, pertes par commutation.

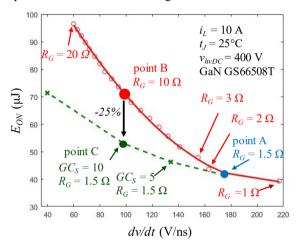

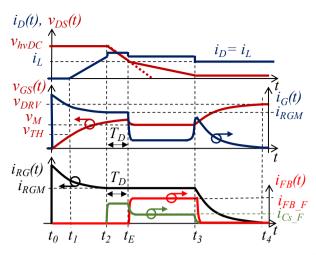

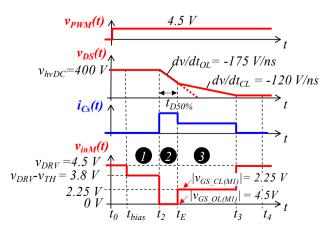

La Fig. 2 illustre l'objectif de la méthode proposée et la Fig. 3 indique les formes d'ondes des signaux obtenus.

Fig. 2. Simulation Cadence du compromis classique (en rouge) entre vitesse de commutation et énergie de commutation à l'amorçage et celui offert par la méthode (en vert pointillé). La methode a pour but de réduire les pertes par commutation pour une vitesse de commutation donnée pour les composants grand-gaps.

La vitesse de commutation de tension à l'amorçage d'un transistor de puissance est donnée par la valeur du courant qui charge la capacité Grille-Drain du transistor divisé par la valeur de cette capacité. En écrivant ce courant en fonction de la valeur de tension de Grille pendant le plateau Miller  $(v_{\rm M})$ , la valeur de dv/dt peut être donnée par l'expression :

$$\frac{dv_{DS}}{dt} = -\frac{i_{G_M}}{C_{rss}} = -\frac{v_{DRV} - v_M}{R_G \cdot (C_{rss} + G \cdot C_S)} \tag{1}$$

où  $C_{rss}$  est la capacité de grille-drain du transistor de puissance,  $v_{DRV}$  la valeur de tension de l'alimentation du circuit driver et  $v_M$  le niveau de tension du plateau Miller.  $R_G$  est la valeur de la résistance placée entre la grille du composant de puissance et la sortie du circuit driver. La variable G est le gain de la boucle de rétroaction proposée. La variable  $C_S$  est un condensateur "capteur" haute-tension utilisé pour mesurer la valeur de dv/dt durant la commutation et permettre une rétroaction depuis le potentiel de drain vers la sortie du circuit de commande rapprochée.

Fig. 3 Chronogramme montrant l'effet d'une capacitance virtuelle entre Grille et Drain d'un transistor de puissance. Elle va soustraire en effet un courant  $i_{\rm FB}$  seulement durant la phase du dv/dt d'une commutation. Le temps de retard de réaction de la boucle est représenté par le temps  $T_{\rm D}$ .

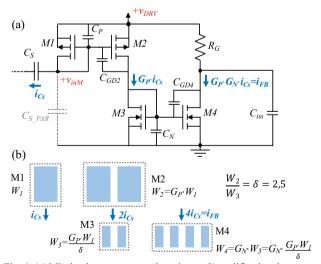

# 2.2. Modélisation du système de la boucle active de rétroaction

La Fig. 4 (a) montre la boucle de rétroaction utilisée pour contrôler activement le  $dv_{DS}/dt$  en considérant  $C_P$  et  $C_N$  la contribution des capacités intrinsèques des transistors PMOS et NMOS de la boucle de rétroaction sur leurs grilles respectives. La Fig. 4 (b) donne une représentation du layout des transistors et montre la surface nécessaire pour l'implémentation des transistors M1 à M4, en lien avec le schéma de la Fig. 1. Le cas avec  $G_P = 2$  et  $G_N = 2$  pour les gains des deux miroirs de courant M1-M2 et M3-M4 est illustré.

Une taille élémentaire, ou surface de référence, pour le transistor M1 est choisie. Son dimensionnement dépend du courant  $i_{Cs}$  fourni par le condensateur  $C_S$  ( $C_S$  pour « sensing capacitor ») et la valeur minimale de tension du nœud  $v_{inM}$  admissible. On peut voir que les tailles des transistors M2, M3 et M4 dépendent de celle de M1. Une valeur minimale pour la surface de M1 doit être calculée pour réduire la surface totale.

Fig. 4. (a) Miroirs de courant avec deux étages d'amplification de courant représentés avec leurs capacités intrinsèques. (b) Layout considérant un facteur de forme 2.5 entre les transistors NMOS et PMOS ( $G_P$ =2 et  $G_N$ =2).

#### 2.3. Dimensionnement de M1

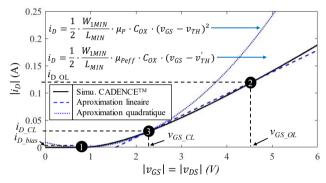

La Fig. 5 montre la caractéristique d'un transistor PMOS utilisé en configuration transdiode. Parce qu'il y a des effets de canal court observés dans les technologies CMOS submicroniques, deux zones d'opération doivent être considérées. La loi classique liant le courant drain du transistor au carré de l'écart de tension  $v_{GS}$ - $v_{TH}$  valable à faible courant, s'apparente plus à une fonction affine à fort courant. A l'aide de simulations paramétriques, dans une grande plage de valeurs de largeurs W du transistor, à tension  $v_{GS}$  constante (2.25 V par exemple), on observe l'existence d'une densité de courant constante. En considérant une longueur L minimale pour les transistors, le ratio constant  $i_D/W$  est très utile pour établir un lien entre la taille de la capacité  $C_S$  et la taille totale des transistors.

Le transistor M1 va opérer successivement sur les points 1, 2 et 3 indiqués dans la Fig. 5, et en lien avec le fonctionnement introduit dans les Fig. 3 et Fig. 6. Au départ, en l'absence de commutation du composant de puissance, on a  $i_{Cs}$ =0 A.

Fig. 5. Caractéristique  $i_D$  vs  $v_{DS}$  à 27°C du transistor PMOS M1 connecté en transdiode et extractions des paramètres par une linéarisation. Le point 1 est atteint avec un courant de pré-polarisation, ensuite le point 2 est atteint au tout début de commutation pendant un transitoire de moins de 1 ns, et enfin le point 3 est atteint correspondant à l'activation de la boucle de rétroaction (dv/dt ralenti).

Dans un premier temps, juste avant la commande d'amorçage du transistor de puissance, un courant de prépolarisation (voir Fig. 1) d'environ 50  $\mu$ A est généré et prépolarise M1 au point 1. Ensuite, quand la commutation démarre, le transistor M1 se déplace au point de polarisation 2 pendant une durée inférieure à 1 ns. Enfin, la boucle de rétroaction s'établie et permet de réduire le  $dv_{DS}/dt$  durant toute la suite de la commutation. Le courant  $i_{Cs}$  est alors réduit et M1 se polarise au point de fonctionnement 3. Il restera sur ce point jusqu'à la fin de la commutation si on considère une forme d'onde pour la tension  $v_{DS}$  parfaitement trapézoïdale. En pratique, pour le cas plus réaliste d'une forme d'onde non trapézoïdale présentant une décroissance progressive du dv/dt, W1 opère entre les points 3 et

Fig. 6. Représentation de la tension d'entrée des miroirs ( $v_{inM}$ ) en supposant une forme d'onde parfaitement trapézoïdale pour  $v_{DS}$ . Les points de fonctionnement 1, 2 et 3 présentés ici sont définies dans la Fig. 5.

Dans la Fig. 5 on peut noter que le point 2 ne doit pas dépasser la tension maximale  $v_{DVR}+0.6V$  au risque de voir la diode de protection  $D_P$  conduire et maintenir le nœud  $v_{inM}$  à la tension - 0.6V Dès lors, le courant recopié et amplifié par les miroirs PMOS et NMOS ne serait plus proportionnel au courant  $i_{Cs}$ . La taille minimale de M1 est calculée afin de placer le point 3 au niveau de tension  $v_{GS\_CL}=v_{DRV}/2$ . On doit vérifier par ailleurs que le point 2 est placé dans une zone sécurisée, inférieure à la tension maximale évoquée précédemment. Finalement, l'expression obtenue pour la largeur  $W_1$  est :

$$W_{IMIN} = \frac{i_{D1\_CL} \cdot L_{MIN}}{g_{mP} \cdot (v_{GS\ CL} - v'_{TH})}$$

(2)

où  $L_{MIN}$  est la longueur minimale de la technologie des transistors CMOS 5 V (typiquement 500 nm) et  $v'_{TH}$  est la tension de seuil effective issue de la linéarisation de l'expression du courant dans la Fig. 5 (proche de 1.5 V). La variable  $\mu_{Peff}$  est la mobilité effective des transistors PMOS à fort courant, c.-à-d. celle extraite dans la partie linéarisée de la Fig. 5.

# 2.4. Dimensionnement de $W_3$ en fonction de $W_2$

Le transistor M2 est un multiple de M1 et dépend du gain  $G_P$  choisi pour le 1<sup>er</sup> étage. Il est nécessaire de garantir que M2 opère toujours en régime saturé (source de courant). Pour ce faire, on va dimensionner la largeur W3 du transistor M3 afin d'obtenir  $v_{DS3}=V_{DRV}/2$ . Pour garantir la polarisation appropriée de M3, on introduit le paramètre  $\delta$ , ratio des mobilités effectives des transistors PMOS et NMOS à fort courant. En effet, en appliquant un facteur d'échelle et en garantissant que M3 est  $G_P/\delta$  fois plus grand que M1, sa tension  $v_{DS}$  atteindra inévitablement le niveau de tension souhaité. En pratique un ratio de  $G_P/2.5$  est obtenu. Enfin, la taille de M4 sera choisie égale à celle de M3 multipliée par le gain  $G_N$  du  $2^{\rm ème}$  étage.

$$W_3 = \frac{W_2}{\delta} \qquad \delta = \frac{\mu_{effN}}{\mu_{effP}}$$

(3)

# 3. ANALYSE ET OPTIMISATION DE LA BANDE PASSANTE

Afin de s'assurer d'être capable de contrôler la commutation du transistor de puissance à très haute vitesse, il est nécessaire d'établir l'expression de bande passante de la boucle de rétroaction en fonction des paramètres de la technologie CMOS et de s'assurer qu'elle est suffisante. À des fins d'analyse paramétrique, on établira son expression en fonction du gain  $G=G_P\cdot G_N$  des miroirs de courant et de la capacité  $C_S$ . On notera que pour une atténuation cible du dv/dt, le produit  $G\cdot C_S$  doit être considéré constant. Les valeurs des capacités totales vues sur les grilles respectives des transistors PMOS et NMOS sont données par (4) et (5).

$$C_{P} = (I + G_{P}) \cdot C_{GSp} + G_{P} \cdot C_{GDp} \cdot (I - a_{v_{P}}) + C_{DSp} + C_{S_{PAR}}$$

$$C_{P} \cong (I + G_{P}) \cdot C_{GSp} + C_{S_{PAR}}$$

$$(4)$$

$$C_{N} = (I + G_{N}) \cdot G_{P} \cdot C_{GSn} + G_{N} \cdot G_{P} \cdot C_{GDn} \cdot (I - a_{v_{\underline{n}}}) + G_{P} \cdot C_{DSn} + G_{P} \cdot C_{DSp}$$

$$C_{N} \cong (I + G_{N}) \cdot G_{P} \cdot C_{GSn} + G_{P} \cdot C_{DSn}$$

$$(5)$$

où  $av_p$  et  $a_{v_n}$  sont les gains en tension en régime petit signal des étages source-commune réalisés par M2 et M4 respectivement, (valeurs proches de 1),  $C_{GS}$ ,  $C_{GD}$  et  $C_{DS}$ , sont les capacitances grille-source, grille-drain et drain-source intrinsèques des transistors M1 à M4 et  $C_{S\_PAR}$  représente la capacité parasite montrée par l'électrode de  $C_S$  entre le nœud  $v_{inM}$  et la masse.

En pratique, les expressions des capacités  $C_P$  et  $C_N$  vues sur les grilles des transistors PMOS et NMOS peuvent être simplifiées en ne retenant que leur premier terme dépendant des capacités  $C_{GSp}$  ou  $C_{GSn}$ .

Afin de déterminer la bande passante de la boucle de rétroaction, connaissant les valeurs de capacités du circuit, les valeurs des impédances dynamiques des nœuds doivent être calculées. Les impédances vues sur les grilles sont imposées par les transistors M1 et M3 connectés en transdiode. Leurs valeurs sont liées aux transconductances  $g_m$  des transistors. Les expressions des constantes de temps associées,  $\tau_P$  et  $\tau_N$ , peuvent être écrite de la façon suivante :

$$\tau_P = \frac{C_P}{g_{ml}} \quad \text{et} \quad \tau_N = \frac{C_N}{g_{DS2} + g_{m3}}$$

(6)

où  $g_{ml}$  et  $g_{m3}$  sont les transconductances de M1 et M3 et  $g_{DS2}$  est l'admittance Drain-Source présentée par M2.

Les fréquences de coupure respectives des miroirs de courant PMOS et NMOS sont alors exprimés comme suit :

$$f_{cP} = \frac{1}{2 \cdot \pi \cdot \tau_P}; f_{cN} = \frac{1}{2 \cdot \pi \cdot \tau_N}$$

(7)

L'expression de la fréquence de transition  $f_T$  d'un transistor MOSFET est rappelée ci-dessous :

$$f_T = \frac{g_m}{2\pi \cdot \left(C_{GS} + C_{GD}\right)} \tag{8}$$

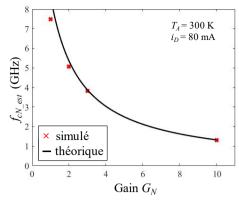

Elle indique, pour une technologie donnée, la fréquence maximale au-delà de laquelle le transistor ne peut plus fournir de gain. Il existe un lien entre la fréquence de coupure des miroirs de courant et cette fréquence de transition. En effet, augmenter W revient à augmenter la transconductance  $g_m$  ainsi que les valeurs de capacités intrinsèques. La fréquence de coupure reste constante et liée aux paramètres de la technologie. Les transistors M1 et M3 sont des montages transdiode qui opèrent toujours en régime saturé. Leur capacité  $C_{GD}$  est négligeable devant  $C_{GS}$ . Dès lors, en négligeant les contributions de  $C_{S\_PAR}$  et  $C_{DSp}$  dans (4) et (5), on obtient l'estimation suivante :

$$f_{cN} \approx \frac{f_T}{1 + G_N} = f_{cN\_est} \tag{9}$$

$$f_{cP} \approx \frac{1}{\delta} \cdot \frac{f_T}{I + G_P} = f_{cP\_est}$$

(10)

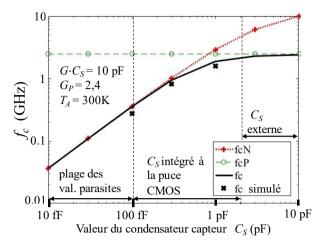

Les équations (9) et (10) montrent que réduire le gain des miroirs de courant permet d'obtenir une meilleure bande passante. Si l'on considère une atténuation de dv/dt donnée, soit un produit  $G \cdot C_S$  constant, il convient donc de privilégier des valeurs de condensateur  $C_S$  plus élevées. La Fig. 7 montre une comparaison entre les valeurs fournies par l'équation (9) et celles obtenues par simulation avec les modèles précis de la technologie utilisée sous Cadence<sup>TM</sup>. Il est à noter que malgré des gains élevés, compris entre 1 et 10, il est possible d'obtenir des bandes passantes élevées, de 1 à 8 GHz, ce qui permet d'envisager l'application de cette technique de rétroaction à une échelle temporelle inédite.

Fig. 7. Bande passante d'un miroir de courant NMOS en fonction de son gain en courant

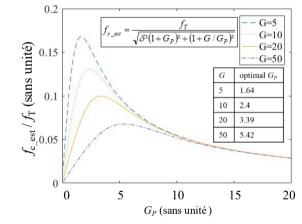

# 3.1. Répartition du gain G entre $G_P$ et $G_N$

La bande passante de la boucle de rétroaction, notée  $f_c$ , change en fonction de la distribution de gain G entre les deux étages d'amplification, c'est à dire entre  $G_P$  et  $G_N$  les gains des deux miroirs de courant. Une répartition optimale des gains peut être identifiée par une modélisation analytique et des simulations paramétriques. Une estimation de la bande passante  $f_c$  fonction des constantes de temps des miroirs de courant est proposée :

$$1/f_{c_{-est}} = \sqrt{1/f_{cN_{-est}}^2 + 1/f_{cP_{-est}}^2}$$

(11)

La Fig. 8 montre alors le choix optimal du gain  $G_P$  à réaliser afin de maximiser la fréquence de coupure totale, pour différentes valeurs de gain total G. On peut de nouveau observer que plus le gain G est élevé, plus la bande passante est réduite.

Fig. 8. Fréquence de coupure estimée normalisée de la boucle de rétroaction fonction du gain du  $1^{er}$  étage PMOS  $(G_P)$  pour plusieurs valeurs de gain G.

# 3.2. Répartition entre G et $C_S$

Pour une atténuation cible de  $dv_{DS}/dt$ , le produit  $G \cdot C_S$  est déterminé et imposé. Dès lors, une distribution optimale entre le gain G et la valeur de capacitance  $C_S$  doit être déterminée pour maximiser la bande passante  $f_c$  de la boucle de rétroaction. En effet plus  $C_S$  augmente plus le gain G diminue, cependant le courant  $i_{C_S}$  augmente et la taille des transistors augmente en conséquence (à densité de courant constante). Notons que M4 échappe à la règle et conserve, à  $G \cdot C_S$  constant, une taille constante.

A présent, pour calculer précisément  $f_c$ , toutes les capacités intrinsèques présentes dans (5) et (6) sont considérées. La Fig. 9 montre le résultat de calculs Matlab<sup>TM</sup>/Octave<sup>TM</sup> prenant en compte les paramètres appropriés de la technologie CMOS en considérant un produit  $G \cdot C_S$  égal à 10 pF. Les résultats de simulations Cadence<sup>TM</sup> utilisant  $C_S = 100$  fF, 300 fF et 1 pF confirment les projections théoriques. On observe que  $f_c$  augmente avec la capacité  $C_S$  et atteint une limite imposée par le

miroir de courant PMOS. Notons que, dans cette analyse, le terme  $G_P$  reste constant, alors que la Fig. 8 nous indique qu'il devrait être adapté à chaque nouvelle valeur de  $C_S$ .

Fig. 9. Bande passante de la boucle de rétroaction fonction de  $C_S$  pour un produit constant  $G \cdot C_S = 10$  pF.

#### 4. ANALYSE DE LA SURFACE TOTALE DE LA PUCE

Maintenant, en considérant un produit constant donné  $G \cdot C_S$ , nous allons analyser l'impact que peut avoir la répartition des valeurs entre G et  $C_S$  sur la surface finale de la puce CMOS. Les surfaces  $S_{Mp}$  et  $S_{Mp}$  des miroirs de courant PMOS et NMOS peuvent être exprimées respectivement par :

$$S_{Mp} = (I + G_P) \cdot \alpha \cdot L_{MIN} \cdot W_{IMIN}$$

(12)

$$S_{Mn} = G_P \cdot (I + G_N) \cdot \alpha \cdot L_{MIN} \cdot W_{3MIN} =$$

$$(G_P + G) \cdot \frac{\alpha}{\delta} \cdot L_{MIN} \cdot W_{1MIN}$$

(13)

où  $\alpha$  est un coefficient de foisonnement, c.-à-d. le rapport entre la surface active et la surface nécessaire pour concevoir et fabriquer les transistors.

Il est important de noter que  $W_{IMIN}$  est proportionnel à la taille de la capa  $C_S$  dû à l'augmentation du courant drain  $i_{DI}$  quand  $C_S$  augmente. Selon (2) il est possible d'écrire :

$$W_{IMIN}(C_S) = \frac{2L_{MIN}}{\mu_{Peff} \cdot C_{OX} \cdot (V_{GS\_CL} - V'_{TH})} \cdot \frac{dv_{DS}}{dt} \Big|_{CL} \cdot C_S;$$

$$W_{IMIN}(C_S) = \frac{1}{J_P \cdot L_{MIN}} \cdot \frac{dv_{DS}}{dt} \Big|_{CL} \cdot C_S$$

(14)

où  $J_P$  est la densité de courant de M1 lié au choix de  $v_{GS\_CL}$  (voir Fig. 5).

L'aire totale de silicium résultante ( $S_{tot}$ ) nécessaire à la réalisation du circuit proposé est liée à la surface des deux miroirs de courant augmenté de celle de la capacité haute-tension  $C_S$  embarquée dans la puce. Son expression est la suivante :

$$S_{tot}(C_S) = \left( \left( I + G_P \right) + G_P \cdot \left( I + \frac{G}{G_P} \right) \cdot \frac{I}{\delta} \right) \alpha \cdot L_{MIN} \cdot W_{IMIN}(C_S) + \frac{C_S}{C_S} (15)$$

$$S_{tot}(C_S) = \frac{1}{\delta} \cdot \frac{\alpha}{J_P} \cdot \frac{dv_{DS}}{dt} \Big|_{CL} (A_{tt} - I) \cdot C_{rss} + \left( \left( I + G_P \cdot (I + \frac{I}{\delta}) \right) \cdot \frac{\alpha}{J_P} \cdot \frac{dv_{DS}}{dt} \Big|_{CL} + \frac{I}{C_S'} \right) \cdot C_S$$

(16)

où  $C_S$ ' est la capacité surfacique (en F/ $\mu$ m²) obtenue dans la technologie CMOS entre les couches de métaux MET4 et MET6 servant à l'intégration monolithique de la capacité  $C_S$ ,  $A_{tt}$  représente l'atténuation désirée du dv/dt et  $dv_{DS}/dt_{CL}$  la valeur cible du dv/dt en boucle fermée.

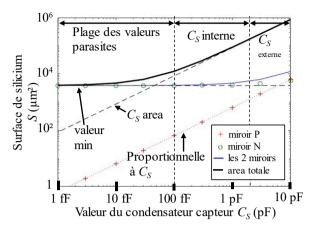

L'équation (16) possède une valeur plancher minimale pour des valeurs faibles de  $C_S$  imposée par la surface du miroir de courant NMOS. La Fig. 10 montre la surface totale  $S_{tot}$  en fonction de la valeur de  $C_S$  pour un produit constant  $G \cdot C_S$  (atténuation constante du dv/dt). La surface  $S_{tot}$  augmente de façon proportionnelle avec  $C_S$  pour des valeurs élevées de  $C_S$ .

Fig. 10. Surface silicium de la boucle de rétroaction fonction de  $C_S$  pour une atténuation donnée (produit  $G \cdot C_S = 10$  pF constant).

L'objectif étant d'obtenir une bande passante élevée, une valeur suffisamment élevée de  $C_S$  devra être choisie (voir Fig. 7) même si cela aura pour conséquence d'augmenter la surface nécessaire pour l'intégration complète de cette fonction dans la puce.

# 5. CIRCUIT INTEGRE ET CARTE DE TEST

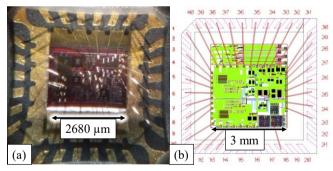

La Fig. 11(a) montre la puce en technologie CMOS-Bulk (AMS H18 180 nm) du circuit driver réalisée pour une application HEMT GaN (compatible composants 100V et 650V) et la Fig. 11(b), la puce CMOS en technologie CMOS-SOI (Xfab XT018 180 nm) en cours de fabrication pour une application MOSFETs de puissance en SiC.

Fig. 11. Circuit intégré analogique (ASIC) du Driver pour application (a) HEMT GaN et (b) MOSFET SiC.

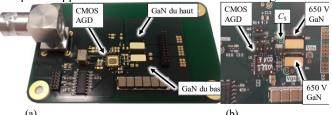

Plusieurs cartes de test multicouches (4 et 6 couches) ont été réalisées pour effectuer des mesures pour des applications ayant une tension de bus DC de 50 V et 400 V utilisant des transistors GaN. Grâce à l'utilisation d'un PCB multicouches, la surface de la maille de commutation peut être réduite afin de minimiser l'inductance parasite des différentes boucles et permettre une commutation à fort di/dt (> 1 A/ns) et dv/dt (> 100 V/ns). Une carte pour l'application 400 V est montrée dans la Fig. 12.

Fig. 12. Une des douze cartes réalisées pour application GaN. La vue de la (a) carte entière et (b) zoom pour la connexion bras d'onduleur avec commande

rapprochée. Pour une idée de taille, la puce de la commande rapprochée fait  $2,68 \text{ mm} \times 2 \text{ mm}$  dans un boitier QFN24  $6 \text{ mm} \times 6 \text{ mm}$ .

Pour effectuer les mesures expérimentales, une des précautions principales a consisté à minimiser la maille de mesure, notamment réduire la boucle de masse de la sonde de l'oscilloscope pour pouvoir avoir une bande passante de mesure suffisante. Le signal  $v_{GS}$  est alors mesuré et comparé avec les résultats de simulations.

#### 6. MESURES EXPERIMENTALES

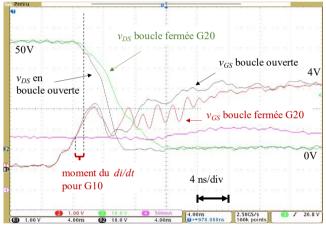

## 6.1. Application 50V

Pour une application 50 V, le transistor utilisé est le GaN EPC2001C (100 V, 36 A, 7 m $\Omega$ ) et montre expérimentalement une réduction du dv/dt à l'amorçage de 15 à 6,3 V/ns avec un courant de puissance de 1,3 A, ce qui correspond à une commutation avec une augmentation de 16% de  $E_{ON}$  seulement, au lieu de 30% dans le cas d'une modification de résistance de grille à même condition de courant Drain et dv/dt. Bien que la vitesse de commutation soit initialement modeste, il est néanmoins très important que la boucle de rétroaction agisse dans un temps très court, ici en moins d'une nanoseconde. Ce temps de réaction ultra rapide est obligatoire afin de réaliser un tel contrôle actif de la commutation dans cette application 50V.

Fig. 13 Mesure expérimentale du front de commutation à l'amorçage du GaN EPC2001C. Temps de réponse de la boucle inférieure à 1 ns et modification de la dérivé de *v*<sub>DS</sub>. On voit aussi que la méthode ne change pas la phase du *di/dt* et donc sa valeur.

La méthode peut être implémentée pour l'amorçage ou bien le blocage. Dans le cas du contrôle de la vitesse de blocage, la méthode devrait être adaptée de façon symétrique. Il est à noter également que l'utilisation de la boucle active de contrôle de l'amorçage n'a aucune influence sur la commutation au blocage, comme démontré expérimentalement dans la Fig. 14.

Fig. 14. Démonstration expérimentale que le contrôle actif de commutation à l'amorçage ne modifie pas la commutation au blocage.

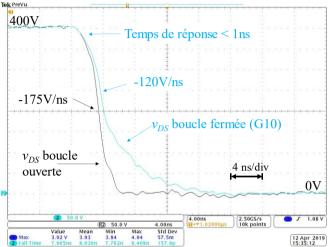

### 6.2. Application 400V

Pour une application 400 V, la méthode a également été validée avec le transistor HEMT de GaN Systems GS66508T (650 V, 30 A, 50 m $\Omega$ ). Son dv/dt d'amorçage est contrôlé et réduit activement de 175 V/ns à 120 V/ns (voir Fig. 15) pour un faible courant de charge de 2,5 A, condition pour obtenir un dv/dt élevé à l'amorçage. Des simulations précises dans CADENCE<sup>TM</sup> avec le design-kit de la technologie montrent qu'il est possible d'obtenir une augmentation de seulement 46% de l'énergie de commutation ( $E_{ON}$ ), pour un fort courant de charge de 20 A, au lieu de 100% si l'on modifiait directement la résistance de grille (mêmes conditions de courant de Drain et d'atténuation de dv/dt de 61%). Il s'agit ici de la démonstration expérimentale la plus rapide d'un système en boucle fermée de contrôle actif de dv/dt.

Fig. 15. Mesure expérimentale du front de commutation à l'amorçage du GaN GS66508T. Temps de réponse de la boucle inférieur à 1 ns et modification de la dérivée de  $v_{DS}$ .

Les données expérimentales de  $v_{DS}(t)$  à l'amorçage et au blocage mesurées avec la méthode à double impulsion sont fusionnées en un signal périodique, avec une fréquence de commutation de 1 MHz et un rapport cyclique de 0,5. La transformée de Fourier d'un tel signal  $v_{DS}(t)$  est représentée sur la Fig. 16 pour l'application 400 V, à la fois pour les commandes en boucle ouverte et en boucle fermée. Une expression analytique de l'atténuation attendue  $K_{\rm dB}$  (G20) à haute fréquence est fournie par (17). Par conséquent, dû à la réduction du dv/dt à l'amorçage avec la commande en boucle fermée, le spectre de  $v_{DS}$  est réduit à haute fréquence de 7,6 dB $\mu$ V à 100 MHz. Pour l'application 48 V, la réduction est de 13 dB $\mu$ V à 100 MHz, voir l'article publie par les mêmes auteurs [14] pour plus d'information.

$$K_{\mathrm{dB(G20)}} = 40 log \left(\frac{dv/dt_{(G20)}}{dv/dt_{(oL)}}\right) \tag{17}$$

$$\underset{170}{170}$$

$$\underset{150}{0}$$

$$\underset{150}{0}$$

$$\underset{120}{0}$$

$$\underset{170}{0}$$

$$\underset{170}{$$

Fig. 16. Spectre de  $v_{DS}$  à l'amorçage sans et avec activation de la contre-réaction pour réduire le dv/dt (application 400V avec GaN Systems 650V).

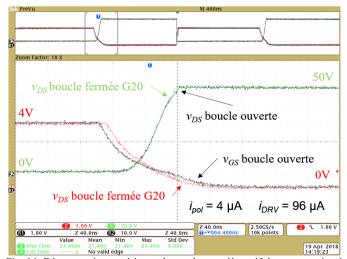

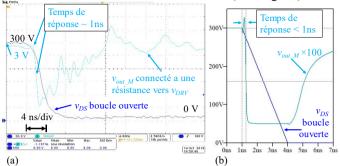

#### 6.3. Démonstration de retard maximum de 1ns

Une façon de montrer que le retard maximum de la boucle ne dépasse pas 1ns consiste à utiliser le montage en boucle ouverte, c.-à-d. ne pas brancher la sortie de la boucle de rétroaction à la grille du composant de puissance mais plutôt à une résistance elle-même connectée à  $v_{DRV}$  (voir Fig. 17).

Fig. 17. (a) Mesure et (b) simulation de la réponse de la boucle de rétroaction avec sa sortie connectée à une résistance de 14.7  $\Omega$  connectée á  $v_{DRF}$ .

#### 7. CONCLUSIONS

Une méthode de commande rapprochée innovante a été présentée. Elle montre la mise en œuvre d'une boucle de rétroaction sub-nano-seconde extrêmement rapide implémentée dans une technologie CMOS, boucle utilisée pour ralentir les fronts de commutation en dv/dt. Elle offre alors une réduction des émissions rayonnés (13 dB $\mu$ V à 100 MHz, pour application 48 V, et 7,6 dB $\mu$ V à 100 MHz pour les mesures à 400 V) dans une application de puissance avec moins de pertes qu'une méthode classique de réduction de vitesse de commutation.

Une analyse théorique exhaustive des performances de la boucle de rétroaction en termes de bande passante et de surface silicium occupée permet de guider le choix des valeurs des paramètres du système. Le lien entre les limites théoriques (bande passante maximale) et le choix de la technologie (sa fréquence de transition) est également donné.

Une telle vitesse de rétroaction laisse entrevoir de nouvelles perspectives en matière de contrôle et d'optimisation des commutations

Une nouvelle puce pour illustrer la méthode avec des composants MOSFET SiC 1200V compatible avec les composants C3M0075120k et C3M0016120K est en cours de fabrication, ainsi que des cartes prototypes des tests.

#### 8. References

- [1] Victor dos Santos, Bernardo Cougo, Nicolas Roux, Bruno Sareni, Bertrand Revol, et al., «Trade-off between Losses and EMI Issues in Three-Phase SiC Inverters for Aircraft Applications.,» chez IEEE EMC International Conference, Washington, 2017.

- [2] Mao, F. al., «A Power-Efficient Hybrid Single-Inductor Bipolar-Output DC-DC Converter with Floating Negative Output for AMOLED Displays,» chez IEEE Custom Integrated Circuits Conference (CICC), Boston, 2020.

- [3] Y. Barazi, Nicolas Rouger, Frédéric Richardeau, «Comparison between ig integration and vgs derivation methods dedicated to fast short-circuit 2D diagnosis for wide bandgap power transistors,» Mathematics and Computers in Simulation (Matcom), 2020.

- [4] T. Mannen, K. Wada, H. Obara, K. Miyazaki, M. Takamiya and T. Sakurai, "Active gate control for switching waveform shaping irrespective of the circuit stray inductance in a practical full-bridge IGBT inverter," chez IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, 2018.

- [5] Dymond, H. C. P. et al., «A 6.7-GHz Active Gate Driver for GaN FETs to Combat Overshoot, Ringing, and EMI,» *IEEE Transactions* on *Power Electronics*, vol. vol. 33 no. 1, pp. pp. 581-594, 2018.

- [6] N. Rouger, Y. Barazi, M. Cousineau and F. Richardeau, «Modular Multilevel SOI-CMOS Active Gate Driver Architecture for SiC MOSFETs,» chez 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Vienna, 2020.

- [7] Y. Barazi, N. Rouger and F. Richardeau, «CMOS Gate Driver with fast short circuit protection for SiC MOSFETs,» chez 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD). Vienna, 2020.

- [8] M. Rose, Y. Wen, R. Fernandes, R. Van Otten, H. J. Bergveld and O. Trescases, «A GaN HEMT driver IC with programmable slew rate and monolithic negative gate-drive supply and digital currentmode control,» chez IEEE 27th International Symposium on Power Semiconductor Devices & IC's (ISPSD), Hong Kong, 2015.

- [9] B. Sun, R. Burgos, X. Zhang and D. Boroyevich, «Active dv/dt control of 600V GaN transistors,» chez IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, 2016.

- [10] J. Yu, W. J. Zhang, A. Shorten, R. Li and W. T. Ng, «A smart gate driver IC for GaN power transistors,» chez IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, 2018.

- [11] P. Bau, M. Cousineau, B. Cougo, F. Richardeau, D. Colin and N. Rougers, «A CMOS gate driver with ultra-fast dV/dt embedded control dedicated to optimum EMI and turn-on losses management for GaN power transistors,» chez Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), Prague, 2018.

- [12] P Bau, M. Cousineau, B. Cougo, F. Richardeau, S. Vinnac, D. Flumian and N. Rouger, «Sub-Nanosecond Delay CMOS Active Gate Driver for Closed-Loop dv/dt Control of GaN Transistors,» chez International Symposium on Power Semiconductor Devices and ICs (ISPSD), Shanghai, 2019.

- [13] P. Bau, M. Cousineaul, B. Cougo, F. Richardeau and N. Rouger, «Modeling and Design of High Bandwidth Feedback Loop for dv/dt Control in CMOS AGD for GaN,» chez 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Vienna, 2020.

- [14] P. Bau, M. Cousineau, B. Cougo, F. Richardeau and N. Rouger, «CMOS Active Gate Driver for Closed-Loop dv/dt Control of GaN Transistors,» *IEEE Transactions on Power Electronics*, vol. 35, n° %112, pp. 13322-13332, 2020.