# Protection rapide et robuste contre les courts-circuits internes de convertisseurs à base de MOSFETs SiC

Yazan BARAZI, François BOIGE, Nicolas ROUGER, Jean-Marc BLAQUIERE, Sébastien Vinnac, Fréderic RICHARDEAU

Laplace, Université de Toulouse, CNRS, INPT, UPS, Toulouse, France

RESUME - Les MOSFETs SiC ont un court temps de tenue au court-circuit par rapport aux IGBTs Silicium. Pour répondre à cette problématique, trois méthodes de détection originales sont proposées et ont été mises en œuvre. Elles sont basées sur un diagnostic de signaux basse-tension accessibles et traités directement depuis le driver (IG, VGS), de manière indépendante du temps. La première méthode est dédiée aux MOSFETs SiC et repose sur la détection d'un niveau anormal de la fuite de grille sur la durée de conduction. La seconde est plus générale et plus rapide car elle utilise la surveillance de la charge de grille sur le cycle de commutation, connues sous le nom de « gate charge monitoring ». Cette dernière méthode est déjà connue pour les IGBTs Silicium mais encore peu développée pour les MOSFETs SiC. Les deux méthodes ont été expérimentées en technologie CMS et évaluées en termes de temps de réponse de robustesse, avec un temps de détection de 130 ns, pour une résistance de grille de 10 Ohms, en présence d'une capacité de grille de 1,7 nF. La troisième méthode de détection est intégrée sur puce en technologie CMOS. Elle est basée sur l'étude de la dérivée temporelle de V<sub>GS</sub>. La puce conçue regroupe les fonctions de commande rapprochée, de détection et de protection.

Mots-clés—MOSFET SiC- Court Circuit – fuite de grille – charge de grille - Détection & protection -

### 1. Introduction

Les MOSFETs en carbure de silicium (SiC) offrent plusieurs avantages, de faibles pertes en conduction et de commutation, une fréquence de découpage plus élevée qu'en technologie silicium et une grande stabilité en température [1]. Cependant aujourd'hui, la durée (T<sub>scw</sub>) et le nombre de cycles de tenue au court-circuit (CC) des MOSFETs SiC sont inférieurs à ceux des dispositifs en Silicium [2]. Les convertisseurs de puissance conçus avec ces composants sont donc moins robustes. Cette faiblesse doit être compensée par une protection dont le retard ne doit pas dépasser T<sub>scw</sub>/2, comme c'est le cas aujourd'hui pour les IGBTs silicum, ou encore moins si la robustesse aux CC répétés est requise. Plusieurs types de méthodes de détection CC ont été proposés pour IGBTs silicium et MOSFETs SiC [3]. La plupart des techniques reposent sur la détection d'un niveau de tension ou de courant drain-source de valeur anormale par rapport à un seuil [4]. La détection en tension est bien adaptée aux composants bipolaires tels que l'IGBT mais nécessite l'utilisation d'une diode rapide haute tension tandis que la détection en courant utilisée pour le MOSFET et parfois pour l'IGBT requiert une puce spécialement conçue avec miroir de courant [5], une électrode de mesure supplémentaire et aussi une

fenêtre de masquage relativement longue est nécessaire dans le cas de la méthode de détection de la tension drain-source afin d'atteindre un régime ohmique stable après le cycle de commutation [6].

#### 2. COMPORTEMENT DES MOSFETS SIC EN COURT-CIRCUIT:

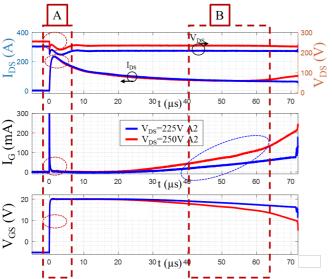

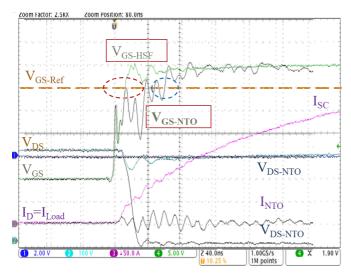

Il existe deux principaux types de CC, le Hard Switch Fault (HSF) (type I), qui est le défaut étudié, et le Fault Under load (type II, non abordé dans cet article), [7]. Le HSF se produit lorsque l'interrupteur est commandé avec une tension de bus pleine et permanente à ses bornes, généralement causé par des signaux de commande défaillants. Le FUL se produit lorsque le transistor est déjà en état de marche et qu'un court-circuit externe se produit. La Fig. 1 présente les formes d'ondes de commutation d'un MOSFET SiC sous fonctionnement normal (NTO) et sous CC (HSF). On peut remarquer brièvement, l'absence du plateau Miller, le changement sur les pentes au niveau de la tension grille-source, le changement au niveau du dV<sub>DS</sub>/dt et les surintensités au niveau du drain qui sont observées sous CC-HSF. Comme il sera présenté ci-après, ce comportement distinctif est utilisé pour détecter et protéger le MOSFET SiC en cas de HSF.

Fig. 1. Caractéristiques de l'amorçage du MOSFET SiC sous NTO et HSF.

En cas de défaut de CC, le MOSFET SiC présente une densité de courant de saturation transitoire très élevée en raison de la forte polarisation de grille  $V_{\rm GS}$  nécessaire à la minimisation de sa  $R_{\rm DS(ON)}$  [1]. Le courant de saturation élevé combiné au champ électrique élevé dans la zone de déplétion intercellulaire JFET implique une intense densité de puissance sur quelques microsecondes. La forte dynamique thermique qui en découle, en particulier au niveau de l'oxyde de grille, conduit à une injection d'électrons chauds fortement énergétiques dépendant principalement de l'effet d'émission Schottky [8].

Le comportement expérimental du MOSFET SiC en régime de CC HSF est représenté en Fig.2. Deux caractéristiques sont particulièrement intéressantes dans cette étude : l'absence du plateau Miller, traduisant une commutation sans  $dV_{DS}/dt$  donc incomplète et anormale, zone A de la figure ; puis l'apparition d'une forte fuite dynamique de courant de grille zone B de la Fig.2.

Fig. 2. Formes d'ondes experimentales du DUT montrant la fuite de courant de grille. DUT : 1.2 kV, 80 m $\Omega$  @ 25°C, Rgext = 10  $\Omega$ , Tcase = 25°C. Essais particuliers à forte dépolarisation de drain (225 V et 250 V comparée à 600 V de tension nominale) pour des besoins d'analyse de robustesse.

# 3. Surveillance et Detection a l'aide du courant de fuite de la grille :

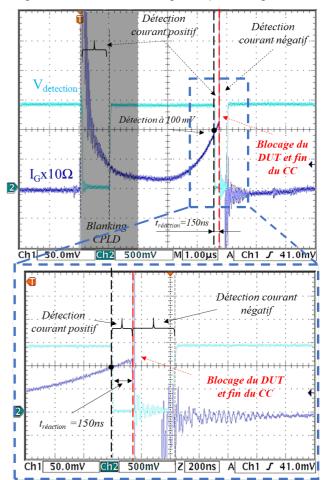

Le courant de fuite dynamique de la grille peut être observé sur l'intervalle de commande, après le cycle de commutation, sur la plupart des MOSFET SiC disponibles aujourd'hui [9]. La détection de ce courant est un marqueur a priori intéressant et original du CC comme l'illustre la Fig. 3. Image de la température, ce marqueur est dépendant de l'inertie thermique de la puce, conséquence du défaut. Il s'agit donc d'une méthode qui ne peut donc pas agir à l'échelle de la séquence de commutation bien qu'une variante adaptée peut être envisagée pour la rendre bien plus rapide mais elle ne sera pas développée dans cet article (\*). La méthode de détection présentée ici repose sur une détection de ce courant associé à un circuit logique dédié pour différentier l'état de fonctionnement normal par rapport à un CC. (\*) cf. F.Boige et al. SGE 2020, SS2 (FiabSurf)

Le principe du circuit de détection est basé sur une chaine de mesure et de détection analogique (non détaillée dans cet article) du courant de grille via la résistance de grille externe, utilisée comme shunt avec un excellent RSB (rapport signal sur bruit) car la fuite de grille atteint rapidement plusieurs mA à plusieurs dizaines de mA, en moins d'une microseconde, moyennent un délai de l'ordre de  $T_{\rm scw}/2$ . Puis, un CPLD Max V - Altera<sup>TM</sup> utilise le signal de commutation PWM comme référence pour générer une fenêtre programmable de masquage temporel de 2

µs (soit T<sub>scw</sub>/4) pour supprimer tout risque de déclenchement au moment de la charge normale de la grille. La Fig. 4 montre le principe de détection. L'électronique conçue et intégrée en CMS.

Fig. 3. Formes d'ondes experimentales du DUT. Détection du courant de fuite de grille et protection.DUT : 1.2 kV, 80 m $\Omega$  @ 25°C, Rgext = 10  $\Omega$ , Tcase = 25°C

Fig. 4. Schéma partiel de principe de détection de la fuite de courant de grille.

### 4. SURVEILLANCE DE LA CHARGE DE GRILLE.

Différemment de la méthode précédente qui n'est pas rapide mais robuste en termes de critère RSB, une seconde méthode est étudiée dans cet article. Cette méthode n'est pas basée sur la surveillance de la fuite de courant de grille, mais toujours au niveau de la grille. Cette méthode étudiée dépend de l'intégration rapide du courant de grille dans la séquence de charge de la grille à l'amorçage. La méthode connue sous le nom « gate charge » a déjà fait l'objet d'articles pour les IGBTs Silicium [10] et quelques résultats partiels pour les MOSFETs SiC en termes de performances et de mise en œuvre pratique [11]. Cette étude menée ici valide expérimentalement la méthode de gate charge et la gestion des défauts pour les MOSFETs SiC en utilisant des

composants CMS (composants montés en surface) et un circuit numérique intégré en fonctionnement réel sous pleine tension.

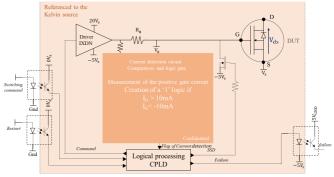

Cette méthode de charge de grille ne nécessite pas de diode haute tension pour la détection ou le réglage d'une période de masquage de détection. Cette méthode est aussi potentiellement robuste en termes de RSB sans pour autant rivaliser avec la méthode précédente. Dans le principe, Cette méthode nécessite un intégrateur ré-initialisable sur le front de commande ou un seuil de V<sub>GS</sub> pour estimer la quantité de charge de grille Q<sub>G</sub> ; et deux comparateurs. Le premier comparateur sert à distinguer la différence entre la quantité de charge en cas de CC Q<sub>G-CC-HSF</sub> et dans le cas de l'amorçage normal Q<sub>G-NTO</sub>; le second comparateur vient créer un drapeau de lecture en utilisant uniquement un franchissement de seuil du signal V<sub>GS</sub> compris entre la tension de plateau et le niveau de polarisation maximal, Fig. 5 [12], permettant une indépendance au temps et aux dispersions temporelles. Ensuite, les deux sorties des comparateurs sont envoyées dans un circuit logique (porte AND, bascule D) pour traiter cette double condition. Une fois que le CC a été détecté et traité par le circuit logique, le DUT est mis sous protection. Le circuit de protection est similaire à celui de la littérature (Soft Shut Down - SSD), où une résistance de valeur plus importante est utilisée pour décharger en douceur la grille du transistor de puissance. Le R<sub>DS(ON)</sub> du transistor auxiliaire SSD intégré est d'environ 7.5 ohms plus une résistance de 75 ohms en série, assurant un arrêt progressif. Avant l'activation du SSD, le gate driver passe à un état de haute impédance HZ (signal HZ dans la fig. 5.), où la grille du dispositif de puissance devient flottante afin de permettre au SSD d'agir pleinement.

Fig. 5. Circuit de principe de surveillance utilisant la méthode de gate charge.

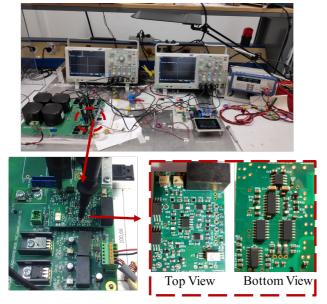

Fig. 6. (a). Banc de test, (b) carte dédiée à la détection.

Pour valider la méthode de détection par la surveillance de la charge de grille, une expérience a été menée pour la méthode de surveillance de la gate charge. La Fig. 6(a) a été proposée en utilisant un transistor MOSFET SiC de 1,2 kV-80 m $\Omega$ , C2M0080120D et une diode Schottky SiC avec une inductance de charge à air de 270  $\mu$ H pour le fonctionnement normal en double pulse. Une barrette de court-circuit en cuivre est utilisée pour le mode HSF. Le buffer de commande de grille utilisée est un IXDN614 à 3 états, permettant une configuration à haute impédance, Fig.6 (b). Fig.6 (b) illustre la carte de détection de CC. Une première carte prototype a été réalisée.

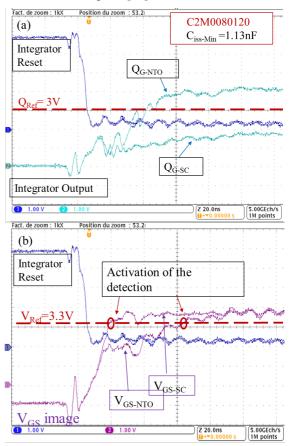

La charge de grille en fonction de V<sub>GS</sub> sous NTO et CC a été étudiée Fig. 7(a). Ce diagramme en 2D est bien connu pour l'étude de la méthode de la gate charge, il offre deux clés de détection importantes : la zone de détection, et le rapport S= Q<sub>G-CC-HSF</sub>/Q<sub>G-NTO</sub> ; avec Q<sub>G-NTO</sub> est égale à Q<sub>3</sub>. La Fig.7 (b) illustre expérimentalement la différence entre la quantité de charge sous fonctionnement normal et sous Hard switch fault.

Fig. 7. (a). Diagramme 2D ( $Q_G$ , $V_{GS}$ ) en fonctionnement normal (NTO) et CC (HSF) (b). Formes d'ondes experimentales de la sortie de l'intégrateur DUT : 1.2 kV, 80 m $\Omega$ @25°C, Rgext = 10  $\Omega$ , Tcase = 25 °C

Le circuit a été validé sous différentes valeurs de  $V_{Bus}$  entre (0-400V). L'expérience a été réalisée sous  $V_{Bus}$  = 400 V avec  $R_G$  = 10  $\Omega$ . Les formes d'ondes de l'oscilloscope sous NTO et CC-HSF, sont présentées Fig.8, et Fig.9.

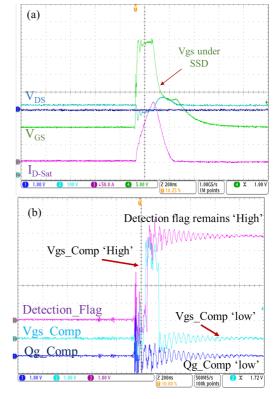

La Fig. 8 présente les formes d'ondes sur la grille et sur le drain ( $V_{\rm DS}$ ,  $V_{\rm GS}$ ,  $I_{\rm Load}$ ), sous NTO et SC-HSF. Les Fig.9 (a) et (b) présentent la quantité de charges stockées par la grille. Cette quantité est plus élevée que sous SC, ce qui active le comparateur de  $Q_{\rm G}$ , cette activation sera prise en compte au moment du basculement du comparateur de  $V_{\rm GS}$ . D'autre part, l'apparition d'un court-circuit (absence de dv/dt drain-source) sur les formes d'ondes du drain et de la grille, le circuit est sous CC, donc la quantité de la charge de grille est inférieure à celle en NTO, le comparateur de  $Q_{\rm G}$  reste bas, et à l'arrivée du signal du comparateur de  $V_{\rm GS}$  active la reconnaissance de détection de court-circuit.

Fig. 8. Formes d'ondes expérimentales du C2M0080120 DUT (LS) SiC à 400V en fonctionnement normal NTO avec diode Schottky SiC (HS) et sous CC-HSF avec band de cuivre (HS)

Pour une détection sélective entre NTO vs CC-HSF et un meilleur rapport S, l'instant de démarrage de l'intégration pourrait être contrôlé en ajoutant un autre niveau de seuil sur V<sub>GS</sub>. Malheureusement, cela réduit le niveau de sortie de l'intégrateur, donnant une plage de robustesse moindre pour les autres composants de puissance et un compromis doit être recherché.

Le drapeau de détection a été activé après 118 ns, incluant le temps de propagation du buffer (10 ns). Le temps de détection ne dépend pas seulement de la vitesse de notre système, il dépend aussi de la valeur de R<sub>G</sub>, de la capacité d'entrée du transistor de puissance, du dV<sub>GS</sub>/dt et du niveau de référence défini (>V<sub>GSM</sub>). La vitesse d'évolution de V<sub>GS</sub> entre NTO et CC-HSF est différente vue la différence entre les capacités chargées sous chaque fonctionnement; comme présenté dans la Fig. 9 (b). En d'autres termes après franchissement du seuil V<sub>GS-M</sub>, sous NTO V<sub>GS</sub> augmente avec une pente C<sub>ISS-MAX</sub> et sous CC-HSF avec une pente C<sub>ISS-MIN</sub>. Le front de comparaison de V<sub>GS</sub> sous CC-HSF arrive plus rapidement qu'en NTO, ce qui est positif pour détecter plus rapidement. Comme pour les niveaux de référence, le niveau de seuil a été défini à un niveau robuste de 18 V, autrement, avec un niveau inférieur la détection sera plus rapide mais avec un compromis sur le RSB.

On notera un délai de 60 ns entre le front d'échantillonnage  $V_{GS\_Comp}$  et le front de comparaison de la gate-charge en mode NTO. Ce délai pourrait être réduit en abaissant le seuil de comparaison et ainsi gagner en rapidité sur le mode CC-HSF de la Fig. 9 (b). Un compromis rapidité – immunité ou robustesse pourrait être recherché. Sur ce type de composant, une protection en moins de 500 ns est largement suffisante et la robustesse à la détection doit être privilégiée. Nous n'avons donc pas cherché à accélérer davantage la protection.

Après la détection du défaut, le MOSFET SiC doit être bloqué en toute sécurité en évitant une dangereuse surtension. Par conséquent, pour protéger le circuit en toute sécurité, un système d'arrêt progressif est inclus dans le circuit monté. Si le circuit de protection n'est pas bien conçu, une tension peut apparaître sur V<sub>DS</sub> due à un dI<sub>DS</sub>/dt négatif élevé à travers l'inductance parasite de la cellule de commutation, la protection doit être douce pour éviter ce phénomène.

Après l'activation de la bascule D (drapeau de détection), la sortie du driver IXDN614 est mise sous haute impédance (HZ), pour éviter de contre carrer le fonctionnement du SSD. Ensuite,

après un délai équivalent au temps de propagation du driver, le SSD est activé avec une résistance série  $R_{SSD} = 75 \Omega$ , pour bloquer lentement le transistor de puissance en déchargeant la capacité d'entrée de la grille [13].

Fig. 9. Formes d'ondes experimentales du DUT SiC à 400V en fonctionnement normal et court-circuit HSF. Détection, la gate-charge est inférieure au seuil.

Fig. 10. Formes d'ondes experimantal du DUT SiC à 400V sous protection du CC-HSF. (En utilisant la carte prototype).

La Fig. 10 présente les formes d'ondes du circuit sous court-circuit, avec le système de détection et de protection. Encore une fois les formes d'ondes du circuit prototype ont été utilisées afin de visualiser les formes d'ondes internes du circuit. Après le drapeau de détection, le buffer est placé sous HZ et le SSD est activé,  $V_{\rm GS}$  commence alors à diminuer doucement, limitant puis supprimant  $I_{\rm DS}$ . Le comparateur  $V_{\rm GS}$  revient au niveau bas mais le drapeau reste haut jusqu'à ce que la PWM du buffer passe au niveau bas, ce qui permet au système de faire un reset interne et activer à nouveau la détection/protection à la prochaine impulsion du PMW.

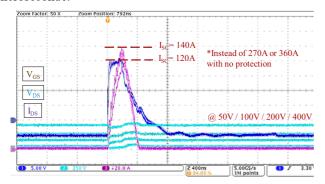

La limitation du courant de saturation sous court-circuit est présentée en Fig. 11 en utilisant la carte finale de détection et protection. Les résultats obtenus montrent une réduction dans un ratio supérieur à 50% du courant de saturation, ce qui permet de réduire très fortement l'amplitude du stress thermo-mécanique dans la région d'oxyde et ainsi permettre au composant une excellente robustesse sur CC répétitifs accidentels. Cette limitation a aussi été validée pour différentes variations de  $V_{\rm Bus}$ , différentes générations de MOSFET SiC, différentes inductances (de capacité parasite très différentes), ce qui prouve in fine sa robustesse

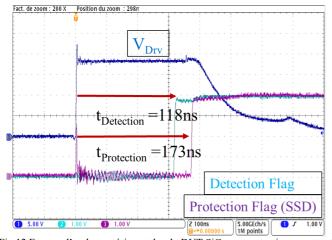

Le temps cumulé de détection et de protection de la carte finale sont présentés en fig. 12, montrant bien la protection submicroseconde.

Fig.11 Formes d'ondes expérimental du DUT SiC sous protection pour différent VBus.

Fig.12 Formes d'ondes expérimentales du DUT SiC sous protection, montrant le temps de détection et protection.

# 5. Integration des techniques de protection en CMOS

Afin de tirer parti des hautes performances dynamiques des MOSFETs SiC, le circuit de commande rapprochée « gate driver » doit s'adapter aux spécificités des MOSFETs SiC. Essentiellement, le courant de crête de charge, des courts délais de propagation, la capabilité du fonctionnement à haute fréquence et la faible consommation du circuit [14].

Les Gates Drivers pour les MOSFETs SiC, comparés à ceux des IGBTs Silicium, doivent avoir un temps de détection du CC et de protection du dispositif inférieur à 2µs. Les tendances récentes pour les gate drivers intégrés sont d'intégrer une variété de fonctions complexes pour améliorer encore les performances de la gestion de la commutation de puissance. La méthode de désaturation V<sub>DS</sub> est classiquement utilisée pour les IGBTs Si et aujourd'hui, pour les MOSFETs SiC à défaut d'alternative performante et économique. Rappelons que cette méthode nécessite une diode rapide haute tension, chemin sensible en présence d'un dv/dt entre le circuit de puissance et le circuit de commande de grille, ce qui rend cette méthode délicate et difficile à intégrer dans une technologie CMOS basse tension. Pour surmonter ces problèmes, un circuit de commande rapproché actif et rapide (« active gate driver ») est conçu en technologie CMOS pour détecter le CC et protéger les MOSFETs SiC, en utilisant uniquement des fonctions analogiques basse tension (transistors 5V et 40V).

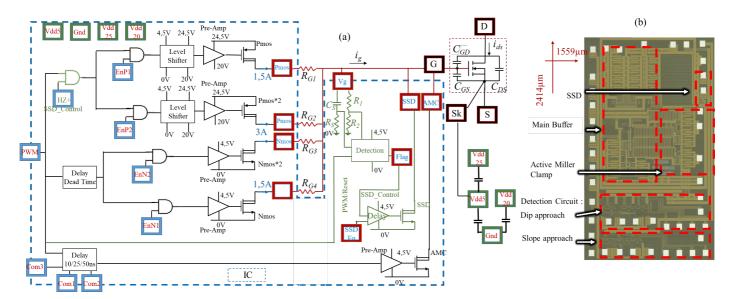

Le prototype du circuit intégré est basé sur la technologie SOI CMOS 0,18  $\mu m$  XT018 de XFAB. Cette technologie qui combine les avantages des plaquettes SOI avec une isolation profonde par DTI (Deep Trench Isolation) et six couches métalliques, une finesse de grilles basse tension de 0,18  $\mu m$ , ainsi que des transistors haute tension jusqu'à 200 V et un fonctionnement à haute température (175 à 225 °C). Ces propriétés facilitent la conception de ce circuit intégré, afin de fournir un courant élevé et de piloter le transistor de puissance avec la tension de grille exigée [15]. Ce gate driver comprend plusieurs fonctions, fig.13. (a) :

- Un buffer de sortie segmenté (40 V, +/- 4,5 A), utilisant des transistors 40 V proposés par la technologie. Les temps de propagation et de leur dispersion sont respectivement de 10 ns et 2 ns. La sortie segmentée du buffer permet trois configurations de courant (par exemple +/-1,5 A; +/-3 A; +/-4,5 A, 25 °C), cela est réalisable à la volée avec des transistors PMOS et NMOS divisées et à chaque sortie une résistance de grille est connectée. Cette sélectivité est configurable par des bits logiques (libellés, EnP1, EnP2).

- Cette segmentation permet un ajustement dynamique selon le point de fonctionnement du meilleur compromis vitesse de commutation, pertes en commutation par rapport aux perturbations électromagnétiques générées par des commutations rapides.

- Un "active Miller clamp" dit AMC actif (R<sub>DS(ON)</sub> < 1 Ω), protégeant efficacement le transistor de puissance contre les fronts de dv/dt élevés et verrouillant en toute sécurité le transistor de puissance en l'absence d'alimentation négative.

- Deux approches de détection CC différentes basées sur la méthode de dérivation [16]. Le circuit de détection a une surface de 150 μm x 200 μm, avec une consommation typique en courant continu de 1,52 mW (ou 0,34 mA à 4,5V, 25°C). Ces fonctions seront détaillées plus bas.

- Un soft shut down SSD pour un arrêt progressif  $(< 100\Omega)$ , dans un cas de court-circuit.

Le layout de l'ensemble des fonctions intégrées dans l'ASIC CMOS est divisé en deux parties principales. Le gate driver est de 2414  $\mu m$  x 1559  $\mu m$ , y compris les condensateurs de découplage des alimentations du circuit qui sont partiellement intégrés.

Fig. 13. (a). Schéma principe du circuit intégré, gate driver (b).vue microscopique du circuit intégré.

Le bloc de détection pour les deux techniques de détection a une surface de  $150~\mu m$  x  $200~\mu m$ , et le SSD a une surface de  $80~\mu m$  x  $30~\mu m$ . La Fig.13. (b) présente une vue microscopique de la puce. La puce est mise dans un boitier QFN40 6 mm x 6mm.

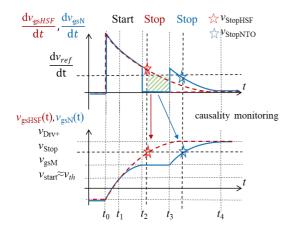

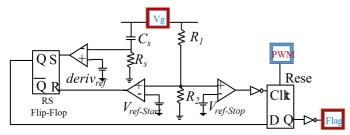

# 6. ETUDE DU CIRCUIT DE DETECTION INTEGRE EN CMOS

La méthode intégrée de surveillance est la méthode de la dérivation de  $V_{\rm GS}$  qui est basée sur une détection par un circuit dérivateur analogique RC dans la séquence de plateau ( $V_{\rm GS}$  proche de  $V_{\rm GSM}$ ). L'approche étudiée est l'approche par détection de creux, i.e. la présence ou non du plateau de Miller, Fig.14. Le schéma de détection du creux est proposé dans la fig. 15.

Fig. 14. Caracteristique de la dérivée  $dV_{GS}/dt$  sous NTO et CC-HSF. La causalité de surveillance dépand de l'approche du creux.

Fig. 15. Circuit de détection intégré au sein de l'active gate driver.

Les formes d'ondes expérimentales ( $V_{GS}$ ,  $V_{DS}$ ), du transistor de puissance DUT (C2M0080120) ont été importées dans

Cadence<sup>TM</sup> pour concevoir et évaluer virtuellement le circuit de cette méthode, associée avec les modèles fournis par le fabriquant CMOS (XFAB XT018 180 nm). La Fig. 16 présente la dérivée de V<sub>GS</sub> sous CC-HSF, où il n'y pas de creux.

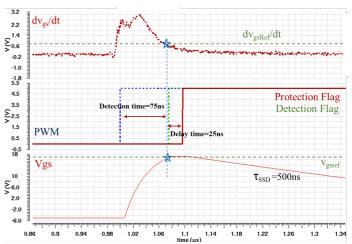

La lecture du creux se produit à l'arrivée du signal  $V_{\rm GS-Ref}$ , à ce moment-là, la référence  $dV_{\rm GSRef}/dt$  joue le rôle de détermination pour les deux modes NTO et CC-HSF, si un creux a été détecté et mémorisé avant ou pas. Dans le cas de la fig.16 où il y a une détection de CC après 75ns, la protection se fait après 25ns, le temps de propagation du circuit de détection plus le délai du gate driver.

Fig. 16. Formes d'ondes simulées sur cadence de DUT sous protection douce,  $dV_{\rm GS}/dt$  est la dérivée de la forme d'onde expérimentale du  $V_{\rm GS}$

#### 7. CONCLUSION

La tenue en CC réduite du MOSFET SiC implique un délai de protection inférieur à 4µs voire 1µs contre moins de 10µs sur des composants en silicium. Partant d'une méthode spécifique basée sur la fuite de grille antérieurement réalisée, deux autres méthodes de détection plus génériques sont proposées et développées : la première, dite gate-charge, est conçue en technologie CMS et la seconde, dite V<sub>GS</sub> dérivation, est basée sur un circuit intégré CMOS incluant différentes fonctions de détection. Dans un premier temps, la méthode de surveillance de la charge de grille corrélée à la tension V<sub>GS</sub> (diagnostic 2D) permet de détecter le défaut au cours de la commutation en 130 ns. A noter que la méthode de détection spécifique par la

fuite de la grille, plus lente, peut venir confirmer ou redonder la première détection de la défaillance pour plus de sûreté.

Un circuit intégré en technologie CMOS regroupant les fonctions de commande rapprochée, de détection et protection a aussi été conçu et présenté. Les deux niveaux d'intégration technologiques ont un impact direct dans la rapidité de la détection.

L'intérêt d'une protection sub-microseconde pour le MOSFET SiC est de pouvoir réduire l'amplitude du stress thermo-mécanique dans la région d'oxyde et ainsi permettre au composant une excellente robustesse sur CC répétitifs accidentels. Une étude de robustesse sur la sensibilité des paramètres (seuils, point de fonctionnement et dispersions composant) reste à mener pour dégager des éléments de choix entre les méthodes de détection présentées.

#### 8. References

- [1] B. J. Baliga, Silicon Carbide Power Devices. World Scientific, 2005.

- [2] C. Chen, D. Labrousse, S. Lefebvre, M. Petit, C. Buttay, et H. Morel, «Study of short-circuit robustness of SiC MOSFETs, analysis of the failure modes and comparison with BJTs », *Microelectronics Reliability*, vol. 55, n° 9-10, p. 1708-1713, août 2015, doi: 10.1016/j.microrel.2015.06.097.

- [3] D. Sadik et al., «Short-Circuit Protection Circuits for Silicon-Carbide Power Transistors», IEEE Transactions on Industrial Electronics, vol. 63, n° 4, p. 1995-2004, avr. 2016, doi: 10.1109/TIE.2015.2506628.

- [4] T. Bertelshofer, A. Maerz, et M.-M. Bakran, « Design Rules to Adapt the Desaturation Detection for SiC MOSFET Modules », in PCIM Europe 2017; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, mai 2017, p. 1-8.

- [5] J. Person, M. Andresen, T. Rettmann, O. Muehlfeld, et M. Liserre, « Short Circuit Detection Methods for Silicon Carbide (SiC) Power Semiconductors », in PCIM Europe 2019; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, mai 2019, p. 1-7.

- [6] S. Mocevic et al., «Comparison between desaturation sensing and Rogowski coil current sensing for shortcircuit protection of 1.2 kV, 300 A SiC MOSFET module », in 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), mars 2018, p. 2666-2672, doi: 10.1109/APEC.2018.8341393.

- [7] M. Cui, J. Li, Y. Du, et Z. Zhao, « Behavior of SiC MOSFET under Short-Circuit during the On-State », IOP Conference Series: Materials Science

- and Engineering, vol. 439, p. 022026, nov. 2018, doi: 10.1088/1757-899X/439/2/022026.

- [8] F. Boige, D. Trémouilles, et F. Richardeau, « Physical Origin of the Gate Current Surge During Short-Circuit Operation of SiC MOSFET», *IEEE Electron Device Letters*, vol. 40, nº 5, p. 666-669, mai 2019, doi: 10.1109/LED.2019.2896939.

- [9] « Gate leakage-current analysis and modelling of planar and trench power SiC MOSFET devices in extreme short-circuit operation | Elsevier Enhanced Reader ». https://reader.elsevier.com/reader/sd/pii/S0026271417302731?token=6D 4CF5A745796AF00D45A939777D60420AC729AFE0B0032F130931D AD90936BBD132F3B1E5C6842A11E7C841215651AA (consulté le nov. 04, 2019).

- [10] K. Oberdieck, S. Schuch, et R. W. DeDoncker, « Short circuit detection using the gate charge characteristic for Trench/Fieldstop-IGBTs », in 2016 18th European Conference on Power Electronics and Applications (EPE'16 ECCE Europe), sept. 2016, p. 1-10, doi: 10.1109/EPE.2016.7695402.

- [11] T. Horiguchi, S. Kinouchi, Y. Nakayama, et H. Akagi, « A fast short-circuit protection method using gate charge characteristics of SiC MOSFETs », in 2015 IEEE Energy Conversion Congress and Exposition (ECCE), sept. 2015, p. 4759-4764, doi: 10.1109/ECCE.2015.7310332.

- [12] T. Horiguchi et al., « Short-Circuit Protection Method Based on a Gate Charge Characteristic », IEEJ Journal of Industry Applications, vol. 4, nº 4, p. 360-369, 2015, doi: 10.1541/ieejjia.4.360.

- [13] X. Liao, Q. Shen, Y. Hu, C. Yang, X. Chen, et H. Li, « Fault protection for a SiC MOSFET based on gate voltage subjected to short circuit type II », *Microelectronics Reliability*, vol. 107, p. 113624, avr. 2020, doi: 10.1016/j.microrel.2020.113624.

- [14] D.-N. To, N. Rouger, Y. Lembeye, J.-D. Arnould, et N. Corrao, « Modeling and characterization of 0.35 μm CMOS coreless transformer for gate drivers », in 2014 IEEE 26th International Symposium on Power Semiconductor Devices IC's (ISPSD), juin 2014, p. 330-333, doi: 10.1109/ISPSD.2014.6856043.

- [15] B. Vogler, R. Herzer, M. Dienstbier, et S. Buetow, «Fully integrated high voltage high current gate driver for MOSFET-inverters», in 2017 29th International Symposium on Power Semiconductor Devices and IC's (ISPSD), mai 2017, p. 271-274, doi: 10.23919/ISPSD.2017.7988912.

- [16] « Barazi Yazan, Nicolas Rouger, Frédéric Richardeau. Comparison between ig Integration and vgs Derivation methods dedicated to fast Short-Circuit 2D-Diagnosis for Wide Band Gap Power Devices. ELECTRIMACS 2019, May 2019, Salerno, Italy. (hal-02180892) ».