# Méthode de mesure du courant de fuite de grille comme indicateur de vieillissement dédiée aux Gate Drivers

Julien Weckbrodt<sup>1, 2</sup>, Antoine Laspeyres<sup>1</sup>, Nicolas Ginot<sup>1</sup>, Christophe Batard<sup>1</sup>, Thanh Long Le<sup>2</sup>, Stéphane Azzopardi<sup>2</sup>

<sup>1</sup> Université de Nantes, <sup>2</sup> Groupe SAFRAN

RESUME - Cet article présente une nouvelle méthode d'estimation du courant de fuite de grille pour les composants de type MOSFET SiC. Cette méthode est directement intégrée dans un gate driver et permet d'assurer une mesure tant en mode « off line » que « on line ». Elle présente l'intérêt d'exploiter la structure naturelle des gate drivers sans une complexification excessive. Les résultats de mesure montrent une capacité à estimer des courants de fuite allant de 30 nA au mA. Cette méthode de mesure a été intégrée à un gate driver industriel, ce dernier assurant également de nombreuses autres mesures ainsi que le transfert des données vers le contrôle commande. Ces résultats sont issus d'une étroite collaboration avec le groupe SAFRANTECH.

Mots-clés—Gate Drivers, fuite de grille, SiC, monitoring, viellissement.

## 1. Introduction

Le paramètre  $I_{GSS}$  représente le courant de fuite grille-source avec le drain connecté à la source. Ce courant, à l'échelle du nA est extrêmement faible par rapport au courant de drain  $I_D$  typique. Généralement, le courant  $I_{GSS}$  est obtenu par mesure hors ligne à l'aide d'un traceur de courbe ou d'un fA-mètre [1]. Par conséquent, la mesure du courant de fuite de grille pendant le fonctionnement normal de l'équipement sous test (DUT) représente un véritable défi. La surveillance en ligne de ce courant est clairement identifiée comme un indicateur de vieillissement du composant [2]. Des études ont rapporté une méthode de détection en ligne du courant de fuite de grille dans les MOSFET SiC [3-4]. Cette technique consiste à mesurer la tension aux bornes de résistance de grille à l'aide d'un amplificateur différentiel pour en déduire le courant de grille.

Ce circuit peut être aisément intégré dans un gate driver mais les courants inferieurs au mA ne peuvent pas être mesurés par cette méthode. Dans cet article, nous proposons une méthode en ligne permettant l'estimation du courant de fuite de grille. Le principe proposé permet d'estimer de très faibles courants de fuite (qq 10 nA) en exploitant une structure particulière du gate driver. La méthode théorique proposée est expliquée dans la section II. Dans la partie III est présenté un gate driver industriel intégrant cette fonction de mesure de la fuite de grille. Enfin, la partie IV relate quelques essais expérimentaux.

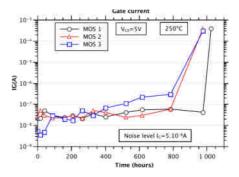

Fig. 1. Evolution du courant de fuite de grille durant un test de vieillissement [20].

## 2. METHODE DE MESURE DE LA FUITE DE GRILLE

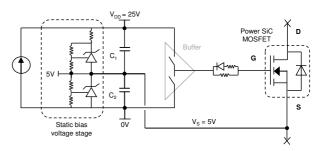

Etant donné la très faible valeur des courants de fuite de grille à mesurer une méthode par mesure directe n'est pas envisageable. La méthode proposée consiste à mesurer ce courant par intégration. Elle présente l'avantage d'exploiter la structure de l'alimentation du gate driver. Comme le montre la figure ci-dessous, les tensions de commande de grille typiques V<sub>GSON</sub> et V<sub>GSOFF</sub>, respectivement égales à +20V et -5V, sont dans la plupart des gate drivers fabriquées à partir d'une source continue de 25V subdivisée en une source +5V et une source +20V à l'aide d'un pont diviseur capacitif. Ce dernier permet également de fournir les pointes de courant de grille. La structure à grille isolée des MOSFETs permet d'équilibrer le pont diviseur capacitif simplement avec l'ajout d'une polarisation statique de l'ordre de 1 mA. Dans l'exemple, cette polarisation est obtenue avec des diodes zeners programmables de type TL431.

Fig. 2. Source d'alimentation typique pour le pilotage des MOSFETs (Si ou SiC)

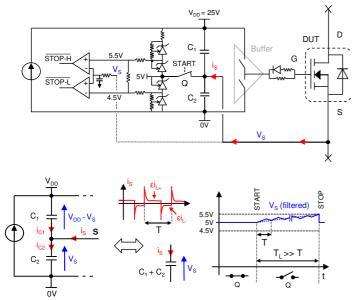

Imaginons qu'à un instant t appelé « START » le point de polarisation se trouve déconnecté du pont diviseur capacitif, alors le potentiel nommé  $v_S$  va diverger au grès de la valeur du courant moyen circulant entre la grille et la source du MOSFET. Ce courant moyen n'est autre que le courant de fuite de grille du composant.

Définissons alors deux butées au voisinage de la tension  $v_s$ , soit  $v_s + 500$  mV et  $v_s - 500$  mV (c'est-à-dire  $4,5 \text{V} < v_s < 5,5 \text{V}$ ) et comparons la tension  $v_s$  à ces deux butées. L'instant t nommé « STOP » correspond à l'instant où  $v_s$  atteint la butée haute (5,5 V) ou la butée basse (4,5 V). Connaissant la valeur des capacités  $C_1$  et  $C_2$  et en mesurant le temps écoulé entre les instants START et STOP, il est possible en théorie de déduire le courant moyen de fuite de grille. Dans la pratique une calibration est bien évidemment nécessaire.

La mise en œuvre de cette méthode est assez simple comme le montre la figure 3.

Fig. 3. Méthode proposée par integration pour l'estimation du courant de fuite de grille.

Le courant  $i_S$  peut s'exprimer comme une fonction du courant de fuite  $I_{L,DUT}$ . Dans l'équation (1), le courant de grille  $i_G$  est défini comme le courant réellement utile à la commande du transistor tandis que le terme  $I_{L,DUT}$  désigne les fuites parasites dans la grille.

$$i_S(t) = i_G(t) + i_{L,DUT}(t), < i_G > = 0$$

(1)

$$V_S(t) = \frac{1}{C_1 + C_2} \int_0^{T_L} i_{L,DUT}(t) dt$$

(2)

Le calcul intégral de l'équation (2) nécessite un modèle comportemental du courant de fuite de grille. En considérant un modèle résistif, la dérive en tension après n périodes T du signal MLI peut s'exprimer comme suit :

$$\Delta V_{S,n} = \frac{1}{c_1 + c_2} \left[ n \int_0^{\alpha T} \varepsilon i_{L+} dt + n \int_{\alpha T}^T \varepsilon i_{L-} dt \right]$$

(3)

$$\Delta V_{S,n=T_L/T} = \frac{n\,T}{c_1 + c_2} \underbrace{\left[\alpha\,\varepsilon i_{L+} + (1-\alpha)\varepsilon i_{L-}\right]}_{<\hat{i}_S>} \tag{4}$$

Où  $\varepsilon i_{L+}$  et  $\varepsilon i_{L-}$  sont respectivement les courants de fuite élémentaires pendant l'amorçage et le blocage. En conséquence, après  $T_L = n T$ , le courant de fuite moyen mesuré  $I_{L,MES}$  par la méthode proposée s'obtient en utilisant l'équation (5).

$$\langle i_S \rangle = I_{L,MES} = I_{L,DRIVER} + I_{L,DUT} = (C_1 + C_2) \frac{\Delta V_S}{T_L}$$

(5)

Où  $I_{L,DRIVER}$  est le courant de fuite parasite dû aux fuites des composants utilisés dans le driver. Pour des courants très faibles, le temps de mesure  $T_L$  est relativement long tandis qu'un courant de fuite excessif induit un temps de mesure plus rapide.

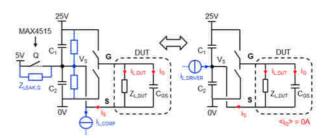

Fig. 4. Courants de fuite sur le driver de grille.

Comme l'illustre la figure 4, le courant de fuite résultant I<sub>L,MES</sub> représente le courant de fuite total vue par la source (S) en incluant les fuites liées au système I<sub>L,DRIVER</sub>. Les courants de fuites du système sont principalement dus aux courants de fuites dans les condensateurs C1 et C2 et dans l'interrupteur Q ainsi qu'aux courants d'entrée des comparateurs (I<sub>L,COMP</sub>) et les fuites dans le PCB. Par conséquent, une calibration en courant est nécessaire pour atteindre une précision à l'échelle du nA. La valeur obtenue à la calibration est ensuite utilisée comme référence pour toute la durée de vie du composant testé. Evidemment, les courants de fuite du système ainsi que la valeur des capacités C1 et C2 peuvent également varier au cours du processus de vieillissement. C'est la raison pour laquelle la valeur de fuite obtenue par l'équation (5) peut seulement permettre une estimation ou approximation de la valeur réelle de fuite de grille I<sub>GSS</sub> du composant testé. Toutefois, l'objectif ici n'est pas de mesurer précisément un courant de fuite mais bien d'observer une évolution de cette grandeur. Par exemple, pouvoir dissocier un composant usé qui fuite à 100µA d'un composant neuf dont la fuite est inférieure à 100nA ne nécessite pas une mesure précise au nA près, l'ordre de grandeur est suffisant.

La méthode proposée peut être implémentée comme une méthode de surveillance hors-ligne aussi bien qu'en cours de fonctionnement. L'évaluation des courants de fuite hors-ligne peut s'effectuer lorsque le convertisseur est à l'arrêt. Pendant  $T_L$ , si  $I_{L,DRIVER}$  est nul, le potentiel de source  $V_S$  augmente naturellement si le composant testé est passant  $(V_{GS,ON} = +20V)$  et diminue naturellement si le composant testé est bloqué  $(V_{GS,OFF} = -5V)$ . La variation linéaire de  $V_S$  s'explique par la charge/décharge de  $C_1 + C_2$  à courant constant. Par exemple, lorsque le composant testé est passant,  $C_1$  se décharge tandis que  $C_2$  se charge pendant la phase d'estimation.

Bien que la surveillance hors-ligne est intéressante pour une évaluation précise du courant de fuite de grille, l'application la plus pertinente de la méthode proposée est la surveillance en cours de fonctionnement. Pendant le fonctionnement normal, le composant testé est commandé en utilisant une loi de commande propre à chaque application. On distinguera dans cette étude le fonctionnement en mode hacheur et en mode onduleur. En considérant l'hypothèse d'un comportement résistif de la jonction grille-source  $R_{\rm GS}$  au cours du vieillissement, le courant de fuite moyen théorique peut s'exprimer comme suit :

$$I_{L,TH} = \frac{1}{R_{GS}} \left( \alpha(t) \cdot V_{DD} + V_{GS,OFF} \right)$$

(6)

Où  $\alpha(t)$  est le rapport cyclique instantané du signal de tension grille-source  $V_{GS}$  et  $V_{DD}$  est la tension d'alimentation (ici  $V_{DD}$  = 25V).

Par conséquent, on remarque que pour  $\alpha$ =20% les courants de fuite se compensent sur une période de découpage donnée et le potentiel  $V_S$  reste stable à 5V. Pour toute autre valeur, une variation positive ou négative peut être observée sur le potentiel de source. Le rapport cyclique et donc la loi de commande appliquée ont donc une incidence sur le système d'estimation du courant de fuite de grille. Toutefois, dans le cas d'une application onduleur, le rapport cyclique est défini par :

$$\alpha(t) = \frac{1 + \text{m·cos}(2\pi f t)}{2} \tag{7}$$

Où m est le taux de modulation et f la fréquence du signal modulant.

Dans ce cas, le rapport cyclique moyen est de 50% et le courant de fuite théorique s'exprime comme une constante puisque  $T_L >> T$ .

$$I_{L,TH} = \frac{V_{GS,ON} + V_{GS,OFF}}{2 \cdot R_{GS}} = \frac{15}{2 \cdot R_{GS}}$$

(8)

La méthode proposée permet donc une caractérisation horsligne ou en cours de fonctionnement pour une application onduleur. Dans le cas d'un fonctionnement en mode hacheur, la valeur du rapport cyclique doit être prise en compte dans le calcul, ce qui rend la méthode proposée moins attractive. La méthode proposée est donc particulièrement adaptée au fonctionnement en mode onduleur mais la principale contrainte est la nécessité d'une calibration en courant à l'état « neuf ». En pratique, cette calibration devra être effectuée lors de la première mise en service du convertisseur d'énergie et servira de référence pour toute la durée de vie du composant testé.

# 3. MISE EN OEUVRE

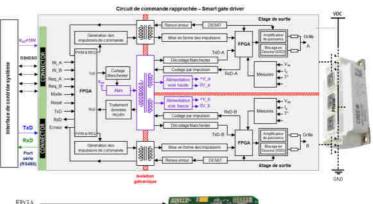

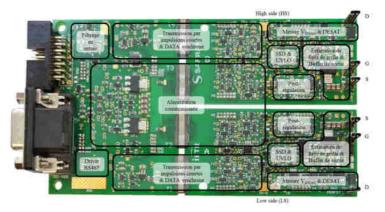

Cette méthode de mesure a été implantée lors du design d'un Smart Gate Driver intégrant de nombreuses autres fonctions. La figure 4 montre à la fois la zone d'implémentation du système de mesure de la fuite de grille mais également les canaux de communication assurant l'échange de nombreuses données entre le primaire et les secondaires du gate driver.

Fig. 5. Smart Gate Driver assurant le pilotage et le monitoring de composants MOSFET SiC (Top view et Bottom view).

#### 4. RÉSULTATS

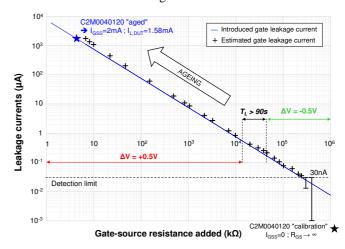

Des essais ont été menés pour valider la méthode proposée. Dans un premier temps, une résistance a été ajoutée entre la grille et la source pour simuler un courant de fuite de grille sur le composant testé. Pour ces premiers essais, le composant testé est un composant MOSFET SiC discret C2M0040120. Un composant « veilli » (même référence) a ensuite été soumis au processus d'estimation de manière à pouvoir valider l'hypothèse d'un comportement globalement résistif de la jonction grillesource lors du vieillissement du composant. Enfin, des essais en environnement de puissance ont été menés sur un module de puissance SiC 1.2kV. Une discussion sur l'influence de la température sur les courants de fuite a également été initiée.

Emulation du courant de fuite de grille par ajout d'une résistance grille-source

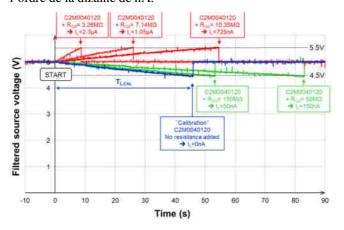

La mesure en fonctionnement a été testée avec un signal de commande modulé correspondant à une application onduleur (tel que défini dans l'équation 7). Un signal MLI de  $100 \mathrm{kHz}$  a été utilisé pour commander le composant. Le signal modulant est un signal sinusoïdal de fréquence  $1 \mathrm{kHz}$ . Le courant dans la charge est sinusoïdal car le signal  $V_{GS}$  appliqué correspond à une application onduleur. La meilleure précision est obtenue lorsque  $T_{SINUS} << T_L$  où  $T_{SINUS}$  est la période du signal modulant.  $T_L$  est typiquement de l'ordre de la seconde mais il peut être inférieur

à 1s lorsqu'un courant de fuite excessif est détecté ( $I_{L,MES} > 10 \mu A$ ).

$C_l$  et  $C_2$  sont composées chacun de 4 condensateurs de  $4.7\mu F$  ce qui équivaut à  $C_1+C_2=37.6\mu F$  (±10%). Cependant, la valeur de capacité dépend de la qualité des condensateurs, de la température et de la tension appliquée (derating), la valeur nominale est donc utilisée comme une approximation dans le processus d'estimation. C'est pourquoi on parlera d'une méthode d'estimation plutôt que d'une méthode de mesure précise.

La plage de variation autorisée du potentiel de source est de  $\Delta V_S = \pm 0.5 V$  pour garantir une tension  $V_{GS}$  entre -5.5V et +20.5V dans le pire des cas. La tension de seuil doit être choisie en tenant compte des performances souhaitées du circuit d'estimation et des conditions de sécurité pour le signal  $V_{GS}$ .

Une calibration a été effectuée sur un composant MOSFET SiC 1.2kV « neuf » (C2M0040120). Puisque le paramètre I<sub>GSS</sub> d'un composant « neuf » est typiquement de quelques fA ou pA, la variation du potentiel de source durant la calibration est entièrement due aux fuites du circuit de commande rapprochée  $I_{L,DRIVER}$ . Comme le montre la figure 6, le potentiel de source diminue pendant  $T_{L,CAL} = 45.5s$ , ce qui correspond à un courant de  $I_{L,DRIVER} = -413nA$ . Une vingtaine de calibrations ont été réalisées pour vérifier la reproductibilité de la mesure : 43s <  $T_{L,CAL}$  < 46.2s. Ces essais correspondent à un courant de fuite lié au système entre -437nA et -407nA. On peut donc estimer une précision maximale de la méthode proposée de l'ordre de 30nA à faible courant. La valeur obtenue à la calibration  $I_{L,DRIVER}$ est différente d'un circuit à l'autre en fonction des courants parasites des composants utilisés. Une calibration à l'état « neuf » est donc nécessaire pour atteindre une précision de l'ordre de la dizaine de nA.

Fig. 6. Résultats d'essais avec émulation du courant de fuite par ajout de résistances grille-source

Les résultats obtenus montrent une excellente capacité à estimer l'évolution du courant de fuite de grille pour des valeurs allant de 30 nA à quelques mA (figure 7). Ces résultats sont obtenus lors du fonctionnement dans une cellule de commutation avec les caractéristiques suivantes :

Vdc = 540~V~/~I = 92~A~/~freq.~découpage = 100~kHz~/~freq.~fondamental = 400~Hz~/~charge~47~kVAR

Fig. 7. Estimation du courant de fuite de grille durant un fonctionnement en mode onduleur 540V / 92A.

#### 5. CONCLUSIONS

Ce papier présente une méthode novatrice permettant d'estimer l'évolution du courant de fuite de grille dans un MOSFET SiC durant son fonctionnement au sein d'un convertisseur. Cette méthode a été mise en œuvre dans un Gate Driver et montre la possibilité d'estimer des courants allant de 30 nA à 2mA.

# 6. References

- T. A. Nguyen, S. Lefebvre and S. Azzopardi, "Effect of short circuit aging on safe operating area of SiC MOSFET", *Microelectronics Reliability*, vol. 88-90, DOI 10.1016/j.microrel.2018.06.040, pp. 645–651, Sept. 2018.

- [2] R. Ouaida et al., "Gate Oxide Degradation of SiC MOSFET in Switching Conditions", IEEE Electron device letters, vol. 35, DOI 10.11.09/LED.2014.2361674, pp. 1284-1286, Dec. 2014.

- [3] F. Erturk, E. Ugur, J. Olson and B. Akin, "Real-Time Ageing Detection of SiC MOSFETs", *IEEE Transactions on Industry Applications*, DOI 10.1109/TIA.2018.2867820, Aug. 2018.

- [4] F. Erturk, B. Akin, "A method for online ageing detection in SiC MOSFETs", *IEEE Applied Power Electronics Conference and Exposition* (APEC), DOI 10.1109/APEC.2017.7931211, pp. 3576–3581, Mar. 2017.

٠