## Modélisation électrothermique compacte des modes de défaillance du Mosfet SiC en régime extrême de

# **COURT-CIRCUIT.** Application au développement d'une protection intégrée pour convertisseur sécurisé à tolérance de panne

François Boige<sup>(1)</sup>, Frédéric Richardeau<sup>(1)</sup>, Stéphane Lefebvre<sup>(2)</sup>

(1) LAPLACE, Université de Toulouse, CNRS – (2) SATIE, Cnam, ENS Paris Saclay, CNRS

RESUME - Le Mosfet SiC de puissance présente des propriétés singulières en régime de court-circuit (CC) telles qu'un courant de fuite de grille important, un fort courant de saturation et deux modes de défaut complémentaires dont l'un est sécurisant (fail-to-open) sous certaines conditions. Ce papier présente un modèle électro-thermique compact original représentatif des singularités du composant. Une analyse technologique poussée de la défaillance a permis de modéliser et de comprendre ses modes de défaut. Enfin, un nouveau circuit de protection contre les court-circuits utilisant le courant de fuite de grille comme indicateur observable est présenté et validé.

Mots-clés—Mosfet SiC, régime extrême, court-circuit, modes de défaillance, modélisation compacte, driver, protection.

#### 1. Introduction

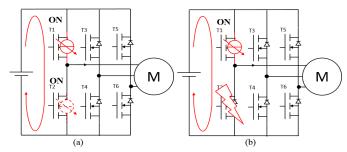

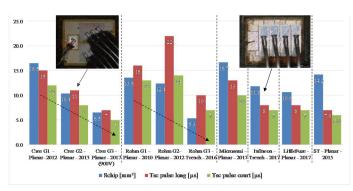

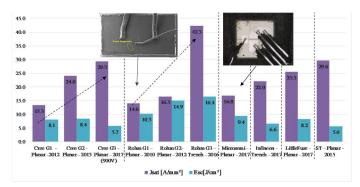

Le MOSFET au carbure de silicium (SiC) devient aujourd'hui incontournable dans la plage de tension 400V-900V. L'un des principaux obstacles à la diffusion de ce composant dans les applications industrielles critiques est sa fiabilité limitée et surtout sa faible robustesse en court-circuit (CC) [1], en particulier sur des cycles répétés de court-circuits internes dans un onduleur comme illustré en Fig. 1 sur deux configurations types [2]. Alors que l'IGBT est couramment spécifié pour une tenue au court-circuit (Tsc) au moins égale à 10µs sur au moins 1000 cycles, le Mosfet SiC peut vieillir très rapidement en quelques dizaines de cycles de quelques microsondes seulement. A cet effet, l'histogramme de la Fig. 2 illustre l'évolution de la tenue au court-circuit des générations successives de Mosfet SiC issus des caractérisations [2]. On constate une baisse nette du niveau de robustesse avec un T<sub>sc</sub> en dessous de la barre des 10µs de référence pour la plupart des composants commerciaux du moment. Cet affaiblissement de la robustesse est, en grande partie, la conséquence d'une réduction de la surface des puces conduisant à une augmentation très nette de la densité de courant de saturation lors du court-circuit, comme le montre le graphique de la Fig. 3 [3]. En effet, les fabricants cherchent toujours à optimiser les coûts en produisant le maximum de puces à surface de wafer

donnée. Cette densité de courant est directement impliquée dans la vitesse à laquelle la température s'installe dans la puce. Bien que très simplifiée et macroscopique, la relation (1) rappelle la solution bien connue de l'équation de la chaleur en assimilant la puce à un milieu homogène 2D adiabatique, dont le terme source est lui-même réduit à un échelon de densité de puissance localisé sur la surface de la puce. A mode de défaillance donné, i.e. à élévation de température maximale autorisée, s'en déduit la valeur approchée du  $T_{\rm sc}$  de la puce.

Fig. 1 Les deux configurations classiques de mise en court-circuit sur défaut interne d'un onduleur [2].

Fig. 2 Comparaison des surfaces de puce, temps de tenue en court-circuit ( $T_{sc}$ ) en pulse long et en pulse court @  $V_{ds} = 600V$  (excepté pour le composant Cree G3  $V_{ds} = 450V$ ) [3][4].

Fig. 3 Comparaison de la densité de courant de saturation maximale et de la densité d'énergie maximale @ $V_{ds} = 600V$  (excepté pour le composant Cree G3  $V_{ds} = 450V$ ) [3][4].

Cette relation (1), a vertu pédagogique, montre bien l'importance des paramètres électriques  $J_{sat}$  et  $V_{ds}$ : les composants Mosfet SiC de calibre haute tension devront voir leur densité de courant atténuée afin de tenir une valeur  $T_{sc}$  suffisante permettant de les protéger, aux dépens d'une plus forte résistance spécifique à l'état passant. Compte tenu du niveau de température intense mise en jeu dans la puce durant le court-circuit, cette relation est rapidement inapplicable sur le plan quantitatif car elle ne prend pas en compte la dépendance en température de la densité de courant (à travers la mobilité électronique dans le canal) et des paramètres du matériau, en particulier celle de la conductivité thermique. Une modélisation plus fine requiert une simulation physique électrothermique couplée de la puce en court-circuit [5].

$$\Delta T_j(t)_{2D \ adiabatique} = 2. V_{ds} J_{sat} \sqrt{\frac{t}{\pi \rho \lambda C_p}}$$

(1)

$\rho$ ,  $\lambda$  et  $C_p$  représentent respectivement la densité, la conductivité thermique et la chaleur massique du SiC.

L'objet de cet l'article de synthèse est de proposer une démarche de modélisation plus poussée du Mosfet SiC permettant d'appréhender ses propriétés singulières principales en régime extrême de court-circuit. Ainsi, dans la deuxième partie, une modélisation physique électro-thermique couplée est décrite, permettant de mieux caractériser les deux modes de défaillance en jeu au sein du Mosfet SiC. Ces modes sont ensuite agrégés dans un modèle électrique équivalent dit *compact*, sous forme d'éléments de circuit, pour des besoins de simulation *système*. Enfin, la dernière partie de l'article propose la conception et la vérification d'une protection hardware originale, intégrée dans un driver de commande rapprochée, tirant parti de la fuite de grille dynamique propre au Mosfet SiC.

## 2. SIMULATION ELECTRO-THERMIQUE ET MODES DE DEFAILLANCE DU MOSFET SIC – CAS D'ETUDE

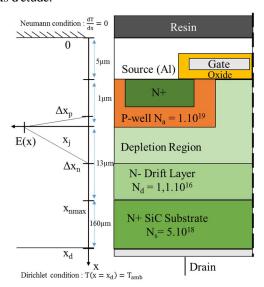

Au-delà des besoins applicatifs d'une robustesse renforcée, l'étude du court-circuit d'un transistor de puissance est une démarche intéressante pour révéler ses caractéristiques en dehors de la SOA. Les connaissances obtenues permettront de mieux protéger le composant en termes de densité d'énergie appliquée et de répétitivité de cycles. L'estimation de la température durant ce régime est tout aussi essentielle pour identifier sur quelles régions de la puce prennent naissance les mécanismes de dégradation, qu'ils soient réversibles ou pas. A cet effet, un modèle physique monodimensionnel a été développé sur la base d'une structure de référence Mosfet SiC à grille planar. La Fig. 4 illustre le principe de la modélisation tel

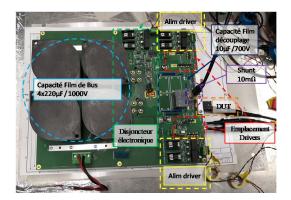

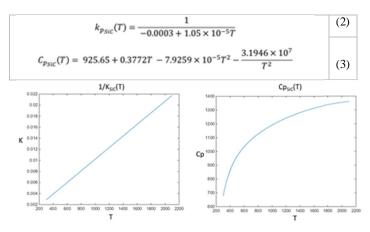

que détaillé par les auteurs dans [6]. La distribution géométrique  $E_x$  du champ électrique est tout d'abord calculée à partir du théorème de Gauss, du dopage de la fine couche d'épitaxie, du puits p+ constituant la jonction bloquante et de la tension aux bornes imposée par la source lors du court-circuit. Cette distribution est ensuite multipliée par la densité de courant temporelle  $J_x(t)$  issue d'un banc de test de court-circuit dont une photo est donnée en Fig. 5 [2]. Ce banc permet de reproduire en toute sécurité les configurations réelles de défauts telles qu'illustrées dans l'introduction de l'article en Fig. 1. La densité de puissance est alors déduite par la relation  $P_{\nu}(x, t) =$  $E_x$ .  $J_x(t)$ . La résolution de l'équation de la chaleur permet ensuite de simuler le régime transitoire thermique de la puce en considérant qu'elle est isolée sur sa face supérieure et que sa face arrière est assimilable à un puits de chaleur. L'usage d'un substrat SiC permet au composant de supporter une élévation de température transitoire bien supérieure à celle connue en silicium, typiquement bien au-delà de 700K. Cette large plage thermique ne permet pas de négliger la dépendance en température de la conductivité thermique et de chaleur massique du substrat. Les relations usuelles issues de [7] sont rappelées en (1) et (2). On pourra constater, sur l'intervalle [300K, 800K], que la conductivité décroit de 200% alors que la chaleur massique n'augmente que de 60%. La puce s'autoéchauffe donc plus fortement à haute température et une résolution spatio-temporelle non-linéaire est indispensable pour trouver la solution. Celle-ci sera obtenue par Comsol<sup>TM</sup> dans notre cas d'étude.

Fig. 4 Modèle monodimensionnel distribué du Mosfet SiC à grille planar pour la simulation de la température de la puce en court-circuit.

Fig. 5 Banc de test développé durant la thèse [2], équipé d'un disjoncteur électronique sur lequel différents composants Mosfet SiC et gate driver peuvent être implantés.

Fig. 6 Loi de variation en température de la conductivité thermique et de la chaleur massique du SiC [7].

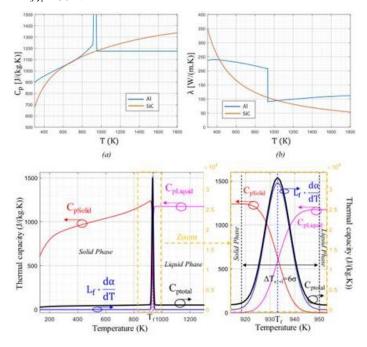

En régime extrême de court-circuit, la température de la puce SiC peut largement dépasser la température de fusion de la couche d'Aluminium sur les électrodes de source et de grille. Cette caractéristique est là aussi une différence importante par rapport au cas du silicium. Il en découle qu'une modélisation de la transition de phase solide-liquide de la couche d'aluminium est nécessaire. Celle-ci est décrite, sous Comsol<sup>TM</sup>, par une fonction de transition d'état suivant une loi normale cumulée comme le précise la relation (4) [8] et les représentations graphiques de la Fig. 7. Dans cette transition, L<sub>f</sub> représente la chaleur de fusion du métal, assimilable à un puits de chaleur transitoire qui va freiner temporairement l'élévation de température de la puce au voisinage de la température de fusion. L'écart type  $\sigma$  est réglé pour assurer la convergence du solveur, dans le cas présent  $\sigma = 5K$  donnant  $\Delta T_{s \to 1} = 6\sigma$ , soit  $\Delta T_{s\rightarrow l} = 30K$ .

Fig. 7 Modélisation de la transition de phase solide-liquide de la couche d'aluminium du Mosfet SiC au niveau des paramètres de conductivité et de chaleur massique [8].

$$C_p = C_{pS}(T) \cdot (1 - \alpha(T)) + C_{pL} \cdot \alpha(T) + L_f \cdot \frac{d\alpha}{dT}$$

(4)

Où  $C_{pS}$ ,  $C_{pL}$  et  $L_f$  représentent respectivement la chaleur massique solide, liquide de l'aluminium dont la chaleur de fusion est notée  $L_f$  de valeur 397kJ/kg [X7].

La démarche de modélisation précédente est ensuite appliquée au cas d'étude de la Fig. 8 où un enregistrement de court-circuit est réalisé sur le banc de la Fig. 5.

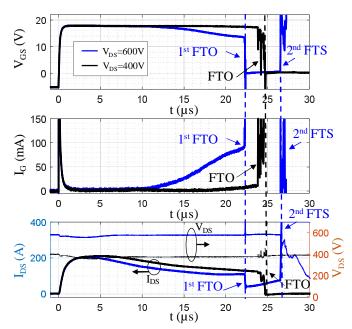

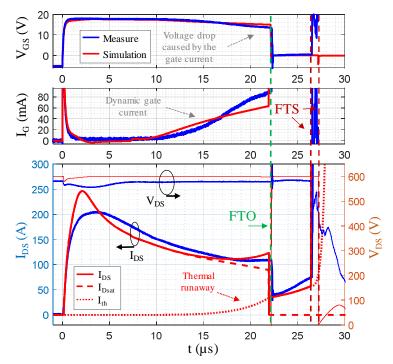

Fig. 8 Formes d'ondes expérimentales d'un Mosfet SiC 1,2kV  $-80m\Omega$  à grille planar en court-circuit sous  $V_{buffer(on/off)}=18V/-5V,\,R_{Gate}$   $_{Ext.}\!\!=\!\!47\Omega,\,T_{jnit}\!=\!25^{\circ}C$ : courbes en noir  $V_{DS}=400V,$  courbes en bleu  $V_{DS}=600V.$  Cas d'un pulse de court-circuit dit "long" sans blocage par la commande.

Ce cas d'étude présente l'intérêt d'illustrer les deux modes de défaillance intrinsèques présents de manière concurrentielle dans ce type de composant. Le premier, représenté par les courbes en noir, est généralement obtenu sous tension de drain réduite, i.e. dans des conditions de densité de puissance atténuées. Après une phase de saturation du courant, on observe un effondrement de la tension grille – source tel un court-circuit forçant ainsi le courant de canal à s'annuler tout en conservant une tenue en tension entre drain et source. Ce premier mode est nommé Fail-To-Open (FTO mode) et s'apparente à un effet disjoncteur qui peut être très recherché pour sécuriser naturellement une application en situation ultime de dernier-secours. Le second mode, représenté par les courbes en bleu, est réalisé sous la pleine tension nominale et donc à pleine densité de puissance. Raison pour laquelle le FTO apparait plus tôt que dans le premier cas : 22,5µs contre 24µs. Cependant, l'ouverture du canal ne permet pas d'annuler totalement le courant total absorbé par le drain : une forte composante de fuite subsiste. Celle-ci maintient l'autoéchauffement du composant jusqu'à son emballement thermique. Le FTO est donc suivi d'une destruction de la puce, entre drain - source, seulement 4,5µs après l'ouverture du canal. Ce mode s'apparente à un court-circuit, il s'agit donc d'un défaut critique redouté, désigné dans la suite par Fail-To-Short ou FTS mode. Il existe bien sûr des cas moins nets que le FTO, par exemple sur cycles répétés, à faible densité de puissance, où la puce vieillit et se dégrade sans être défaillante, avec une tension de grille affaiblie mais de valeur supérieure à la tension de seuil V<sub>gsth</sub>, amenant ainsi le canal à rester actif et à la puce de rester fonctionnelle [9]. La fuite de grille est aussi bien visible dans les deux cas d'étude de la Fig. 8. Elle présente une forte dynamique, environ à partir de T<sub>fail</sub>/2 et une forte amplitude, de l'ordre de  $10mA/\mu s$  sous 600V, alors même que le composant n'est pas encore défaillant. Raison pour laquelle la tension de grille subit une chute ohmique bien nette, de plusieurs volts, à travers la résistance de grille externe. Cette fuite est analysée physiquement dans [10], comme une injection d'électrons chauds par effet d'émission Schottky, entre la grille en poly-silicium et le substrat SiC à travers l'oxyde de grille. Ce courant servira de base de détection pour la mise en place d'un nouveau principe de protection au §5. A champ électrique donné, cette fuite est aussi une image physique interne de la montée en température de la puce.

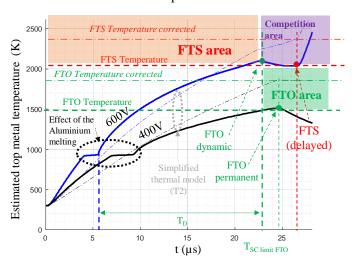

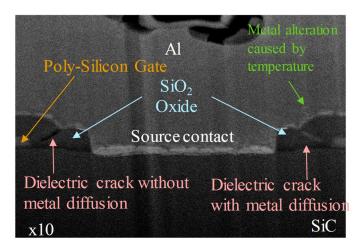

Une simulation électrothermique monodimensionnelle de la puce est ensuite réalisée dans les deux cas de polarisation en tension  $V_{DS} = 400V$  puis  $V_{DS} = 600V$ . La Fig. 9 en donne les dynamiques thermiques correspondantes. On notera clairement le régime d'état solide de la couche d'aluminium ( $T_{\text{top}} < 933 K$  - $3\sigma$ ), le régime d'état liquide de cette couche ( $T_{top} > 933K + 3\sigma$ ) et le régime de puits de chaleur permettant la transition métallurgique complète solide - liquide. Sous tensions réduites, des essais successifs ont permis d'identifier les frontières d'entrée de la zone de défaillance dite FTO, matérialisée en vert sur la figure :  $\Delta T_{sc}>23\mu s,~T_{top}>1500K.$  Quelques articles se sont attachés à comprendre l'origine du FTO, en particulier. L'hypothèse la plus probable est la fissuration de l'oxyde épais entre la grille et la source du composant lors de la montée en température, suivie de la diffusion du métal jusqu'à la mise en court-circuit de la grille [11][12]. Un délai suffisant d'infiltration est nécessaire à une température suffisante pour permettre au métal de traverser l'oxyde épais jusqu'à un doigt de grille. Une microsection de la puce dans la région d'oxyde suivie d'un MEB a ainsi été faite pour apporter des éléments de preuve, bien que d'autres hypothèses soient en cours d'investigation à ce jour. La photo Fig. 10 montre effectivement des traces endommagement de l'oxyde dans les coins avec le métal et pour certaines fissures une suspicion d'infiltration de métal. La Fig. 9 montre aussi la trajectoire thermique sous tension nominale. Là aussi, de nombreux essais ont permis d'identifier la frontière d'entrée du mode FTS correspondant à un seuil estimé ici à 2000K. Le cas de la polarisation à 600V est intéressant à étudier : la trajectoire thermique traverse transitoirement la frontière FTS pour ensuite atteindre aussi la frontière FTO. Les deux modes sont en compétition avec d'un côté une fuite de drain et de l'autre un canal ouvert. La fuite élevée se développe principalement dans une zone de déplétion en parallèle avec le canal ce qui signifie que cette fuite ne peut pas être contrôlée (du moins au premier ordre) par l'ouverture du canal et l'emballement finit par déclencher le mode FTS.

Fig. 9 Trajectoires thermiques et identification des zones de défaillance du Mosfet SiC en pulse long , sous tension nominale  $V_{DS}=600V$  et sous tension réduite  $V_{DS}=400V\,$  pour  $V_{buffer}=18V,\,T_{jinit}=25^{\circ}C.$

Fig. 10 Image MEB de la zone de grille (oxyde épais) endommagée lors d'un court-circuit et donnant lieu à un mode FTO.

L'analyse thermique transitoire est précieuse pour guider la compréhension des limites d'usage du composant. Afin d'assurer une connexion vers le modèle compact "circuit" présenté en §3, les trajectoires thermiques sont modélisées par une simple ligne de *Cauer* à 20 éléments. Celles-ci sont illustrées en Fig. 9 par des lignes en pointillées. Les paramètres  $R_{thi}$  et  $C_{thi}$  de la ligne équivalente sont obtenus selon un critère de minimisation d'erreur par la méthode des moindres carrés sous Matlab<sup>TM</sup>. Nous avons veillé à rendre robuste la solution par une succession de conditions initiales issues d'un tirage aléatoire sur un large intervalle de valeurs éligibles afin de se rapprocher d'un optimum global.

## 3. MODELE ELECTRO-THERMIQUE COMPACT DU MOSFET SIC INCLUANT SES MODES DE DEFAILLANCE

Le modèle précédent a permis une analyse thermique de la puce en régime de court-circuit partant d'un stimulus expérimental. Nous en avons déduit une ligne thermique équivalente. Dans cette section nous allons présenter une synthèse des résultats portant sur le modèle électrique du Mosfet SiC doté de paramètres thermo-sensibles couplés à la ligne thermique précitée. Ce modèle présente l'originalité de modéliser la fuite de grille, la fuite de drain ainsi que ses deux modes de défaillance [13], tout en étant compatible avec un environnement de simulation circuit de type LT/PSpice<sup>TM</sup> ou PLECS/PSIM<sup>TM</sup> pour les plus connus en électronique de puissance, à des fins de simulation *système*.

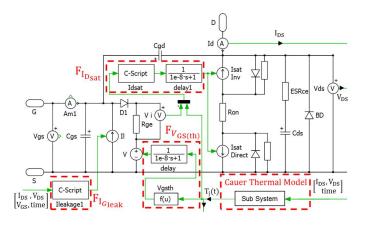

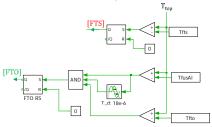

Un premier niveau de modélisation est représenté en Fig. 11. Son cœur est constitué d'un modèle simplifié de Mosfet autour duquel sont rajoutés des fonctions de dépendance à la température ou à l'énergie thermique accumulée durant le court-circuit.

Ainsi, le premier bloc  $FI_{Gleak}$  est dédié à la modélisation comportementale de la fuite de grille sous la forme d'une résistance non linéaire dépendante de l'énergie thermique accumulée. Elle sera modélisée par un dipôle source de courant piloté en tension de grille comme le décrit la relation (5). Les coefficients de cette loi sont fittés sous Matlab<sup>TM</sup> par optimisation, sur la plage  $V_{GS} \in [18V, 21.5V]$  @  $V_{DS} = 600V$ .

Fig. 11. Modèle électro-thermique compact du Mosfet SiC pour des besoins de représentation en mode de court-circuit :  $FI_{Gleak}$ ,  $FV_{GSth}$ ,  $FI_{Dsat}$  représentent respectivement les fonctions de comportement  $I_{Gleak}(T_j)$ ,  $V_{GSth}(T_j)$  and  $I_{Dsat}(T_j)$ .

$$I_{Gleak} = (p_{01} + p_{11}E_n + p_{21}E_n^2) \cdot V_{GS} + p_{00} + p_{10}E_n + p_{20}E_n^2 + p_{30}E_n^3$$

(5)

Avec :  $p_{01} = 9.51$ ,  $p_{11} = 9.44$ ,  $p_{21} = 2.512$ ,  $p_{00} = -156.08$ ,  $p_{10} = -150.35$ ,  $p_{20} = -36.05$ ,  $p_{30} = 0.628$ .

Les deuxième et troisième blocs, respectivement  $FI_{Dsat}$  et  $FV_{GSth}$ , rendent compte de la dépendance à la température du courant de saturation et de la tension de seuil. Ces deux modèles sont décrits en relations (6) et (7) sous la forme d'une loi de mobilité bien connue de type Matheissen et par un modèle linéaire pour la tension de seuil. Une modélisation plus poussée de type exponentielle peut aussi être envisagée comme décrite dans [14].

$$I_{Dsat}(T_j) = \frac{\mu_n(T_j) \cdot C_{OX} \cdot Z}{2L} \cdot (V_{gs} - V_{gs(th)}(T_j))^2 \quad (6)$$

$$\mu_{n}(T_{j}) = \frac{\mu_{a0}\left(\frac{T_{j}}{T_{0}}\right)^{a}}{1 + \frac{\mu_{a0}}{\mu_{b0}}\left(\frac{T_{j}}{T_{0}}\right)^{b-a} + \frac{\mu_{a0}}{\mu_{a0}}\left(\frac{T_{j}}{T_{0}}\right)^{c-a}}$$

(7)

$$V_{GS(th)}(T_i) = x_1 \cdot T_i + x_2$$

(8)

Où :  $\mu_{a0}$ ,  $\mu_{b0}$ ,  $\mu_{c0}$  sont les paramètres de base à 300K et a, b and c sont des coefficients de sensibilité thermiques fittés sur des résultats expérimentaux afin de caler le modèle : en unité [cm².V¹.s⁻¹],  $\mu_{a0} = 2.33$ ,  $\mu_{b0} = 2.95$ ,  $\mu_{c0} = 1.94.10³$  et : a = -1.48, b = -4.8, c = 2.56. Dans les mêmes conditions et sur la plage  $V_{GS} \in [18V, 21.5V]$  @  $V_{DS} = 600V$  :  $x_1$  et  $x_2$  ont été fittés:  $x_1 = -0.025$  V/K,  $x_2 = 15.4V$ .

La Fig. 12 donne un exemple de comparaison du modèle ainsi fitté par rapport aux données expérimentales pour  $V_{GS}=18V$  et  $V_{GS}=21V$ . Le modèle reproduit correctement le comportement global excepté en début de transitoire de courant de saturation. Ce même modèle a aussi été évalué positivement sur des stimuli différents de ceux ayant servi à fitter le modèle afin d'en connaitre la robustesse [6]. La même démarche a aussi été appliquée avec succès sur deux technologies différentes de Mosfet SiC à grille planar.

Fig. 12 Vérification du recalage du modèle électro-thermique de référence, en régime de court-circuit @  $V_{DS}=600V$ ,  $T_{jinit}=25^{\circ}C$  and  $R_{Gate\ Ext.}=47\Omega$ .

## 4. Modelisation des modes de Defaut – Modele compact complet

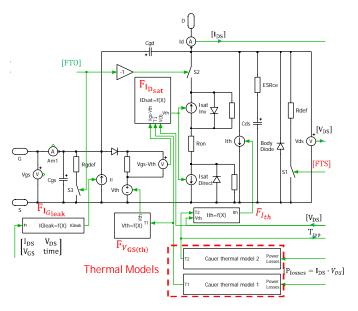

Le modèle proposé dans cette section est affiché en Fig. 13. Il constitue une extension du modèle précédent. En premier lieu, le cœur du modèle est amélioré en dissociant la partie dédiée à la contrôlabilité du canal de la diode body. Ainsi une structure de contrôle du canal "miroir" est introduite permettant de dissocier la conduction du canal et de la diode body dans le 3ème quadrant de conduction, i.e. en inverse. Le modèle thermique de Cauer introduit dans le premier modèle en Fig. 11 est conservé car il pilote directement les paramètres électriques de premier niveau que sont la mobilité dans le canal et la tension de seuil. Le recalage de ces grandeurs ayant été vérifié en §3. Ce modèle est désigné par "modèle 1" en Fig. 13. Un second modèle thermique est introduit comme décrit en §2, lequel prend en compte cette fois la sensibilité thermiques du substrat SiC et la chaleur latente de transition de phase solide liquide de la couche d'aluminium. Ce modèle est désigné par "modèle 2" en Fig. 13. Le courant de fuite de drain est ensuite modélisé par une loi de génération thermique de type Shockley-Read-Hall (SRH) décrite en relation (8) [15], [16]. Il a été montré dans [3], sur ce type de structure de Mosfet SiC et dans ces conditions d'utilisation extrême, que la fuite par génération thermique était dominante par rapport aux autres composantes par diffusion et par avalanche. Cette fuite de drain est à l'origine de l'emballement thermique de la puce et du passage en mode destructif FTS. C'est en réalité un phénomène local et inhomogène sur la puce donc complexe à décrire, qui est ici simplifié car ramené à une échelle globale. Le phénomène décrit reste représentatif globalement du comportement en limite d'usage. Dans ce modèle de fuite de drain,  $W_D$  est la profondeur de déplétion de la jonction bloquée deep-p+ / n- drift en régime de saturation, comme définie en relation (9), n<sub>i</sub> est la densité intrinsèque de porteurs de charges décrite en relation (10) en fonction de la température du cristal [17].

$$I_{th}(T) = \frac{qW_D n_i(T)}{\tau_q} S$$

(8)

$$W_D = \sqrt{\frac{2\epsilon_s}{q} \cdot \frac{N_d + N_a}{N_d N_a} \cdot V_{DS}} \tag{9}$$

$$n_{iSiC}(T) = 1.7 \cdot 10^{16} \cdot T^{\frac{3}{2}} \cdot e^{-\frac{2.08 \cdot 10^4}{T}}$$

(10)

Avec :  $\tau_g$ , la durée de vie des porteurs générés par SRH compris entre [1ns, 1 $\mu$ s] issue de [18][19]. Ce paramètre a été fitté à 1ns pour reproduire le comportement FTS de notre composant sur la plage  $V_{DS} \in [400V, 600V]$  et assurer la convergence du modèle complet. Celui-ci est évalué dans la section suivante.

Fig 13 Modèle compact complet, de type circuit, permettant de représenter le comportement électrothermique du Mosfet SiC et ses modes de défaillance FTO – FTS en régime de court-circuit.

Fig 14. Blocs de comparaison pour l'activation des modes de défaillance FTO et FTS par la température simulée sur la ligne de Cauer  $n^\circ 2: T_{fiscorrected} = 2400 K$ ,  $T_{fusAl} = 933 K$ ,  $T_{fio \, corrected} = 1900 K$ .

Dans ce modèle, les interrupteurs S3 pour  $R_{\text{gdef}}\left(0.1\Omega\right)$  et S1 pour R<sub>def</sub> (5mΩ) permettent de modéliser l'activation des modes de défaillance FTO et FTS lorsque les conditions thermiques sont atteintes durant le court-circuit. Pour réaliser cette opération, la ligne thermique de Cauer n°2 est utilisée dans le modèle compact. La sortie de cette ligne est comparée à un ensemble de comparateurs tels que schématisés en Fig. 14. Le FTO sera atteint lorsque la température estimée sera à la fois supérieure à la température de fusion de la couche d'aluminium T<sub>fuseAl</sub> pendant une durée T<sub>D</sub> et supérieure à la température de frontière du mode FTO, T<sub>FTO corrigée</sub>. Lorsque ces trois conditions sont remplies, l'interrupteur S3 placé en parallèle avec la grille vient forcer le blocage du canal et provoquer le FTO. Le FTS est gouverné par un seul seuil T<sub>FTS corrigé</sub> associé à l'interrupteur S1 placé en parallèle entre les électrodes drain et source pour forçant ainsi le mode destructif

du composant. Partant de la trajectoire thermique de la Fig. 9 sur la ligne de *Cauer* n°2, les seuils et délais "équivalents" suivants sont retenus pour modéliser globalement le comportement de notre composant :  $T_{\rm fuseAl} = 933 \, \text{K}$ ,  $T_D = 18 \, \mu \text{s}$ ,  $T_{FTO \; corrigé} = 1900 \, \text{K}$  et  $T_{FTS \; corrigé} = 2400 \, \text{K}$ .

Fig. 15 Comparaison entre le modèle proposé (courbes en rouge) et les formes d'ondes expérimentales issues du banc de la Fig. 1 (courbes en bleu) : modes FTO et FTS obtenus à VDS = 600V @Tjnit =  $25^{\circ}$ C, Vbuffer (on/off) = +18V/-5V et RG =  $47\Omega$ .

L'évaluation du modèle compact complet est donnée en Fig. 15 lorsque le composant est polarisé sous la pleine tension de 600V. Sur ce point de polarisation, l'expérience a révélé un enchaînement des deux modes FTO et FTS propre au Mosfet SiC. Ce comportement est parfaitement reproduit en Fig. 15 sur les variables internes  $i_{GS}(t)$ ,  $v_{GS}(t)$  et  $i_{DS}(t)$ , où les fuites de grille et de drain sont bien visibles et cohérentes par rapport à la mesure sauf sur les transitoires rapides. Par ce modèle, nous vérifions l'apparition du FTO après 24 µs. Cependant, en présence d'un court-circuit sur un pulse long, la forte montée en température de la puce sous la pleine tension provoque une fuite de drain importante qui est bien visible juste après le blocage du canal (composante Ith(t) en pointillé). Celle-ci ne permet pas à la puce de se refroidir et l'emballement thermique devient inévitable jusqu'au FTS après 26µs alors même que le FTO était bien présent au niveau de la région de grille.

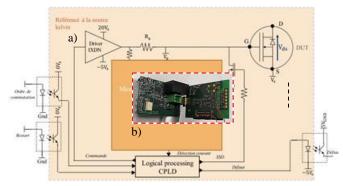

### 5. Driver de Protection

Le courant de fuite dynamique de grille présenté en Fig. 2. lors d'un fonctionnement en court-circuit apparait environ à la moitié du temps avant la défaillance du composant (soit T<sub>sc</sub>/2) pour la plupart des références caractérisées [3]. Cette fuite présente une dynamique temporelle importante de l'ordre de la dizaine de mA/µs pour des puces de 80mOhm, ce qui rend sa détection voire sa mesure possible avec un rapport signal à bruit satisfaisant, y compris au moyen d'une technologie non intégrée de type CMS. Cette propriété disparait évidemment dans des conditions particulières d'usage à tension de grille réduite, où le faible champ électrique développé à travers l'oxyde mince ne permet pas d'activer pleinement l'effet d'émission Schottky entre le substrat SiC et la grille polysilicium [10]. Si la fuite de grille est seuillée et détectée dès le

début de son emballement, le composant pourra être bloqué et sauvé.

Un nouveau circuit de protection dédié a ainsi été développé selon cette idée. Le schéma de principe simplifié et la réalisation sont présentés en Fig. 16. La détection du courant de grille se fait au moyen de la résistance de grille nominale du composant qui joue le rôle d'un shunt. Compte tenu de la forte dynamique temporelle de la fuite, il n'est pas nécessaire d'introduire une section résistive de plus forte valeur. Le driver ainsi constitué repose sur deux cartes : une carte mère sur laquelle sont placés le buffer principal et son isolateur de commande, une carte fille intégrant les circuits analogiques de détection de la fuite et la communication isolée avec la carte mère. L'électronique de détection est référencée au plus près de la résistance de grille afin d'éviter une trop forte tension de mode commun et de préserver une basse tension d'alimentation locale des circuits, gage de rapidité et de faible consommation. La conception de cette électronique a été réalisée de manière à pouvoir détecter une fuite de grille bidirectionnelle et ainsi couvrir les deux types de court-circuit principaux, type 1 et type 2. La carte fille intègre également un circuit numérique programmable de type CPLD venant centraliser les informations principales (commande, confirmation du défaut et mise en mémoire, blocage de sécurité, réarmement par superviseur) et appliquer une fenêtre réglable de masquage de l'impulsion de charge de grille à chaque front de commande.

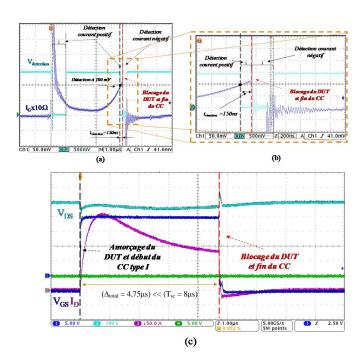

Le fonctionnement de la protection est démontré en Fig. 17, en mode de court-circuit de type 1 sous 600V. La détection de la fuite est réglée à 10mA pour bénéficier d'une marge au bruit conséquente. Cette valeur implique une fenêtre de masquage d'au moins 1µs sur le front de commande ce qui n'a aucun impact sur les performances de la protection puisque celle-ci ne peut pas réagir avant T<sub>sc</sub>/2 (valeur typique). Dans ces conditions, l'ordre de blocage de sécurité est propagé en moins de 150ns pour une protection effective en 4,75µs à ramener à un T<sub>sc</sub> de 8µs pour le composant considéré. Ce résultat a été obtenu sans modification de la résistance de grille, i.e. en utilisant une valeur de  $10\Omega$ , typique pour ce type de calibre en courant. En effet, cette valeur est suffisante pour permettre une mesure fiable et aussi un blocage d'urgence sans mettre en danger le composant au blocage comme l'illustre la Fig. 5c. En Fig. 5b, il est intéressant de souligner qu'au blocage de sécurité, la détection est à nouveau active alors que la fuite de grille est pourtant redescendue en dessous du seuil des 10mA. Ce fonctionnement s'explique par la double détection ±10mA en place sur la carte fille. C'est d'ailleurs grâce à cette détection bidirectionnelle qu'il est possible de traiter le cas du courtcircuit de type 2, exposé dans le paragraphe suivant.

Fig. 16 a) Schéma de principe simplifié du driver incluant un circuit de protection pour la détection du CC, b) intégration en deux cartes (partie driver standard et option de protection).

Fig. 17 Exemple de formes d'ondes en mode de protection de court-circuit de type 1 pour  $V_{\rm ds}=600V,~V_{\rm gs}~+20V/-5V,~R_{\rm g}=10\Omega.$  Délai apparent total de protection du composant  $~4,75\mu s$  pour délai interne sur la détection seule de 150ns:a) fenêtrage et détection de la fuite de grille, b) zoom, c) blocage de sécurité du transistor.

Rappel 1: un court-circuit est dit de type 1 lorsqu'il prend naissance sur le front de commande d'un des deux transistors constituant un bras d'onduleur.

Rappel 2: un court-circuit est dit de type 2 lorsqu'il prend naissance durant la phase de conduction d'un des deux transistors constituant un bras d'onduleur.

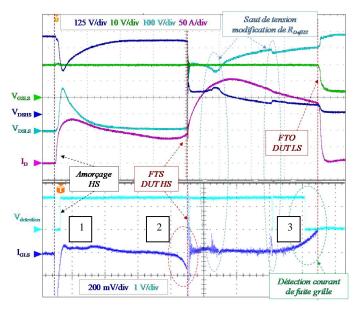

L'évaluation de notre driver passe aussi par l'étude de son comportement sur un court-circuit de type 2. Celle-ci a été menée en configurant le banc de la Fig.1 en bras d'onduleur. Le driver du composant high-side est réglé de manière à polariser une tension de grille plus basse que celle appliquée au composant low-side. Ce dernier est en permanence commandé pour toute la durée de l'essai. Ainsi, en commandant le composant high-side, celui-ci va saturer le premier puis rentrer en défaillance alors que le composant low-side est en régime ohmique préalablement établi. Un court-circuit de type 2 est donc appliqué au composant low-side en acceptant de détruire le composant high-side. La Fig. 18 donne une vue d'ensemble des résultats où, pour des raisons pédagogiques, la protection a été inhibée afin d'observer toutes les séquences en jeu, seul le signal de détection de l'électronique est maintenu visible.

La séquence "1" est la conséquence de l'amorçage du composant high-side : le di/dt contrôlé par son canal provoque un dv/dt ohmique aux bornes du composant homologue low-side. Ce dernier est le siège d'une réinjection de charge par sa capacité grille – drain, visible par un courant de grille négatif. La détection à -10mA vient donc s'activer sur ce composant à même de se bloquer et ainsi de neutraliser le défaut initial.

Fig. 18 Séquences de défaut dans un bras d'onduleur sous  $V_{BUS} = 600V$ : composant high-side commandé à  $V_{GS}$  réduit à 15V en association avec un composant low-side (DUT) sous  $V_{GS}$  20V pour l'application d'un court-circuit de type 2.

On le voit donc sur cet exemple, la présence d'une détection bidirectionnelle dans le contexte d'un bras d'onduleur permet *in fine* une détection apparente en moins de 200ns sans être dépendant de l'inertie de la fuite de grille à T<sub>sc</sub>/2. C'est un avantage essentiel. C'est le détecteur du composant homologue à celui en défaut qui réagira le premier et permettra une mise en sécurité rapide de l'ensemble du bras. La séquence suivante "2" montre le même comportement : la destruction du composant high-side provoque à nouveau un di/dt (très élevé cette fois car limité par l'inductance parasite de la maille seule), provoquant là aussi une réinjection de charge sur le composant low-side puis sa détection. Finalement, la séquence "3" ramène le composant low-side en court-circuit de type 1 avec le même comportement qu'en Fig. 17 où réapparait la fuite de grille inertielle.

#### 6. CONCLUSION

Une modèle électrothermique compact complet est présenté dans cet article de synthèse. Il est représentatif à la fois du comportement et des modes de défaillances propres au Mosfet SiC en régime de court-circuit. Il peut être utilisé ou adapté pour des besoins d'analyse ou des études orientées "système de conversion" dans un environnement de simulation circuit de type LT/PSpice<sup>TM</sup> ou PLECS<sup>TM</sup>. En tirant parti des propriétés singulières de cette technologie de composant, un dispositif de protection original basé sur la détection du niveau de la fuite de grille a été développé avec succès. Cette protection présente des niveaux de performance allant de la microseconde à Tsc/2, selon son mode d'usage. Enfin, nous rappelons que le mode de défaillance "en circuit ouvert", propre à ce type de composant, est une propriété nouvelle qui s'annonce comme très attractive pour la protection native "dernier secours" d'un bras d'onduleur.

Remerciements : ces travaux ont été en partie financés par le projet ANR JCJC HIT-TEMS, SATIE, Cnam, piloté par Denis Labrousse. Jean-Marc Blaquière et Sébastien Vinnac pour la conception et la mise au point du détecteur à fuite de grille.

#### 7. References

- [1] Z. Wang et al., 'Temperature-Dependent Short-Circuit Capability of Silicon Carbide Power MOSFETs', IEEE Trans. Power Electron., vol. 31, no. 2, pp. 1555–1566, Feb. 2016.

- [2] Introduction à la sûreté de fonctionnement de l'onduleur de tension. Modes de défauts principaux et principes de sécurisation, F.Richardeau, Arnaud Gaillard, Techniques de l'Ingénieur, fascicule n°D3179, 10 mai 2017.

- [3] F.Boige, Caractérisation et modélisation électrothermique compacte étendue du MOSFET SiC en régime extrême de fonctionnement incluant ses modes de défaillance. Application à la conception d'une protection intégrée au plus proche du circuit de commande, thèse de doctorat de Toulouse INP, 27 septembre 2019, Lab. LAPLACE, Université de Toulouse, mémoire en ligne: <a href="http://www.theses.fr/2019INPT0084">http://www.theses.fr/2019INPT0084</a>

- [4] F. Boige, F. Richardeau, Gate leakage-current analysis and modelling of planar and trench power SiC MOSFET devices in extreme short-circuit operation, Microelectronics Reliability, Volumes 76–77, 2017, Pages 532-538.

- [5] G. Romano et al., A Comprehensive Study of Short-Circuit Ruggedness of Silicon Carbide Power MOSFETs, in IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 4, no. 3, pp. 978-987, Sept. 2016, doi: 10.1109/JESTPE.2016.2563220.

- [6] F. Boige, F. Richardeau, S. Lefebvre, M. Cousineau, SiC power MOSFET in short-circuit operation: Electro-thermal macro-modelling combining physical and numerical approaches with circuit-type implementation, Mathematics and Computers in Simulation, Volume 158, 2019, Pages 375-386, https://doi.org/10.1016/j.matcom.2018.09.020.

- [7] L. L. Snead, T. Nozawa, Y. Katoh, T.-S. Byun, S. Kondo, and D. A. Petti, 'Handbook of SiC properties for fuel performance modeling', J. Nucl. Mater., vol. 371, no. 1, pp. 329–377, Sep. 2007 https://doi.org/10.1016/j.jnucmat.2007.05.016.

- [8] J. E. Hatch, Aluminum: Properties and Physical Metallurgy. ASM International, 1984.

- [9] A Fayyaz, F. Boige, A Borghese, G Guibaud, V. Chazal, et al.. Aging and failure mechanisms of SiC Power MOSFETs under repetitive shortcircuit pulses of different duration. International Conference on Silicon Carbide and Related Materials 2019, Sep 2019, Kyoto, Japan. (hal-02334396)

- [10] F. Boige, et al, 'Physical origin of the gate current surge during shortcircuit operation of SiC MOSFET', IEEE Electron Device Lett., pp. 1–1, 2019.

- [11] F. Boige, et al, 'Ensure an original and safe "fail-to-open" mode in planar and trench power SiC MOSFET devices in extreme short-circuit operation', Microelectron. Reliab., vol. 88–90, pp. 598–603, 2018.

- [12] P. D. Reigosa, F. Iannuzzo, and L. Ceccarelli, 'Effect of short-circuit stress on the degradation of the SiO2 dielectric in SiC power MOSFETs', Microelectron. Reliab., vol. 88–90, pp. 577–583, Sep. 2018 https://doi.org/10.1016/j.microrel.2018.07.144.

- [13] F. Richardeau, F. Boige, Circuit-type modelling of SiC power Mosfet in short-circuit operation including selective fail-to-open and fail-to-short modes competition, Microelectronics Reliability, Volumes 100–101, 2019, https://doi.org/10.1016/j.microrel.2019.113501.

- [14] Dinh-Lam Dang, Caractérisation, analyse et modélisation du Mosfet de puissance en carbure de silicium, Thèse de doctorat de l'Université de Lorraine, 23 octobre 2019.

- [15] Z. Khatir, S. Lefebvre, and F. Saint-Eve, 'Experimental and numerical investigations on delayed short-circuit failure mode of single chip IGBT devices', Microelectron. Reliab., vol. 47, no. 2, pp. 422–428, Feb. 2007 https://doi.org/10.1016/j.microrel.2006.05.004.

- [16] Z. Wang, X. Shi, L. M. Tolbert, F. Wang, Z. Liang, D. Costinett, and B. J. Blalock, 'Temperature-Dependent Short-Circuit Capability of Silicon Carbide Power MOSFETs', IEEE Trans. Power Electron., vol. 31, no. 2, pp. 1555–1566, Feb. 2016 https://doi.org/10.1109/TPEL.2015.2416358.

- [17] B. J. Baliga, Silicon Carbide Power Devices. World Scientific, 2005.

- [18] L. L. Snead, T. Nozawa, Y. Katoh, T.-S. Byun, S. Kondo, and D. A. Petti, 'Handbook of SiC properties for fuel performance modeling', J. Nucl. Mater., vol. 371, no. 1, pp. 329–377, Sep. 2007 https://doi.org/10.1016/j.jnucmat.2007.05.016.

- [19] N. G. Wright, D. J. Morrison, C. M. Johnson, and A. G. O'Neill, 'Electrothermal Simulation of 4H-SiC Power Devices', Materials Science Forum, 1998. [Online]. Available: https://www.scientific.net/MSF.264-268.917. [Accessed: 27-Jun-2019] https://doi.org/10.4028/www.scientific.net/MSF.264-268.91