# Développement de briques technologiques pour la fabrication de composants MOS diamant : contacts ohmiques et capacités MIS sur diamant de type P

Lya FONTAINE <sup>1</sup>, Karine ISOIRD <sup>1</sup>, Josiane TASSELLI <sup>1</sup>, Patrick AUSTIN <sup>1</sup>, Emmanuel SCHEID <sup>1</sup>, Alain CAZARRE <sup>1</sup>, Riadh ISSAOUI <sup>2</sup>

RESUME -Des contacts ohmiques de très bonne qualité électrique et des capacités MIS fonctionnelles sur diamant de type P sont des briques technologiques fondamentales pour envisager la fabrication de composants MOS diamant. La méthode de caractérisation des contacts ohmiques par TLM circulaire a été validée et des structures de type MIS ont donc été fabriquées sur diamant de type P. Même si des optimisations sont encore nécessaires, les résultats présentés permettent d'envisager la fabrication d'un démonstrateur de type diode P-TMBS (*Trench MOS Barrier Schottky*) en diamant.

Mots-clés—Diamant, MOS, Contacts ohmiques, Capacités MIS

### 1. Introduction

Les performances de l'électronique de puissance en termes de tenues en tensions, de densités de puissance admissibles, de température et de fréquences de fonctionnement étant de plus en plus élevés, des matériaux semi-conducteurs alternatifs au silicium sont étudiés afin de concevoir des composants permettant d'assurer ces exigences. C'est le cas du diamant, semi-conducteur à large bande interdite (Eg = 5,5 eV) aux propriétés prometteuses permettant d'envisager son utilisation pour des application haute tension et à haute température.

De nombreux verrous technologiques restent cependant à lever pour fabriquer des composants de puissance à base de diamant. Si la fabrication de contacts ohmiques sur diamant de type P est maitrisée [1], la résistance spécifique de contact doit encore être améliorée pour minimiser son impact sur les performances électriques. De plus, le dépôt et la maitrise de l'interface entre le diélectrique et le diamant doivent être parfaitement contrôlés pour permettre la fabrication de composants de type MOS. Les études sur les capacités MIS [2] montrent des densités de charges dans la couche diélectrique et à l'interface diamant/diélectrique encore bien trop élevée nécessitant, de fait, d'être réduites .

Dans cet article nous présentons l'étude menée sur les procédés de fabrication de TLM (Transmission Line Model) et cTLM (Circular Transmission Line Model) et des capacités MIS sur diamant de type P.

## 2. ETUDE DES CONTACTS OHMIQUES SUR DIAMANT DE TYPE P

Les contacts ohmiques ont été étudiés à l'aide de deux motifs de tests : les TLM droits et les TLM circulaires (ou cTLM) [3]. Le but de cette étude est de vérifier l'impact de la température de recuit sur la formation de contacts ohmiques et de comparer ces deux motifs sur un même échantillon afin de valider

l'utilisation des cTLM dont les motifs peuvent être intégrés facilement lors de la fabrication des composants.

## 2.1. Réalisation technologique des contacts ohmiques

Une étude approfondie a tout d'abord été menée sur la mise au point d'un procédé de photolithographie adapté aux échantillons diamant qui sont, à l'heure actuelle, de petite taille de l'ordre de quelques mm². Les techniques classiquement utilisées de dépôt de résine photosensible par « spin coating » et d'insolation aux UV à l'aide de machines par projection ne sont plus adaptées pour ces dimensions. En effet, les effets de bord après dépôt conduisent à une surface utile de seulement 50% dans le pire cas avec une faible résolution des motifs obtenus.

Nous avons donc développé la technique de dépôt par « Spray coater ». Des gouttelettes de résine sont vaporisées sur le substrat au travers d'une buse et par vagues successives. On obtient ainsi une surface utile de l'échantillon entre 95% et 100%. La technique alternative choisie pour l'insolation de la résine photosensible est l'écriture directe par faisceau laser, à l'aide de la Dilase 750. Deux types de résine ont été étudiées : la résine positive AZ4999, pour les étapes de gravure et la résine négative NLOF pour les dépôts de métaux par lift-off. Des résolutions de l'ordre du micron ont pu être obtenues. Les travaux menés sont détaillés dans la thèse de Lya Fontaine [4].

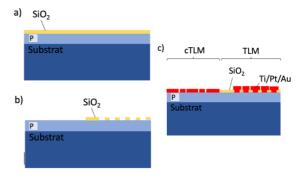

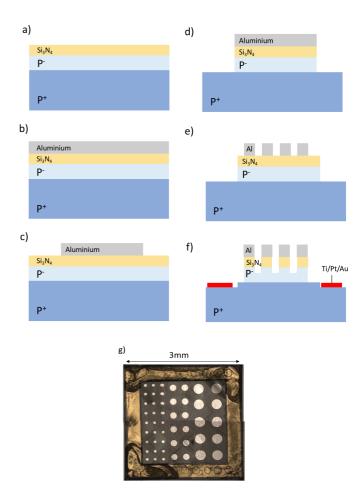

Le procédé de fabrication utilisé est schématisé sur la Fig. 1. Les couches de type P ont été épitaxiées au LSPM sur substrats diamant de 3x3mm<sup>2</sup>. La concentration de Bore est estimée à 1x10<sup>20</sup> at/cm<sup>3</sup> pour une épaisseur de couche d'environ 8µm.

Fig. 1 Vue en coupe schématique des étapes de fabrication des motifs de TLM droits et de cTLM

Une couche de SiO<sub>2</sub> de 200nm est déposée par PECVD (*Plasma Enhanced Chemical Vapour Deposition*). Une première lithographie laser avec la résine AZ4999 permet de créer deux

<sup>&</sup>lt;sup>1</sup> LAAS-CNRS Université de Toulouse, CNRS, UPS, Toulouse, France, <sup>2</sup> LSPM Université Paris 13, Villetaneuse, France

types d'ouvertures dans cette couche (Fig. 1b) par gravure plasma CF<sub>4</sub>/O<sub>2</sub> : l'une correspondant aux dimensions des barres de TLM droits, l'autre à la zone où seront définies les couronnes de cTLM.

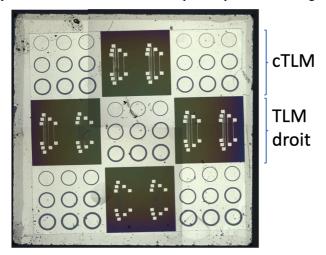

Une deuxième lithographie laser avec la résine NLOF permet ensuite de définir les barres de TLM droits, les plots de reprise de contact et les couronnes de cTLM (Fig. 1c). Le métal est déposé par évaporation thermique (Ti/Pt/Au, 50/50/500nm) et, après le *lift-off*, un recuit thermique est effectué pour former les contacts ohmiques (500°C pour l'échantillon P<sub>1</sub> et à 600°C pour l'échantillon P<sub>2</sub>). Une image optique de l'échantillon P<sub>1</sub> après fabrication des contacts ohmiques est présentée à la Fig. 2.

Fig. 2 Vue au microscope optique de l'échantillon  $P_1$  après fabrication des motifs de TLM droits et de cTLM

# 2.2. Caractérisation électrique des contacts ohmiques

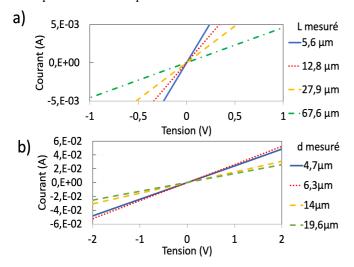

Les courbes I(V) mesurées à température ambiante (Fig. 3) sont linéaires pour les deux types de motifs sur l'échantillons  $P_1$  et impliquent donc que les contacts sont ohmiques. Des résultats identiques sont obtenus pour l'échantillon  $P_2$ .

Fig. 3 Caractéristiques courant/tension obtenues à température ambiante pour l'échantillon P<sub>1</sub> recuit à 500°C : a) pour les motifs de TLM droits, b) pour les motifs de cTLM

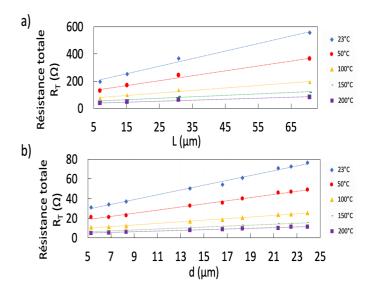

Des mesures ont également été réalisées en fonction de la température jusqu'à 200°C. Nous avons tracé, pour l'échantillon P<sub>1</sub>, la résistance totale entre deux contacts voisins en fonction de la distance L qui les sépare pour les TLM droits (Fig. 4a) ainsi que la résistance totale en fonction de la largeur d de chaque couronne pour les cTLM (Fig. 4b).

Fig. 4 Résistance totale mesurée à différentes températures pour l'échantillon  $P_1$ : a) en fonction de la distance L entre deux contacts voisins pour les TLM droits b) en fonction de la largeur d de chaque couronne pour les cTLM.

A température ambiante, les résistances spécifiques de contact sont alors estimées pour l'échantillon  $P_1$  à  $\rho_{C\,TLM}=3,55~x~10^{-4}~\Omega.cm^2$  (écart type de  $5,3x10^{-5}~\Omega.cm^2$ ) pour les TLM et à  $\rho_{C\,cTLM}=5,05~x~10^{-4}~\Omega.cm^2$  (écart type de  $3,54~x~10^{-4}~\Omega.cm^2$ ) pour les motifs de cTLM. Pour l'échantillon  $P_2$ , la résistance spécifique de contact vaut  $\rho_{C\,TLM}=3,21~x~10^{-4}~\Omega.cm^2$  (écart type de  $1,24x10^{-4}~\Omega.cm^2$ ) pour les motifs de TLM et  $\rho_{C\,cTLM}=6,16~x~10^{-4}~\Omega.cm^2$  (écart type de  $2,77~x~10^{-4}~\Omega.cm^2$ ) pour les motifs de cTLM toujours à température ambiante. Ces valeurs de résistances étant du même ordre de grandeur pour les deux types de motifs, l'utilisation des cTLM pour caractériser les contacts ohmiques peut être validée.

Si l'on considère les mesures effectuées sur tous les motifs pour chaque échantillon, on relève une certaine dispersion des résultats [4]. Plusieurs hypothèses peuvent expliquer ces dispersions comme la non uniformité du dopage de la couche P, des erreurs induites par les techniques de micro-fabrication ainsi que par les méthodes de caractérisations utilisées.

On constate de plus que la résistance de couche modifiée sous le contact  $R_{SK}$  est bien inférieure à la résistance de couche  $R_{SH}$  ( $R_{SK}=33,24~\Omega/\Box$  contre  $R_{SH}=1070,22~\Omega/\Box$  pour l'échantillon  $P_1$  et  $R_{SK}=35,99~\Omega/\Box$  contre  $R_{SH}=685,6~\Omega/\Box$  pour l'échantillon  $P_2$ ). Ceci indique la présence d'une couche alliée de carbure de titane favorisant la formation des contacts ohmiques.

La résistance spécifique de contact diminue quand la température augmente. Pour l'échantillon P1, on a  $\rho_{\text{C TLM}} = 1,11 \times 10^{-4} \ \Omega.\text{cm}^2 \text{ et } \rho_{\text{C cTLM}} = 3 \times 10^{-5} \ \Omega.\text{cm}^2 \text{ à } 200^{\circ}\text{C}.$ L'amélioration des caractéristiques électriques des contacts ohmiques avec la température peut être expliquée par l'effet d'ionisation incomplète des atomes dopants [5]. En effet, dans le diamant à température ambiante, l'énergie thermique n'est pas suffisante pour ioniser complètement tous les atomes accepteurs (à cause de l'énergie d'activation élevée du bore E<sub>a</sub>=0,18eV pour un échantillon dopé à 1x10<sup>20</sup> at/cm<sup>-3</sup>). La concentration de porteurs n'atteint donc pas la concentration d'atomes dopants. L'augmentation de la température va ioniser de plus en plus de dopants et augmenter la concentration de porteurs, et donc diminuer la résistance de couche et améliorer le contact. En effet, à ce niveau de dopage, la mobilité des porteurs est déjà très faible  $(\mu_p = 30 \text{ cm}^2/\text{V.s} [6])$  et ne varie quasiment plus avec la température et ne va donc pas dégrader la conductivité.

L'augmentation de la température de recuit n'a pas amélioré les contacts de façon significative. Les résistances spécifiques de contacts obtenues sont supérieures d'un ordre de grandeur par rapport à celles obtenues dans la littérature [1], [7]. De plus, la dispersion dans les mesures réalisées nous amène à conclure qu'une optimisation du procédé de fabrication semble encore nécessaire. Toutefois, les résultats similaires obtenus sur les deux types de motifs de TLM montrent qu'il est tout à fait pertinent d'utiliser les motifs de cTLM, plus simples à réaliser, pour caractériser les contacts ohmiques sur le diamant de type P.

# 3. REALISATION DE CAPACITES MIS SUR DIAMANT DE TYPE P

Afin d'ouvrir la voie au développement de composants de type MOS diamant, il est nécessaire de maitriser le dépôt de couche diélectrique et l'interface avec le diamant pour pouvoir observer la déplétion caractéristique de l'effet MOS. C'est l'étude que nous avons menée au travers de structures de tests de type capacité MIS.

# 3.1. Réalisation technologique des capacités MIS

Des capacités MIS pseudo-verticales ont été réalisées sur un empilement de type substrat IIb/P<sup>+</sup>/P<sup>-</sup> réalisé au LSPM, d'orientation cristalline (100) et de dimensions 3x3mm². La couche P<sup>+</sup> a une épaisseur d'environ 10μm et un dopage Bore estimé à 1x10²0 at.cm³. La couche P<sup>-</sup> a une épaisseur d'environ 4μm pour un dopage de 1x10¹7 at.cm³. Afin d'analyser la qualité de la surface du diamant avant dépôt du diélectrique, nous avons effectué une étude XPS au CIRIMAT avant et après nettoyage chimique et traitement à l'UV Ozone. Cela a permis de vérifier que tous les contaminants présents en surface de l'échantillon ont été éliminés par le nettoyage et qu'une partie des liaisons pendantes en surface ont été remplacées par des liaisons oxygène lors du traitement à l'UV Ozone afin de limiter la présence de pièges à l'interface diamant/diélectrique [4].

Les étapes de fabrication des capacités MIS pseudoverticales sont présentées à la Fig. 5. Le diélectrique Si<sub>3</sub>N<sub>4</sub> (30nm) est déposé par LPCVD (*Low Pressure Chemical Vapour Deposition*) à 700°C suivi, dès la sortie du bâti, par un dépôt de 700nm d'aluminium afin d'éviter toute contamination de sa surface (Fig. 5b). Une première photolithographie est effectuée avec une résine positive afin de délimiter par gravure chimique un carré central d'aluminium qui sert de masque pour la gravure RIE de la couche de Si<sub>3</sub>N<sub>4</sub> suivie de la gravure du diamant de type P<sup>-</sup> (recette décrite par [8]), afin d'atteindre la couche P<sup>+</sup> (Fig. 5d).

Une deuxième photolithographie permet de définir les contacts sur le diélectrique Des capacités de différents diamètres ( $100\mu m$ ,  $200\mu m$  et  $300\mu m$ ) sont ainsi obtenues. La dernière étape de photolithographie avec de la résine négative consiste à réaliser le contact ohmique sur la couche  $P^+$  (en y incluant un motif de cTLM afin de pouvoir caractériser ces contacts par la suite). Un empilement de Ti/Pt/Au (50/50/500nm) est donc déposé par évaporation thermique (Fig. 5f). Ces contacts ont été recuits à  $450^{\circ}$ C pendant une heure sous atmosphère d'azote pour permettre la formation du contact ohmique. La température de recuit habituelle de  $500^{\circ}$ C a été abaissée à  $450^{\circ}$ C afin de limiter la diffusion thermique de l'aluminium dans la couche de diélectrique.

La Fig. 5g montre une vue au microscope optique des structures MIS réalisées.

Fig. 5 Etapes de fabrication des capacités MIS pseudo-verticales a) Dépôt de 30nm de  $\mathrm{Si}_3\mathrm{N}_4$ ; b) Dépôt de 500nm d'aluminium ; c) Gravure de l'aluminium ; d) Gravure plasma du  $\mathrm{Si}_3\mathrm{N}_4$  et de la couche  $\mathrm{P}^*$ ; e) Gravure de l'aluminium pour définir les contacts diélectriques ; f) Gravure supplémentaire du diamant pour atteindre la couche  $\mathrm{P}^*$  et Dépôt par évaporation des contacts  $\mathrm{Ti}/\mathrm{Pt}/\mathrm{Au}$  (50/50/500nm) ; g) Photo de l'échantillon en fin de procédé.

# 3.2. Caractérisation électrique des capacités MIS

Des mesures I(V) ont été réalisées par mesures 4 pointes sur les motifs cTLM : les courbes obtenues sont linéaires, indiquant que le contact sur la couche  $P^+$  est bien ohmique. La résistance spécifique de contact extraite à partir de ces mesures vaut  $\rho_C=1.7 \times 10^{-4} \; \Omega.\text{cm}^2.$  Cette valeur est suffisante pour que, lors des mesures C(V), il n'y ait pas de chute de potentiel importante due aux contacts ohmiques. Cette faible valeur nous confirme également que l'on peut ici se placer dans l'hypothèse où la résistance série est négligeable.

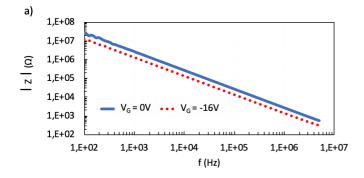

Un balayage en fréquence a été réalisé à l'aide d'une station sous pointes Signatone CM210 et d'un analyseur d'impédance Agilent 4294a. La Fig. 6 présente les variations de module et d'argument de l'impédance pour des capacités de 300µm de diamètre à une tension de polarisation de 0V, et -16V (en régime d'accumulation), pour une amplitude du signal ac de 30mV. La mesure de phase à -90° montre le caractère purement capacitif des structures réalisées sur un large bande de fréquence allant de 1kHz à 100kHz. L'influence de la résistivité de la couche semiconductrice est donc bien négligeable sur cette bande de fréquence. Un modèle à deux éléments (capacité et résistance représentant les fuites en parallèle) est donc utilisé ici comme schéma électrique équivalent pour extraire, à partir des mesures, l'évolution de C en fonction de la tension.

Fig. 6 a) Module et b) argument de l'impédance mesurée en fonction de la fréquence pour les capacités de  $300\mu m$  de diamètre à température ambiante

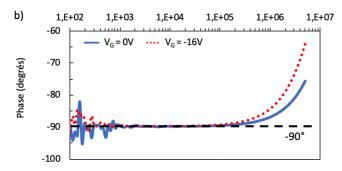

La Fig. 7 présente les mesures C(V) réalisées pour des tensions de polarisation de -15V à +30V. La caractéristique obtenue permet d'identifier les différents régimes d'accumulation, de déplétion et de déplétion profonde.

Fig. 7 Caractéristiques C(V) mesurées à  $10 \mathrm{kHz}$  à température ambiante comparées à la courbe théorique

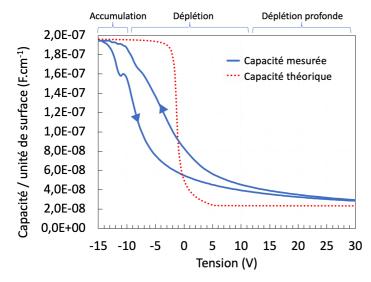

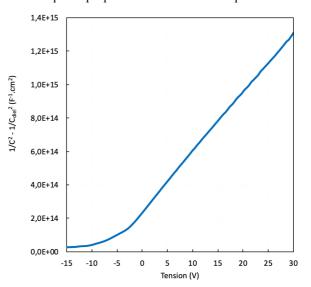

Les variations de  $\frac{1}{c^2} - \frac{1}{c_{diel}^2}$  avec V sont tracées pour une capacité de 300µm de diamètre à température ambiante (voir Fig. 8). La tension de bande plate au second ordre est alors extraite et vaut  $V_{BP2} = -6,6V$ . Cela correspond au décalage de la tension de seuil dû aux charges présentes dans le diélectrique et à l'interface diélectrique/semiconducteur. A partir de cette valeur, il est possible de calculer la densité de charges fixes dans la couche diélectrique à partir de l'équation suivante [9] :

$$N_f = \frac{C_{diel}(\phi_{MS} - V_{BP2})}{qS}$$

avec  $\phi_{MS} = \phi_M - \phi_{SC}$  la différence de travaux de sortie entre le métal et le semiconducteur qui vaut 3,67 eV. On calcule ici

$N_f$  = 1,23 x10<sup>13</sup> cm<sup>-2</sup> soit 3,67 x 10<sup>18</sup> cm<sup>-3</sup> pour une épaisseur de diélectrique de 33,5nm. Cette valeur est très élevée et du même ordre de grandeur que celle obtenue dans la littérature [2] avec une couche d'Al<sub>2</sub>O<sub>3</sub>, confirmant ainsi que de nombreuses charges fixes piégées sont présentes dans le volume de la couche diélectrique impliquant un courant de fuite par effet tunnel.

Fig. 8 Caractéristique  $\frac{1}{c^2} - \frac{1}{c_{diel}^2}$  en fonction de la tension de polarisation pour une capacité de 300µm de diamètre à température ambiante en descente à  $10 \mathrm{kHz}$

La méthode de la conductance [10] est ensuite appliquée pour déterminer la densité de pièges à l'interface D<sub>it</sub> pour cet échantillon. La densité de pièges ramenée à l'interface est supérieure à 10<sup>14</sup> cm<sup>-2</sup>. Cette valeur très élevée indique clairement que l'interface diélectrique/diamant n'est pas électroniquement stable, altérant ainsi fortement les performances électriques des capacités.

Ces pièges peuvent provenir de différentes sources. Les charges fixes et mobiles dans le diélectrique peuvent être dues au procédé de dépôt utilisé. Il est par exemple possible qu'il y ait eu une migration des atomes d'aluminium servant de contact métallique lors du recuit de l'échantillon, ou une contamination durant le dépôt en lui-même. En effet, les rampes de température adaptées qui ont été utilisées impliquent que le temps de dépôt est de plusieurs heures, ce qui augmente la probabilité de contamination. Les pièges à l'interface peuvent correspondre à des espèces contaminantes ou à des liaisons C-H pendantes encore présentes après le traitement de surface.

Il semble donc primordial d'améliorer le procédé de fabrication de ces capacités avant d'envisager la fabrication de MOSFET en diamant. Nous avons envisagé plusieurs voies possibles. Un traitement de surface adapté pourrait être mis en place pour éviter le changement de bâti entre le traitement chimique et le dépôt du diélectrique de grille, afin de limiter encore davantage les risques de contamination.

Un dépôt d'Al<sub>2</sub>O<sub>3</sub> par ALD (*Atomic Layer Deposition*) pourrait permettre de déposer un diélectrique avec une constante diélectrique plus élevée afin d'augmenter la capacité de la grille sans effet de fuite. Il serait également possible avec cette technique d'analyser la qualité du traitement de surface effectué sur les échantillons avant dépôt de diélectrique de façon plus précise que les analyses XPS réalisées. En effet, même si une forte augmentation de l'oxygène présent en surface avait été observée, il était impossible de quantifier la quantité d'hydrogène restant. Dans le cas d'un dépôt par ALD, la

présence de liaison hydrogène en surface modifie la cinétique de dépôt de l'Al<sub>2</sub>O<sub>3</sub>, ce qui permettrait de mener une étude pour connaître le taux de liaisons C-H toujours présentes après ce traitement de surface.

Une injection de porteurs de la couche semiconductrice vers le diélectrique a pu être observée, ce qui favorise notamment les courants de fuite par effet tunnel. Il pourrait alors être envisagé de déposer un autre diélectrique comme barrière afin d'éviter ce phénomène.

# 4. CONCLUSION

Les travaux présentés ont porté sur le développement de briques technologiques comme les contacts ohmiques de type P et les capacités MIS. Nous avons montré que la technique de caractérisation des contacts ohmiques par TLM circulaires, plus simples à réaliser, était viable. Des capacités MIS diamant fonctionnelles ont été fabriquées avec du Si<sub>3</sub>N<sub>4</sub> comme diélectrique. Une capacité en accumulation de 200nF/cm² a été mesurée en accord avec la théorie pour cette couche diélectrique. Cependant, l'amélioration des contacts ohmiques sur diamant de type P et la limitation des charges dans le diélectrique des capacités MIS sont encore nécessaires pour permettre la fabrication de ces composants complexes.

Les résultats obtenus sont encourageants et permettent dès à présent d'envisager la fabrication de composants MOS de puissance comme les diodes TMBS (*Trench MOS Barrier Schottky*) en diamant de type P.

# 5. REMERCIEMENTS

Ce travail est soutenu par l'Agence Nationale de la Recherche ANR à travers le projet MOVeToDIAM : ANR-17-CE05-0019-02 et par la plateforme de micro et nanotechnologies LAAS-CNRS, membre du réseau français RENATECH.

Les auteurs remercient Nicolas MAURAN, responsable de la plateforme de caractérisation du LAAS-CNRS, pour son aide précieuse, Éric IMBERNON, Adrian LABORDE et Pierre-François CALMON pour leur soutien technique dans la mise en place du procédé de fabrication des composants ainsi que Jérôme ESVAN du CIRIMAT pour les mesures XPS.

### 6. References

- [1] D. F. G. Civrac, « Vers la réalisation de composants haute tension, forte puissance sur diamant CVD. Développement des technologies associées. », 2009.

- [2] A. Marechal, « Metal-oxide-semiconductor capacitor for diamond transistor: simulation, fabrication and electrical analysis », Theses, Université Grenoble Alpes, 2015.

- [3] L. Fontaine, K. Isoird, J. Tasselli, A. Cazarré, P. Austin, et A. Laborde, « Développement de briques technologiques pour la réalisation de composants de puissance sur diamant », p. 8, 2019.

- [4] L. Fontaine, « Développement de briques technologiques pour la fabrication de composants de puissance MOS sur diamant », phdthesis, Université Toulouse 3 Paul Sabatier (UT3 Paul Sabatier), 2020.

- [5] S. J. Rashid *et al.*, «Numerical Parameterization of Chemical-Vapor-Deposited (CVD) Single-Crystal Diamond for Device Simulation and Analysis », *IEEE Trans. Electron Devices*, vol. 55, no 10, p. 2744-2756, 2008, doi: 10.1109/TED.2008.2003225.

- [6] J. Pernot *et al.*, «Hall hole mobility in boron-doped homoepitaxial diamond», *Phys. Rev. B Condens. Matter Mater. Phys.*, vol. 81, n° 20, p. 205203, mai 2010, doi: 10.1103/PhysRevB.81.205203.

- [7] Y. Chen, M. Ogura, S. Yamasaki, et H. Okushi, «Ohmic contacts on p-type homoepitaxial diamond and their thermal stability », *Semicond. Sci. Technol.*, vol. 20, nº 8, p. 860-863, août 2005, doi: 10.1088/0268-1242/20/8/041.

- [8] F. Thion, « Conception de protections périphériques applicables aux diodes Schottky réalisées sur diamant monocristallin. », 2010.

- [9] D. Schroder, « Oxide and Interface Trapped Charges, Oxide Thickness », 2005, p. 319-387.

- [10]E. Nicollian and J. Brews, MOS physics and technology. Wiley-Interscience, 1982.